加法器设计(二)串行加法器(Verilog)

<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

全加器

module fulladder(a,b,cy_in,sum,cy_out);

input a,b,cy_in;

output sum,cy_out;

assign sum="a"^b^cy_in;

assign cy_out=(a&b)|(a&cy_in)|(b&cy_in);

endmodule

4位加法器

module add4bit(a, b, ci, s,ovf);

input[3:0] a;

input[3:0] b;

input ci;

output[3:0] s;

output ovf;

wire [2:0] cy;

fulladder fulladder1 (a[0],b[0], ci,s[0],cy[0]);

fulladder fulladder2 (a[1],b[1],cy[0],s[1],cy[1]);

fulladder fulladder3 (a[2],b[2],cy[1],s[2],cy[2]);

fulladder fulladder4 (a[3],b[3],cy[2],s[3],ovf );

endmodule

4位加法器顶层模块

`timescale 1ns / 1ps

module add4bit_test_v;

// Inputs

reg [3:0] a;

reg [3:0] b;

reg ci;

// Outputs

wire [3:0] s;

wire ovf;

// Instantiate the Unit Under Test (UUT)

add4bit uut (

.a(a),

.b(b),

.ci(ci),

.s(s),

.ovf(ovf)

);

initial begin

// Initialize Inputs

a = 0;

b = 0;

ci = 0;

// Wait 100 ns for global reset to finish

#100;

a = 4'b1100;

b = 4'b1010;

ci = 1;

// Wait 100 ns for global reset to finish

#100;

a = 4'b1010;

b = 4'b0011;

ci = 1;

// Wait 200 ns for global reset to finish

#200;

a = 4'b1011;

b = 4'b1001;

ci = 0;

end

endmodule

行为仿真(Behavioral Simulator)结果

可以看到仿真结果实现了全加器的功能。

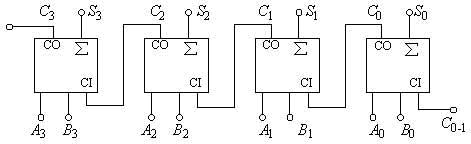

综合的RTL Schematic

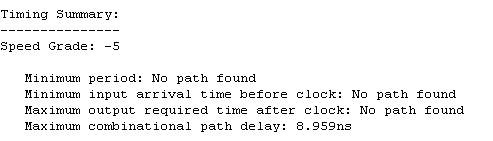

综合可以看到path delay为8.959ns

Post-Place & Route Simulator就可以看到在器件上的延迟了(XC3S500E-5)

四位全加器工程文件:https://static.assets-stash.eet-china.com/album/old-resources/2009/2/11/e118e98c-0b5a-4f1a-9833-7a76dd16484e.rar

/5

/5

文章评论(0条评论)

登录后参与讨论