ISE管脚约束设置参数详解<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

在ISE中,打开User Constraints中的Assign Package Pins就可以对设定的管脚进行约束。

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

打开了Xilinx PACK-[Design Object List-I/O Pin]

其中参数设置如下

I/O Name ——IO管脚名称,对应于module里输入输出管脚。

I/O Direction——设定输入(Input)还是输出(Output)管脚。

Loc——位于芯片的位置。

Bank——管脚位于的Bank块,当指定了Loc后,bank也就确定了。

FROM:Spartan-3E FPGA 系列数据手册 P19

I/O Std.——I/O管脚的电平标准。

每个bank都可以随意设置为该器件支持的电平标准,不同的电平标准在一个bank中要注意它们的电平要一致,比如都为3.3v,电平可以为LVTTL、LVCOMS33。

From:Spartan-3E FPGA 系列数据手册 P16~17

///////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

下面介绍一下常见逻辑电平标准

现在常用的电平标准有TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPECL、RS232、RS485等,还有一些速度比较高的 LVDS、GTL、PGTL、CML、HSTL、SSTL等。下面简单介绍一下各自的供电电源、电平标准以及使用注意事项。

TTL:Transistor-Transistor Logic 三极管结构。

Vcc:5V;VOH>=2.4V;VOL<=0.5V;VIH>=2V;VIL<=0.8V。

因为2.4V与5V之间还有很大空闲,对改善噪声容限并没什么好处,又会白白增大系统功耗,还会影响速度。所以后来就把一部分“砍”掉了。也就是后面的LVTTL。

LVTTL又分3.3V、2.5V以及更低电压的LVTTL(Low Voltage TTL)。

3.3V LVTTL:

Vcc:3.3V;VOH>=2.4V;VOL<=0.4V;VIH>=2V;VIL<=0.8V。

2.5V LVTTL:

Vcc:2.5V;VOH>=2.0V;VOL<=0.2V;VIH>=1.7V;VIL<=0.7V。

更低的LVTTL不常用就先不讲了。多用在处理器等高速芯片,使用时查看芯片手册就OK了。

TTL使用注意:

TTL电平一般过冲都会比较严重,可能在始端串22欧或33欧电阻; TTL电平输入脚悬空时是内部认为是高电平。要下拉的话应用1k以下电阻下拉。TTL输出不能驱动CMOS输入。

CMOS:Complementary Metal Oxide Semiconductor??PMOS+NMOS。

Vcc:5V;VOH>=4.45V;VOL<=0.5V;VIH>=3.5V;VIL<=1.5V。

相对TTL有了更大的噪声容限,输入阻抗远大于TTL输入阻抗。对应3.3V LVTTL,出现了LVCMOS,可以与3.3V的LVTTL直接相互驱动。

3.3V LVCMOS:

Vcc:3.3V;VOH>=3.2V;VOL<=0.1V;VIH>=2.0V;VIL<=0.7V。

2.5V LVCMOS:

Vcc:2.5V;VOH>=2V;VOL<=0.1V;VIH>=1.7V;VIL<=0.7V。

CMOS使用注意:

CMOS结构内部寄生有可控硅结构,当输入或输入管脚高于VCC一定值(比如一些芯片是0.7V)时,电流足够大的话,可能引起闩锁效应,导致芯片的烧毁。

ECL:Emitter Coupled Logic 发射极耦合逻辑电路(差分结构)

Vcc=0V;Vee:-5.2V;VOH=-0.88V;VOL=-1.72V;VIH=-1.24V;VIL=-1.36V。

速度快,驱动能力强,噪声小,很容易达到几百M的应用。但是功耗大,需要负电源。为简化电源,出现了PECL(ECL结构,改用正电压供电)和LVPECL。

PECL:Pseudo/Positive ECL

Vcc=5V;VOH=4.12V;VOL=3.28V;VIH=3.78V;VIL=3.64V

LVPELC:Low Voltage PECL

Vcc=3.3V;VOH=2.42V;VOL=1.58V;VIH=2.06V;VIL=1.94V

ECL、 PECL、LVPECL使用注意:

不同电平不能直接驱动。中间可用交流耦合、电阻网络或专用芯片进行转换。以上三种均为射随输出结构,必须有电阻拉到一个直流偏置电压。(如多用于时钟的LVPECL:直流匹配时用130欧上拉,同时用82欧下拉;交流匹配时用82欧上拉,同时用130欧下拉。但两种方式工作后直流电平都在1.95V左右。)

前面的电平标准摆幅都比较大,为降低电磁辐射,同时提高开关速度又推出LVDS电平标准。

LVDS:Low Voltage Differential Signaling

差分对输入输出,内部有一个恒流源3.5-4mA,在差分线上改变方向来表示0和1。通过外部的100欧匹配电阻(并在差分线上靠近接收端)转换为±350mV的差分电平。

LVDS使用注意:

可以达到<?xml:namespace prefix = st1 ns = "urn:schemas-microsoft-com:office:smarttags" />600M以上,PCB要求较高,差分线要求严格等长,差最好不超过10mil(0.25mm)。100欧电阻离接收端距离不能超过500mil,最好控制在300mil以内。

下面的电平用的可能不是很多,篇幅关系,只简单做一下介绍。如果感兴趣的话可以联系我。

CML:是内部做好匹配的一种电路,不需再进行匹配。三极管结构,也是差分线,速度能达到3G以上。只能点对点传输。

GTL:类似CMOS的一种结构,输入为比较器结构,比较器一端接参考电平,另一端接输入信号。1.2V电源供电。

Vcc=1.2V;VOH>=1.1V;VOL<=0.4V;VIH>=0.85V;VIL<=0.75V

PGTL/GTL+:

Vcc=1.5V;VOH>=1.4V;VOL<=0.46V;VIH>=1.2V;VIL<=0.8V

HSTL是主要用于QDR存储器的一种电平标准:一般有V¬CCIO=1.8V和V¬¬CCIO= 1.5V。和上面的GTL相似,输入为输入为比较器结构,比较器一端接参考电平(VCCIO/2),另一端接输入信号。对参考电平要求比较高(1%精度)。

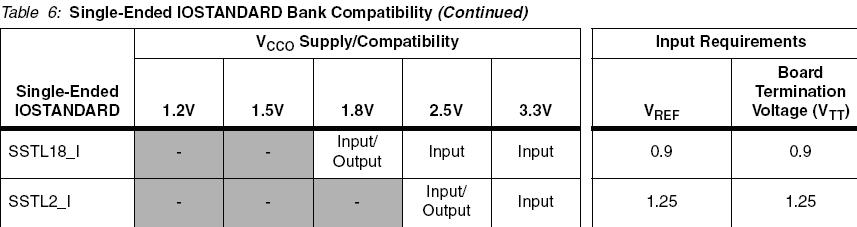

SSTL主要用于DDR存储器。和HSTL基本相同。V¬¬CCIO=2.5V,输入为输入为比较器结构,比较器一端接参考电平1.25V,另一端接输入信号。对参考电平要求比较高(1%精度)。

HSTL和SSTL大多用在300M以下。

RS232和RS485基本和大家比较熟了,只简单提一下:

RS232采用±12-15V供电,我们电脑后面的串口即为RS232标准。+12V表示0,-12V表示1。可以用MAX3232等专用芯片转换,也可以用两个三极管加一些外围电路进行反相和电压匹配。

RS485是一种差分结构,相对RS232有更高的抗干扰能力。传输距离可以达到上千米

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

Drive Str.——I/O管脚的驱动电流。

逻辑电平大小与输出电流强度大小的关系:

From:Spartan-3E FPGA 系列数据手册 P19

Termination——终端结构(电阻上拉/电阻下拉/悬空)。

PULLDOWN和PULLUP原语

数字电路有三种状态:高电平、低电平、和高阻状态。有些应用场合不希望出现高阻状态,可以通过上拉电阻或下拉电阻的方式使其处于稳定状态,如图所示。FPGA的I/O端口,可以通过外接电阻上下拉,也可以在芯片内部,通过配置完成上下拉。

上拉电阻是用来解决总线驱动能力不足时提供电流的;

而下拉电阻是用来吸收电流;

通过FPGA内部配置完成上下拉,能有效节约电路板面积,是设计的首选方案。

上、下拉电路示意图

上、下拉的原语分别为PULLUP和PULLDOWN。

1)PULLUP原语的例化代码

// PULLUP: 上拉原语(I/O Buffer Weak Pull-up)

// 适用芯片:所有芯片

// Xilinx HDL库向导版本,ISE 9.1

PULLUP PULLUP_inst (

.O(O),

//上拉输出,需要直接连接到设计的顶层模块端口上);

// 结束PULLUP模块的例化过程

2)PULLDOWN原语的例化代码

// PULLDOWN:下拉原语( I/O Buffer Weak Pull-down)

// 适用芯片:所有芯片

// Xilinx HDL库向导版本,ISE 9.1

PULLDOWN PULLDOWN_inst (

.O(O),

// 下拉输出,需要直接连接到设计的顶层模块端口上

);

// 结束PULLDOWN模块的例化过程

(FROM: FPGA开发实用教程 第4节 Xilinx公司原语的使用方法

http://www.eefocus.com/article/08-03/37457s.html )

From:Spartan-3E FPGA 系列数据手册 P18

当选择Keeper(悬空)的选项时,使总线悬浮而没有驱动电流,所有驱动翻转后保持上一个逻辑电平。

Slew——Slew Rate。信号的转换速率,可以理解为信号在某一点的斜率。

它不是只针对时钟信号说的;诸如放大器的slew rate就是一个很重要的参数;而在数字电路里,它可能更常用于描述芯片输入信号的变化率。

在Xilinx的设计环境中,可以将输出信号的Slew rate设置成FAST或SLOW。当设置成FAST时,提高了信号变化的斜率,从而提高了信号的转换速率,但同时使脉冲信号的振铃增大。因此,除非万不得已,不要将输出信号的Slew rate设成FAST。

skew选fast,IO转化时快,但电流大,功耗大。

skew选slow,IO转化慢,但功耗小。^: Y! P: v/ W* ~" o$ h

查看器件的DC AC Switching特性手册有详细说明。

默认设置

IOSTANDARD=LVCMOS25

SLEW=SLOW

DRIVE=12

Delay——输入延时。加入延时可以减缓上升速度。BOTH 、 IBUF 、 IFD 、NONE这四个备选项

IFD——Registered inputs

可编程的混合输入延迟单元:

From:Spartan-3E FPGA 系列数据手册 P12

Diff. Type

参考资料:

1) LVTTL与LVCMOS区别

http://nylzhaowei.blog.163.com/blog/static/14303922007324104723589

2) FPGA开发实用教程 第4节 Xilinx公司原语的使用方法

http://www.eefocus.com/article/08-03/37457s.html

3)riple's Blog:Stay hungry. Stay foolish.

这篇文章介绍了 slew rate的选择与EMI的关系

4) 几种接口的标准电平定义

http://bbs.weeqoo.com/bbsdetail-32425-8.html

5)电子工程专辑网站论坛PCB设计技术问答精粹(2)-EMI/EMC设计

http://www.pcbfans.cn/article/3d/5390$2.html

6)Xilinx FPGA如何使用LVDS

http://www.61eda.com/Services/help/Xilinx/200803/1225.html /4

/4

文章评论(0条评论)

登录后参与讨论