STM32的体系结构<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

AMMB片上总线是由ARM公司推出的。

AMBA规范主要包括了AHB(Advanced High performance Bus)系统总线

APB(Advanced Peripheral Bus) 外围总线

AHB主要用于高性能模块(如CPU、DMA和DSP等)之间的连接。

APB主要用于低带宽的周边外设之间的连接。

AHB总线和APB总线通过APB桥来连接。

APB 桥既是APB总线上唯一的主模块,也是AHB系统总线上的从模块。其主要功能是锁存来自AHB系统总线的地址、数据和控制信号,并提供二级译码以产生APB外围设备的选择信号,从而实现AHB协议到APB协议的转换。

在STM32中

? 连接在APB1(低速外设)上的设备有:

电源接口、备份接口、CAN、USB、I<?xml:namespace prefix = st1 ns = "urn:schemas-microsoft-com:office:smarttags" />2C1、I2C2、UART2、UART3、SPI2、窗口看门狗、Timer2、Timer3、Timer4。

? 连接在APB2(高速外设)上的设备有:GPIO_A-E、USART1、ADC1、ADC2、ADC3、TIM1、TIM8、SPI1、ALL。

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

STM32F10x体系架构

STM32F10x体系架构

参考资料:

1) STM32之时钟树笔记 -- joyboy's Blog

http://blog.ednchina.com/joyboy/192898/message.aspx

2) STM32F103x6 STM32F103x8 STM32F103xB DataSheet

附:

AMBA、AHB、APB总线简介 - Embedded Paper - 学习~~~~

http://blog.chinaunix.net/u2/60314/showart_576112.html

AMBA、AHB、APB总线简介

AMBA简介

随着深亚微米工艺技术日益成熟,集成电路芯片的规模越来越大。数字IC从基于时序驱动的设计方法,发展到基于IP复用的设计方法,并在SOC设计中得到了广泛应用。在基于IP复用的SoC设计中,片上总线设计是最关键的问题。为此,业界出现了很多片上总线标准。其中,由ARM公司推出的AMBA片上总线受到了广大IP开发商和SoC系统集成者的青睐,已成为一种流行的工业标准片上结构。AMBA规范主要包括了AHB(Advanced High performance Bus)系统总线和APB(Advanced Peripheral Bus)外围总线。

AMBA片上总线

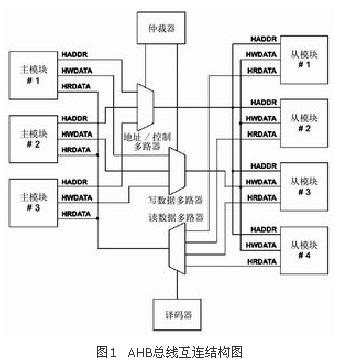

AMBA 2.0规范包括四个部分:AHB、ASB、APB和Test Methodology。AHB的相互连接采用了传统的带有主模块和从模块的共享总线,接口与互连功能分离,这对芯片上模块之间的互连具有重要意义。AMBA已不仅是一种总线,更是一种带有接口模块的互连体系。下面将简要介绍比较重要的AHB和APB总线。

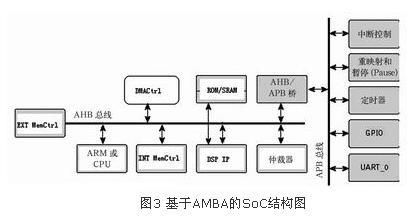

基于AMBA的片上系统

一个典型的基于AMBA总线的系统框图如图3所示。

大多数挂在总线上的模块(包括处理器)只是单一属性的功能模块:主模块或者从模块。主模块是向从模块发出读写操作的模块,如CPU,DSP等;从模块是接受命令并做出反应的模块,如片上的RAM,AHB/APB 桥等。另外,还有一些模块同时具有两种属性,例如直接存储器存取(DMA)在被编程时是从模块,但在系统读传输数据时必须是主模块。如果总线上存在多个主模块,就需要仲裁器来决定如何控制各种主模块对总线的访问。虽然仲裁规范是AMBA总线规范中的一部分,但具体使用的算法由RTL设计工程师决定,其中两个最常用的算法是固定优先级算法和循环制算法。AHB总线上最多可以有16个主模块和任意多个从模块,如果主模块数目大于16,则需再加一层结构(具体参阅ARM公司推出的Multi-layer AHB规范)。APB 桥既是APB总线上唯一的主模块,也是AHB系统总线上的从模块。其主要功能是锁存来自AHB系统总线的地址、数据和控制信号,并提供二级译码以产生APB外围设备的选择信号,从而实现AHB协议到APB协议的转换。

AHB简介

AHB主要用于高性能模块(如CPU、DMA和DSP等)之间的连接,作为SoC的片上系统总线,它包括以下一些特性:单个时钟边沿操作;非三态的实现方式;支持突发传输;支持分段传输;支持多个主控制器;可配置32位~128位总线宽度;支持字节、半字节和字的传输。AHB 系统由主模块、从模块和基础结构(Infrastructure)3部分组成,整个AHB总线上的传输都由主模块发出,由从模块负责回应。基础结构则由仲裁器(arbiter)、主模块到从模块的多路器、从模块到主模块的多路器、译码器(decoder)、虚拟从模块(dummy Slave)、虚拟主模块(dummy Master)所组成。其互连结构如图1所示。

APB简介

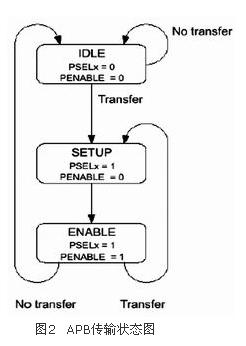

APB主要用于低带宽的周边外设之间的连接,例如UART、1284等,它的总线架构不像AHB支持多个主模块,在APB里面唯一的主模块就是APB 桥。其特性包括:两个时钟周期传输;无需等待周期和回应信号;控制逻辑简单,只有四个控制信号。APB上的传输可以用如图2所示的状态图来说明。

1)系统初始化为IDLE状态,此时没有传输操作,也没有选中任何从模块。

2)当有传输要进行时,PSELx=1,PENABLE=0,系统进入SETUP状态,并只会在SETUP 状态停留一个周期。当PCLK的下一个上升沿时到来时,系统进入ENABLE 状态。

3)系统进入ENABLE状态时,维持之前在SETUP 状态的PADDR、PSEL、PWRITE不变,并将PENABLE置为1。传输也只会在ENABLE状态维持一个周期,在经过SETUP与ENABLE状态之后就已完成。之后如果没有传输要进行,就进入IDLE状态等待;如果有连续的传输,则进入SETUP状态。

/5

/5

用户1466950 2010-4-24 18:30