最近要做一个通信收发系统项目,以前对收发器的射频前段关注的比较多,而对基带部分的信号处理一直没有仔细研究。因此,正好借这个项目,熟悉整个基带部分的信号处理流程。

基带部分主要包括以下几个主要部分:信源编码,信道编码(分组码,卷积码,Turbo码,低密度校验码LDPC等),交织,信号调制(BPSK,QPSK,8PSK,16QAM,64QAM等),OFDM调制,DA变换。

一、基本原理

本文主要关注信号调制的原理和FPGA具体实现。信号调制主要是对信号进行星座映射,一串二进制数据进过星座映射,生成一路I信号和一路Q信号,如下图所示。

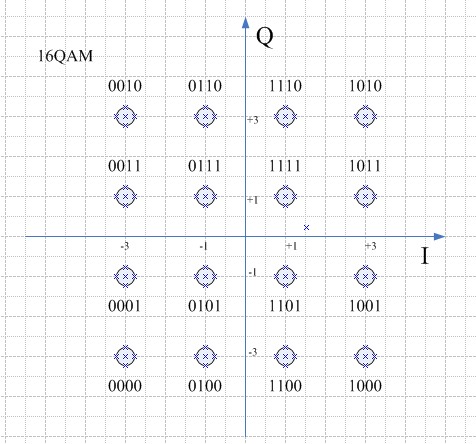

下面以16QAM为例说明星座映射的过程。16QAM中每4个bit对应一路I信号和一路Q信号,因此首先要将串行输入的四个bit数据转换成并行的4bit数据,根据这4bit并行数据选取出其对应的I信号和Q信号,具体映射图如下所示。

上图采用格雷码映射,即星座图上相邻星座对应的编码只有1bit差异,这样在相同的误码率情况下可以得到最小的误比特率。比如输入二进制数据为1001,则输出为3+1i(复数),即I路输出3(十进制),Q路输出1。不过在实际编码中用间距比较大的十进制数据来表示IQ信号,以提高噪声容限。比如用-97(1110011111),96(0001100000),-33(1111011111),32(0000100000)代替-3,3,-1,1,即1001输入时,I信号输出为0001100000,Q信号输出为0000100000。

二、FPGA实现

串变变换模块的实现:

data_in:串行数据输入,data_out:4位并行数据输出。

module(input clk,input data_in,input reset,output[3:0] data_out);

reg[1:0] cnt;

reg[3:0] data_temp;

reg[3:0] data_out;

always @(posedge clk)

begin

if(!reset)

cnt<=2'b00;

else

cnt<=cnt+1;

end

end

always @(posedge clk)

begin

if(!reset)

data_temp <= 4'b00;

else

data_temp<={data_temp[2:0],data_in};

end

always @(posedge clk)

begin

if(cnt==2'b11)

data_out<=data_temp;

else

data_out<=data_out;

end

endmodule

星座映射的实现(关键模块):

case(data_out)

4'b0000:

begin

I<=2'b1110011111;

Q<=2'b1110011111;

end

4'b0001:

begin

I<=2'b1110011111;

Q<=2'b1111011111;

end

......(省略)

三、后续模块

为了使IQ输出的符号速率和后续器件的输入符号速率相匹配,需要在IQ后进行内插,比如IQ输出符号速率为128KBaud,而后续模块输入符号速度要求1024KBaud,则内插倍数位1024/128=8,即在每个IQ符号后内插7个0符号,内插后会产生7个高频镜像分量,在接收时采用低通滤波滤除。另外为了抑制信号带外辐射,还需要添加成型滤波器。

参考文献:

1、OFDM基带数据传输系统及其FPGA设计与实现研究(下载)

2、基于软件无线电的16QAM调制解调器设计与FPGA实现(下载)

/1

/1

文章评论(0条评论)

登录后参与讨论