在混合电路设计中,数字信号的上升下降斜率带来的电磁干扰对模拟信号影响很大,因此在满足要求的情况下,应该尽量降低系统工作频率和脉冲的上升下降斜率。在Quartus中可以方便的设置相关选项来控制。

Assignments->Assignment Editor menu item

Category: Logic Options: I/O Timing

Then:

"To" column: select the pin (you can do this via Node Finder)

"Assignment Name" column: Slow Slew Rate

不过注意Cyclone II不支持这个选项,(但是Cyclone I,III支持)还好我们可以在另外一个地方设置:

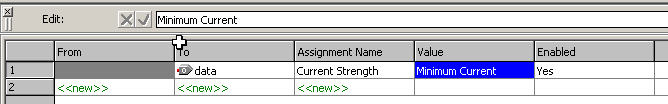

Assignment Editor - Logic Options - I/O Features - Assignment Name "Current Strength" - Value "Minimum Current".

The "output pins" section indicates the current limit changed to 4mA (was 24mA).

如果觉得斜率还是偏大,可以使用RC来进一步降低斜率。

/2

/2

文章评论(0条评论)

登录后参与讨论