难度蛮大的奥。编写中。。。。

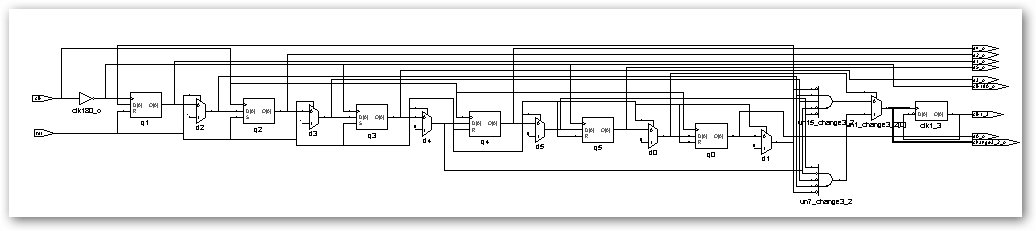

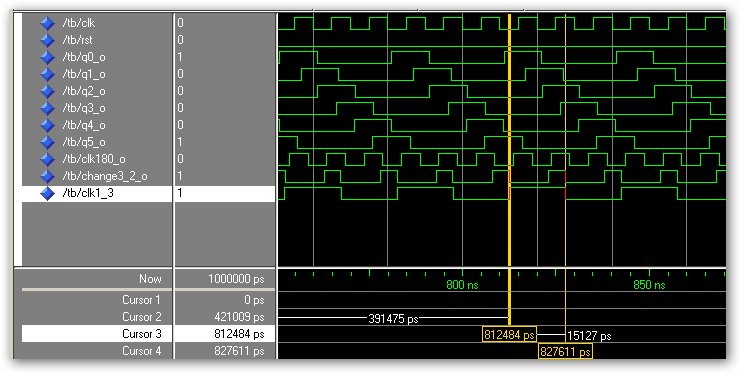

搞定一个版本的(原创):用6个(外加一个)实现,3个用上升沿,3个用下降沿触发(VHDL是通过反相clk,然后上升沿有效)开始赋值“001100”(不能用“000100”)然后每个clk的跳变沿循环左移一位。3个时钟周期循环左移6次,每移三次,clk1_3反相。从而得到。但是中间由于存在组合逻辑,故占空比不能达到严格的1:1.布线FPGAxilinx器件,仿真结果15.8:14.2(周期10ns)还是有一定差距的。

entity fre_div is

Port ( clk : in STD_LOGIC;

rst : in STD_LOGIC;

q0_o,q1_o,q2_o,q3_o,q4_o,q5_o :out std_logic;

clk180_o: out std_logic;

change3_2_o: out std_logic;

clk1_3 : out STD_LOGIC);

end fre_div;

architecture Behavioral of fre_div is

signal d0,d1,d2,d3,d4,d5 :std_logic;

signal q0,q1,q2,q3,q4,q5 :std_logic;

signal change3_2,clk0,clk180:std_logic;

begin

clk180<= not clk0;

clk0<=clk;

q0_o<=q0;

q1_o<=q1;

q2_o<=q2;

q3_o<=q3;

q4_o<=q4;

q5_o<=q5;

clk180_o<=clk180;

change3_2_o<=change3_2;

process(rst,q0,q1,q2,q3,q4,q5)

begin

if rst='1' then

d0<='0';

d1<='0';

d2<='1';

d3<='1';

d4<='0';

d5<='0';

else

d0<=q5;

d1<=q0;

d2<=q1;

d3<=q2;

d4<=q3;

d5<=q4;

end if;

end process;

process(clk0)

begin

if (clk0'event and clk0='1') then

q0<=d0;

q2<=d2;

q4<=d4;

end if;

end process;

process(clk180)

begin

if (clk180'event and clk180='1') then

q1<=d1;

q3<=d3;

q5<=d5;

end if;

end process;

change3_2<=(( d5) and (not d4) and (not d3) and (not d2) and (not d1) and ( d0))

or ((not d5) and (not d4) and ( d3) and ( d2) and (not d1) and (not d0));

process(change3_2)

begin

if (change3_2'event and change3_2='1') then

clk1_3<= not clk1_3;

end if;

end process;

end Behavioral;

改进措施:在synplify中加入retiming选项,效果明显好转。15.1:14.9(布局布线原因很大)

仿真结果:

欢迎切磋!

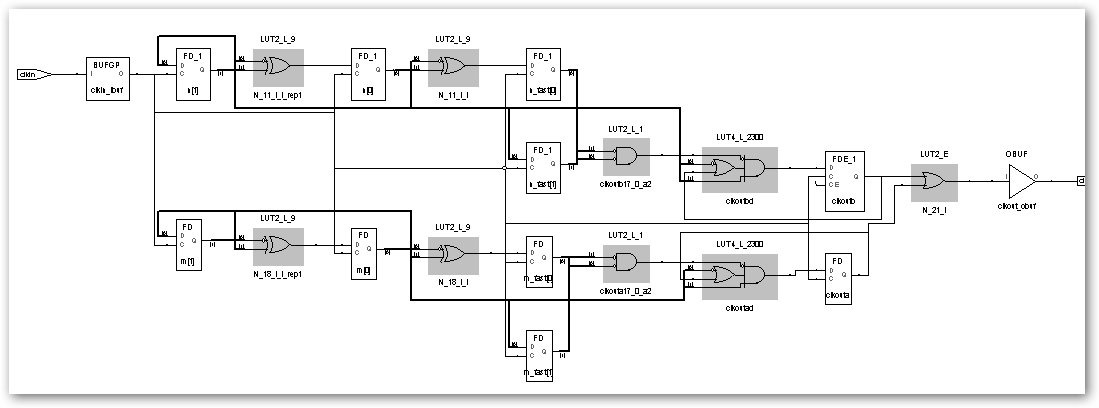

感谢ostrich1983 的补充,他的方案,跟家的简洁,易懂。自己的是从数字电路设计的角度编写的。而ostrich1983 的方案设计的层次更高,,仿真了下,占空比基本上也是14.9:15.1。

下面是ostrich1983 方案的综合:

/1

/1

tengjingshu_112148725 2009-1-11 21:23

用户502718 2007-12-28 17:33

module div3(clkin,clkout);

input clkin;

output clkout;

reg clkout,clkouta,clkoutb;

reg [1:0]m,n;

always@(posedge clkin)

begin

case(m)

0:begin clkouta<=0;m<=m+1'b1;end

1:begin clkouta<=0;m<=m+1'b1;end

2:begin clkouta<=1;m<=0;end

endcase

end

always@(negedge clkin)

begin

case(n)

0:begin clkoutb<=0;n<=n+1'b1;end

1:begin clkoutb<=0;n<=n+1'b1;end

2:begin clkoutb<=1;n<=0;end

endcase

end

always@(clkouta,clkoutb)

begin

clkout=clkouta|clkoutb;

end

endmodule

用户1393038 2007-12-27 15:00

不好意思

刚写好

哈

用户42640 2007-12-26 22:33