在测量过程中,高的波形捕获率对于示波器来说很重要,它可以提高示波器捕获随机事件和低概率事件的能力。

在说明波形捕获率之前,首先需弄清楚死区时间的概念。

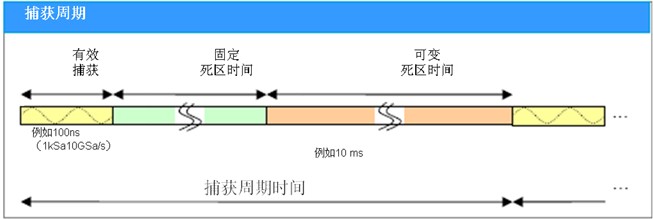

何谓死区时间?即:两次采集之间,示波器触发释抑、重新准备下一次采集、数据处理时间的总和。死区时间可能比采集时间长,而且长很多。下图显示了一个波形捕获周期的示意图。波形捕获率即为捕获周期时间的倒数。

在上图中,捕获的死区时间包括固定死区时间和可变死区时间两部分。固定死区时间取决于各个仪器的架构本身。可变死区时间则取决于处理所需的时间,它与设定的捕获样本数(记录长度)、水平刻度、采样率以及所选的后处理功能有关(例如,插值、数学函数、测量与分析等)。

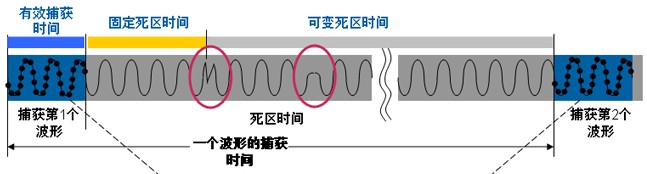

死区时间过长容易导致一些关键信号信息丢失。如下图所示。

根据以下公式,如果波形捕获时间(即:样本数*分辨率,或10格*水平刻度)、波形捕获率和信号事件发生概率均已确定,那么增加测量时间可加大捕获并显示信号事件的概率。

其中:

P:捕获偶发重复信号事件的概率 [单位是 %]

GlitchRate:信号故障频率(例如,重复脉冲干扰)[单位是 1/s]

T:有效捕获时间或波形显示时间(记录长度/采样速率,或记录长度 * 分辨率,或 10 * 时间量程/格)[单位是 s]

AcqRate:波形捕获率 [单位是 wfms/s]

Tmeasure:测量时间 [单位是 s]

下面举例说明。

例一:

假定毛刺出现频率为10次每秒,观察时间窗口为50ns(10格*5ns/div),观察时间为5s。

按上述公式进行计算如下:

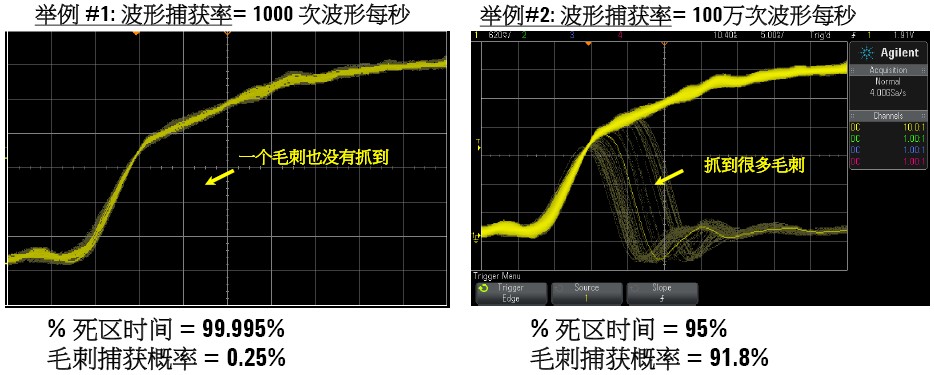

(1)若波形捕获率为1000次波形每秒:

死区时间%=(1ms-50ns)/1ms=99.995%

毛刺捕获概率P=100-100*(1-10*50ns)1000*5s=0.25%

(2)若波形捕获率为100万次波形每秒:

死区时间%=(1us-50ns)/1us=95%

毛刺捕获概率P=100-100*(1-10*50ns)1000000*5s=91.8%

见下图所示。

例二:

假定某个信号带有一个每秒重复10次的异常。要使该信号显示在示波器上,所采用的水平刻度为10ns/div,如果所用显示屏有10个水平格,则可以计算100ns的有效捕获时间。为了确保捕获所需信号事件的置信度较高,需要达到99.9%的概率。现在,所需的测试时间取决于示波器的波形捕获率,结果见下表:

表1 捕获重复异常信号所需时间

因此,波形捕获率和水平刻度、记录长度、采样率的设置都有关系。在实际测量过程中,需要根据实际的被测信号在这些参数设置中找到一个平衡点,以最高的捕获概率查看波形,提高调试效率。

/5

/5

用户1259054 2012-5-15 13:59