在某FPGA系统中,对电源系统进行调试,在同样的测试条件下,发现其中有一块板相对其它的板功耗总偏大,进而对其进行调试分析。

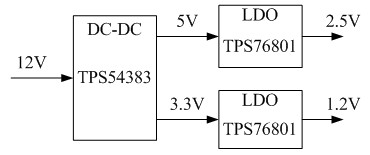

在该系统中,输入电压为DC12V,输出电压有:5V、3.3V、2.5V和1.2V,综合考虑电源纹波和转换效率,在该系统中采用了DC-DC和LDO,基本框图如下所示:

该DC-DC为双路输出(5V和3.3V)。这里,功率电感的大小选择为10uH。以下是对各输出电压所进行的纹波测试,波形如下:

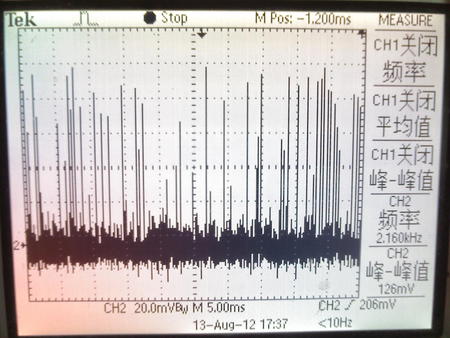

图1 5V电压纹波

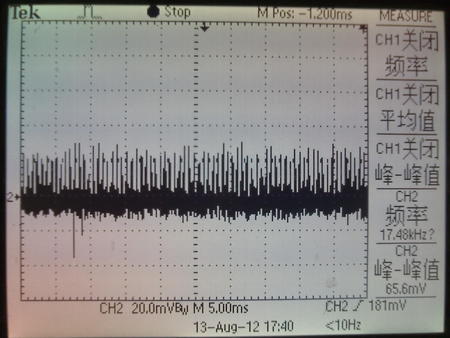

图2 3.3V电压纹波

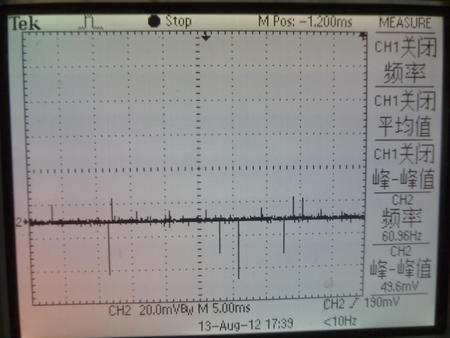

图3 2.5V电压纹波

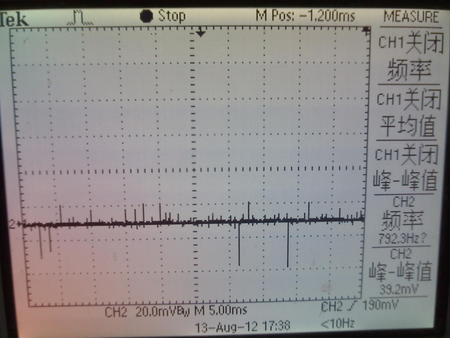

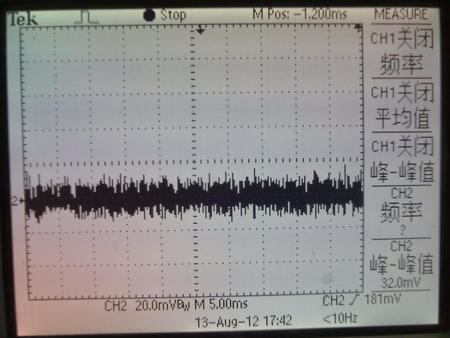

图4 1.2V电压纹波

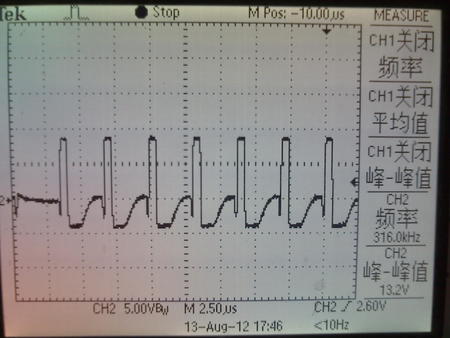

由以上可以看出,各电压的纹波相当大,再次测试5V一侧的斩波波形,如下图。

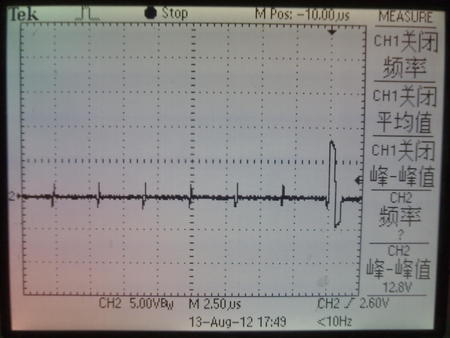

图5 5V一侧斩波波形

从图中可以看出,该斩波波形是较差的。在FPGA系统中则会表现为:整个系统电流偏大,进而影响功耗偏大。

因此,这里重点考虑DC-DC外围元件的参数选择不合理。首先从功率电感入手,将其由10uH加大到15uH,再次进行测试。更换功率电感后的斩波波形如下,得到了较大改善。

图6 更换L后5V一侧斩波波形

再次测量各电压纹波如下:

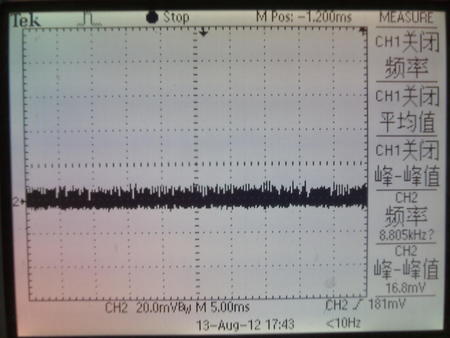

图7 更换L后5V电压纹波

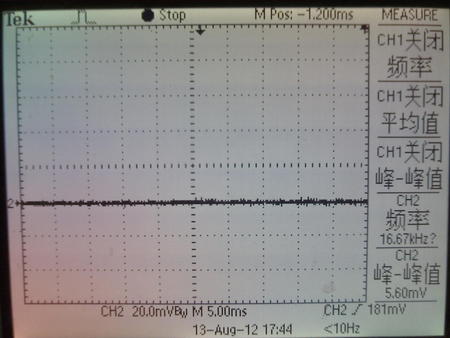

图8 更换L后3.3V电压纹波

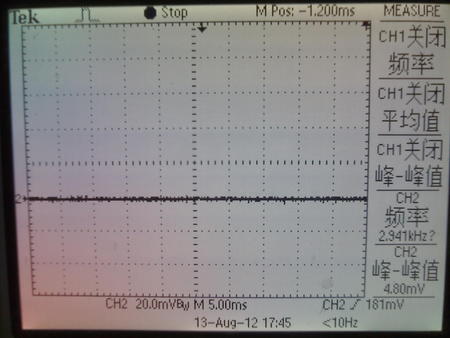

图9 更换L后2.5V电压纹波

图10 更换L后1.2V电压纹波

更换L前各电压的纹波分别为:126mV,65.6mV,49.6mV,39.2mV;

更换L后各电压的纹波又分别为:32mV,16.8mV,5.6mV,4.8mV。

从以上可以看出,各电压纹波对得到了较大的改善。继续对电路进行改进,加大去耦电容,经测试,纹波再一次得到了减小,不过作用并不是太明显。

分析:若DC-DC的纹波较大,则会直接影响其转换效率,进而造成一些不必要的能量浪费,使整个系统的功耗偏大。

纹波偏大的影响:

纹波过大会引起系统工作不稳定,发热量偏高等。长期的工作不稳定还可能造成芯片功能下降或损坏

总结:功率电感对于DC-DC的影响是极大的,在实际的DC-DC电源调试过程中,如果发现输出纹波较大,可以先测试一下其斩波波形,并首先尝试改变一下功率电感的参数(应尽量满足芯片手册给出的要求),增大电源滤波电容等;纹波大还有可能是PCB走线不合理造成,所以在PCB的设计过程中也要引起重视(一般在芯片手册中都有Layout指导,可参考)。

一般来说,Buck型DC-DC的输出纹波应该控制在20-30mV以下,而LDO的纹波则应该控制在10mV以下。如果纹波是50Hz或者100Hz有效值波形,则很可能是输入滤波电容小了;如果纹波是开关频率的有效值波形,则可能是输出电感或电解电容小了;如果纹波是高频波形,则可能是反馈电路的元器件参数不当,或者是PCB走线不好等造成。

在某些场合,若对纹波要求较高,而输入输出压差又较大,还可以考虑采用DC-DC加LDO的方式供电。

当然,以上这些都是针对一般的应用而言,如果是更高要求的系统,则应进行更加全面、深入的考虑和测试。

saj 2015-5-20 16:06

395354912_796243290 2015-5-20 11:34

用户1010551 2013-3-20 23:06

asus119_412419641 2012-9-3 22:14

coyoo 2012-9-3 12:29

fanyan_tll_621621837 2012-8-31 21:52

按你们的设计,功率电感的饱和电流Isat应该是2A左右,这样规格10-15-22uH带屏蔽的功率电感最小也应该有7×7这么大,如果还要小3.3-1.2V这路就有可能饱和了。如果对大小这么敏感,何不直接用TI的电源模块,不带隔离的2A以内的可调输出这个电源就只有10几个毫米长,开关芯片这些都是QFN的封装。系统应该是Altera的FPGA。最好把调试开关波形采集出来看一看,是不是饱和也能看得出来。也可以先估算一下占空比是多大,这里要是有问题最好不要接芯片负载,接了负载肯定烫,因为电流上去了饱和后感值就降低了,直接漏过去芯片就会发热,电感也能听到啸叫声。调试的时候不应该先去关心纹波,一般SW波形对了后面纹波都问题不大,设计的时候也可以外加LC滤波去抑制纹波。另外,功率电感并不是选择上要越大越好,选择上一般都选比理论值大一级的标称电感,10.9uH选10uH就不应该,按照这个经验,直接选择15uH@2A的就不会有饱和的问题。

asus119_412419641 2012-8-31 18:19

用户593939 2012-8-30 23:51

fanyan_tll_621621837 2012-8-30 17:07

ilove314_323192455 2012-8-30 12:50