使用过Cadence也有一段时间了,现在对其原理图工具的使用做一小结。

1、多张Page页面时,信号的连接

对于较复杂的设计,一般都会将整个设计细分成各个模块来设计,以便于阅读和管理,这时就会用到多张Page页面。在Capture CIS中,用于信号连接的有三种:网络标号、Hierarchical Port、Off-Page Connector。它们的应用场合各不相同,网络标号通常用于当前Page中的信号连接;Hierarchical Port用于层次设计时各层信号的连接;而Off-Page Connector则是用于平坦式设计时的不同Page间信号的连接。它们虽然可以通用,但是不注意的话就容易出问题,比如:将Hierarchical Port用于平坦式电路设计的不同Page信号的连接,虽然也可以用,但是必须保证所连接信号的端口类型一致,如:当前Page中的CLK信号用了该类型端口,为Input(或Output)类型,那么在其他Page中的该CLK信号也必须为Input(或Output)类型的,否则就会出错。但是,如果用Off-Page Connector的话,就不会有这样的区分,不会出错,推荐使用。

因此,为了保证设计的准确,建议还是要遵守原理图设计的规范。

2、多Page页面设计时,显示页间标识符

在大型设计中,Page众多、信号众多,为了显示的直观,可将各Page页面中的信号添加上页间标识符。方法如下:

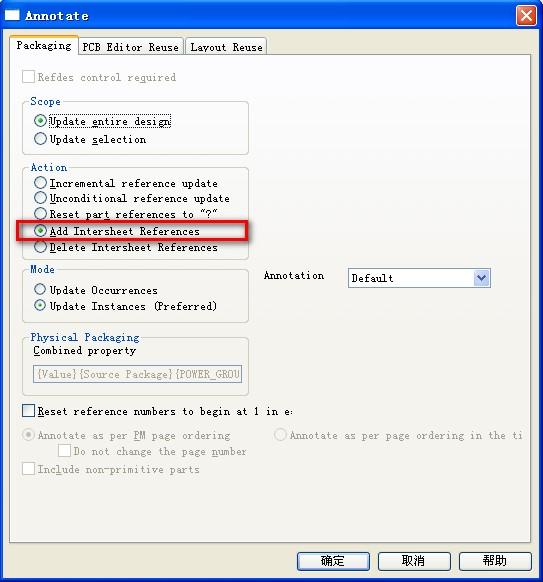

A、在Tool下调出Annotate注释窗口,在Packaging一栏的Action中选择Add Intersheet References。如下图:

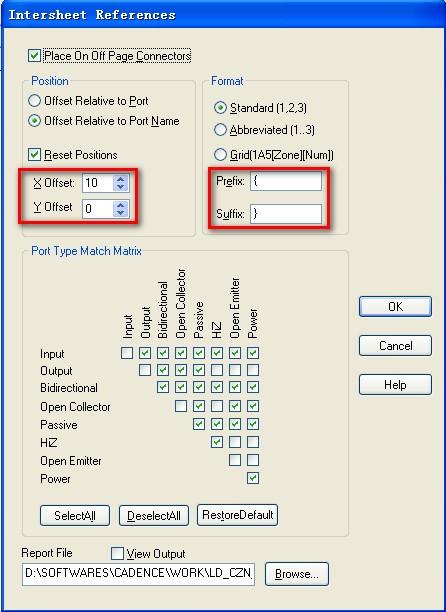

B、出现Intersheet References窗口,可设置标识符的偏移位置,格式,等等。

这里设置X轴偏移10,格式为{n},其它默认即可,OK即可,如下图:

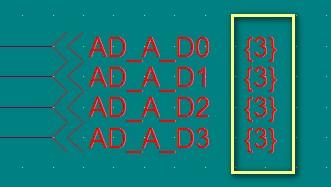

C、设置完成后的效果如下图,这样每个信号所在的Page页面就都标注出来了,可方便的对各信号进行管理,直观明了。

3、元件某属性隐藏后,如何再次显示出来

这里以电阻元件的Value属性为例说明。步骤如下:

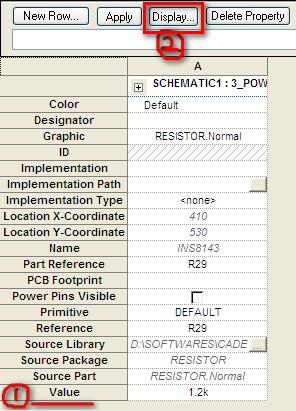

A、双击元件打开元件属性窗口。

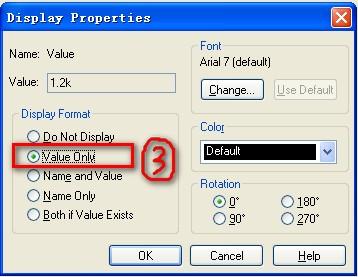

B、点击Value栏,然后点击窗口上方的Display按钮,将显示属性中的Format切换为需要显示的状态,OK即可。

C、返回原理图,之前隐藏的Value属性再次显示出来了。

其它内容待续,期待与各位的交流,共同学习、共同进步!

/2

/2

用户1626498 2014-3-27 21:57