一种电压驱动的场效应晶体管,以氧化物绝缘的金属或多晶为栅极,是单极晶体管,其工作依靠一种多数载流子(N型为电子,P型为空穴)的运动,而不是像双极结型场效应管(JFET)那样靠两种载流子同时运动。MOSFET的控制栅压作用于横跨绝缘层的沟道区,而不像结型场效应管那样横跨PN结。栅极用二氧化硅(SiO2)或氮化硅(SiN)来绝缘。MOSFET可以是P沟道也可以是N沟道,其工作可以是耗尽型或者增强型。MOSFET包括在CMOS和BiCMOS数字逻辑电路中,因为有源极和漏极之间的绝缘,所以MOSFET功耗低。另外MOSFET比JFET加工过程简单,硅的利用更经济,与基片更容易互连,也称为绝缘栅场效应晶体管(IGFET)。

MOSFET是Metal-Oxide-Silicon Field Effect Transistor的英文缩写,平面型器件结构,按照导电沟道的不同可以分为NMOS和PMOS器件。MOS器件基于表面感应的原理,是利用垂直的栅压VGS实现对水平IDS的控制。它是多子(多数载流子)器件。用跨导描述其放大能力。

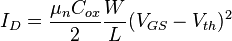

NMOS和PMOS在结构上完全相像,所不同的是衬底和源漏的掺杂类型。简单地说,NMOS是在P型硅的衬底上,通过选择掺杂形成N型的掺杂区,作为NMOS的源漏区;PMOS是在N型硅的衬底上,通过选择掺杂形成P型的掺杂区,作为PMOS的源漏区。如图所示,两块源漏掺杂区之间的距离称为沟道长度L,而垂直于沟道长度的有效源漏区尺寸称为沟道宽度W。对于这种简单的结构,器件源漏是完全对称的,只有在应用中根据源漏电流的流向才能最后确认具体的源和漏。

MOSFET有什么优点?

MOSFET和双极性晶体管(BJT)相比,MOSFET是一种高输入阻抗、电压控制的器件;BJT则是一种低阻抗、电流控制的器件。在功率应用中采用MOSFET具有众多好处。

1、MOSFET的驱动电路比较简单。BJT可能需要多达20%的额定集电极电流以保证饱和度,而MOSFET需要的驱动电流则小得多,而且通常可以直接由CMOS或者集电极开路TTL驱动电路驱动;

2、MOSFET的开关速度比较迅速,MOSFET是一种多数载流子器件,能够以较高的速度工作,因为没有电荷存储效应;

3、MOSFET没有二次击穿失效机理,它在温度越高时往往耐力越强,而且发生热击穿的可能性越低,还可以在较宽的温度范围内提供较好的性能。

器件的栅电极是具有一定电阻率的多晶硅材料,这也是硅栅MOS器件的命名根据。在多晶硅栅与衬底之间是一层很薄的优质二氧化硅,它是绝缘介质,用于绝缘两个导电层:多晶硅栅和硅衬底,从结构上看,多晶硅栅-二氧化硅介质-掺杂硅衬底 (Poly-Si--SiO2--Si) 形成了一个典型的平板电容器,通过对栅电极施加一定极性的电荷,就必然地在硅衬底上感应等量的异种电荷。这样的平板电容器的电荷作用方式正是MOS器件工作的基础。

以SiO2为栅介质时,叫MOS器件,这是最常使用的器件形式。历史上也出现过以Al2O3为栅介质的MAS器件和以 Si3N4为栅介质的MNS 器件,以及以SiO2+Si3N4为栅介质的MNOS器件,统称为金属-绝缘栅-半导体器件--MIS 器件。

以Al为栅电极时,称铝栅器件。以重掺杂多晶硅(Poly-Si) 为栅电极时, 称硅栅器件。它是当前MOS器件的主流器件。 硅栅工艺是利用重掺杂的多晶硅来代替铝做为MOS管的栅电极,使MOS电路特性得到很大改善,它使VTP下降1.1V,也容易获得合适的VTN值并能提高开关速度和集成度。

硅栅工艺具有自对准作用,这是由于硅具有耐高温的性质。栅电极,更确切的说是在栅电极下面的介质层,是限定源、漏扩散区边界的扩散掩膜,使栅区与源、漏交迭的密勒电容大大减小,也使其它寄生电容减小,使器件的频率特性得到提高。另外,在源、漏扩散之前进行栅氧化,也意味着可得到浅结。

self aligned poly-silicon process 自对准多晶硅工艺

铝栅工艺为了保证栅金属与漏极铝引线之间有一定的间隔,要求漏扩散区面积要大些。而在硅栅工艺中覆盖源漏极的铝引线可重迭到栅区,这是因为有一绝缘层将栅区与源漏电极引线隔开,从而可使结面积减少30%~40%。

硅栅工艺还可提高集成度,这不仅是因为扩散自对准作用可使单元面积大为缩小,而且因为硅栅工艺可以使用“二层半布线”即一层铝布线,一层重掺杂多晶硅布线,一层重掺杂的扩散层布线。由于在制作扩散层时,多晶硅要起掩膜作用,所以扩散层不能与多晶硅层交叉,故称为两层半布线.铝栅工艺只有两层布线:一层铝布线,一层扩散层布线。硅栅工艺由于有两层半布线,既可使芯片面积比铝栅缩小50%又可增加布线灵活性。

当然,硅栅工艺较之铝栅工艺复杂得多,需增加多晶硅淀积、等离子刻蚀工序,而且由于表面层次多,台阶比较高,表面断铝,增加了光刻的困难,所以又发展了以Si3N4作掩膜的局部氧化LOCOS--Local oxidation on silicon (又称为 MOSIC 的局部氧化隔离工艺Local Oxidation Isolation for MOSIC) ,或称等平面硅栅工艺。

扩散条连线由于其电容较大,漏电流也较大,所以尽量少用,一般是将相应管子的源或漏区加以延伸而成。扩散条也用于短连线,注意扩散条不能跨越多晶硅层,有时把这层连线称为“半层布线”。因硼扩散薄层电阻为30~120Ω/□,比磷扩散的R□大得多,所以硼扩散连线引入的分布电阻更为可观,扩散连线的寄生电阻将影响输出电平是否合乎规范值,同时也因加大了充放电的串联电阻而使工作速度下降。因此,在CMOS电路中,当使用硼扩散条做连线用时要考虑到这一点。

当在NMOS的栅上施加相对于源的正电压VGS时,栅上的正电荷在P型衬底上感应出等量的负电荷,随着VGS的增加,衬底中接近硅-二氧化硅界面的表面处的负电荷也越多。其变化过程如下:当VGS比较小时,栅上的正电荷还不能使硅-二氧化硅界面处积累可运动的电子电荷,这是因为衬底是P型的半导体材料,其中的多数载流子是正电荷空穴,栅上的正电荷首先是驱赶表面的空穴,使表面正电荷耗尽,形成带固定负电荷的耗尽层。

这时,虽然有VDS的存在,但因为没有可运动的电子,所以,并没有明显的源漏电流出现。增加VGS,耗尽层向衬底下部延伸,并有少量的电子被吸引到表面,形成可运动的电子电荷,随着VGS的增加,表面积累的可运动电子数量越来越多。这时的衬底负电荷由两部分组成:表面的电子电荷与耗尽层中的固定负电荷。如果不考虑二氧化硅层中的电荷影响,这两部分负电荷的数量之和等于栅上的正电荷的数量。当电子积累达到一定水平时,表面处的半导体中的多数载流子变成了电子,即相对于原来的P型半导体,具有了N型半导体的导电性质,这种情况称为表面反型。

The metal-oxide-semiconductor field-effect transistor (MOSFET, MOS-FET, or MOS FET), is by far the most common field-effect transistor in both digital and analog circuits. The MOSFET is composed of a channel of n-type or p-type semiconductor material (see article on semiconductor devices), and is accordingly called an NMOSFET or a PMOSFET (also commonly nMOSFET, pMOSFET, NMOS FET, PMOS FET, nMOS FET, pMOS FET).

The 'metal' in the name is an anachronism from early chips in which the gates were metal; modern chips use polysilicon gates. IGFET is a related, more general term meaning insulated-gate field-effect transistor, and is almost synonymous with "MOSFET", though it can refer to FETs with a gate insulator that is not oxide. Some prefer to use "IGFET" when referring to devices with polysilicon gates, but most still call them MOSFETs.

Usually the semiconductor of choice is silicon, but some chip manufacturers, most notably IBM, have begun to use a mixture of silicon and germanium (SiGe) in MOSFET channels. Unfortunately, many semiconductors with better electrical properties than silicon, such as gallium arsenide, do not form good gate oxides and thus are not suitable for MOSFETs.

The gate terminal is a layer of polysilicon (polycrystalline silicon; why polysilicon is used will be explained below) placed over the channel, but separated from the channel by a thin insulating layer of what was traditionally silicon dioxide, but more advanced technologies used silicon oxynitride. When a voltage is applied between the gate and source terminals, the electric field generated penetrates through the oxide and creates a so-called "inversion channel" in the channel underneath. The inversion channel is of the same type — P-type or N-type — as the source and drain, so it provides a conduit through which current can pass. Varying the voltage between the gate and body modulates the conductivity of this layer and makes it possible to control the current flow between drain and source.

A variety of symbols are used for the MOSFET. The basic design is generally a line for the channel with the source and drain leaving it at right angles and then bending back into the same direction as the channel. Sometimes a broken line is used for enhancement mode and a solid one for depletion mode, but the awkwardness of drawing broken lines means this distinction is often ignored. Another line is drawn parallel to the channel for the gate.

The bulk connection, if shown, is shown connected to the back of the channel with an arrow indicating PMOS or NMOS. Arrows always point from P to N, so an NMOS (N-channel in P-well or P-substrate) has the arrow pointing in. If the bulk is connected to the source (as is generally the case with discrete devices) it is angled to meet up with the source leaving the transistor. If the bulk is not shown (as is often the case in IC design as they are generally common bulk) an inversion symbol is sometimes used to indicate PMOS.

Comparison of enhancement and depletion mode symbols, along with JFET symbols:

|  |  |  | P-channel |

|  |  |  | N-channel |

| JFET | MOSFET enh | MOSFET dep | ||

For the symbols in which the bulk, or body, terminal is shown, it is here shown internally connected to the source. This is a typical configuration, but by no means the only important configuration. In general, the MOSFET is a four-terminal device, and in integrated circuits many of the MOSFETs share a body connection, not necessarily connected to the source terminals of all the transistors.

A metal-oxide-semiconductor (MOS) structure is obtained by depositing a layer of silicon dioxide (SiO2) and a layer of metal (polycrystalline silicon is actually used instead of metal) on top of a semiconductor die. As the silicon dioxide is a dielectric material its structure is equivalent to a plane capacitor, with one of the electrodes replaced by a semiconductor.

When a voltage is applied across a MOS structure, it modifies the distribution of charges in the semiconductor. If we consider a P-type semiconductor (with NA the density of holes), a positive VGB (see figure) tends to reduce the concentration of holes and increase the concentration of electrons. If VGB is high enough, the concentration of negative charge carriers near the gate is more than that of positive charges, in what is known as an inversion layer.

This structure with P-type body is the basis of the N-type MOSFET, which requires the addition of an N-type source and drain regions.

A metal-oxide-semiconductor field-effect transistor (MOSFET) is based on the modulation of charge concentration caused by a MOS capacitance. It includes two terminals (source and drain) each connected to separate highly doped regions. These regions can be either P or N type, but they must both be of the same type. The highly doped regions are typically denoted by a '+' following the type of doping (see the image at the right). These two regions are separated by a doped region of opposite type, known as the body. This region is not highly doped, denoted by the lack of a '+' sign. The active region constitutes a MOS capacitance with a third electrode, the gate, which is located above the body and insulated from all of the other regions by an oxide.

If the MOSFET is an N-Channel or nMOS FET, then the source and drain are 'N+' regions and the body is a 'P' region. When a positive gate-source voltage is applied, it creates an N-channel at the surface of the P region, just under the oxide. This channel spreads from the source to the drain and provides conductivity of the transistor. When zero or negative voltage is applied between gate and source, the channel disappears and no current can flow between the source and the drain.

If the MOSFET is an P-Channel or pMOS FET, then the source and drain are 'P+' regions and the body is a 'N' region. When a negative gate-source voltage (positive source-gate) is applied, it creates a P-channel at the surface of the N region, just under the oxide. This channel spreads from the source to the drain and provides conductivity of the transistor. When no or a positive voltage is applied between gate and body, the channel disappears and no current can flow between the source and the drain.

The source is so named because it is the source of the charge carriers (electrons for N-channel, holes for P-channel) that flow through the channel; similarly, the drain is where the charge carriers leave the channel.

The operation of a MOSFET can be separated into three different modes, depending on the voltages at the terminals. For an enhancement mode, n-channel MOSFET the modes are:

The body effect describes the changes in the threshold voltage by the change in the source-bulk voltage, approximated by the following equation:

,

,

where VTO is the zero substrate bias, γ is the body effect parameter, and 2φ is the surface potential parameter.

The body can be operated as a second gate, and is sometimes referred to as the "back gate"; the body effect is sometimes called the "back-gate effect". (http://equars.com/~marco/poli/phd/node20.html)

In 1960, Dawon Kahng and Martin Atalla at Bell Labs invented the metal oxide semiconductor field-effect transistor (MOSFET). Theoretically different from Shockley's transistor, the MOSFET was structured by putting an insulating layer on the surface of the semiconductor and then placing a metallic gate electrode on that. It used crystalline silicon for the semiconductor and a thermally oxidized layer of silicon dioxide for the insulator. Not only did it possess such technical attractions as low cost of production and ease of integration, the silicon MOSFET serendipitously did not generate localized electron traps (interface states) at the interface between the silicon and its native oxide layer, and thus was free of the characteristic that had impeded the performance of earlier transistors. Buoyed by this stroke of good fortune, the MOSFET has achieved electronic hegemony. It is this serendipity that sustains the large-scale integrated circuits (LSIs) underlying today's information society.

The growth of digital technologies like the microprocessor has provided the motivation to advance MOSFET technology faster than any other type of silicon-based transistor. The principal reason for the success of the MOSFET was the development of digital CMOS logic, which uses p- and n-channel MOSFETs as building blocks. The great advantage of CMOS logic is that they allow no current to flow (ideally), and thus no power to be consumed, except when the inputs to logic gates are being switched. CMOS accomplishes this by complementing every nMOSFET with a pMOSFET and connecting both gates and both drains together. A high voltage on the gates will cause the nMOSFET to conduct and the pMOSFET not to conduct and a low voltage on the gates causes the reverse. During the switching time the voltage goes from one state to another and both will conduct. This arrangement greatly reduces power consumption and heat generation. Overheating is a major concern in integrated circuits, since ever more transistors are packed into ever smaller chips.

Another advantage of MOSFETs for digital switching is that the oxide layer between the gate and the channel prevents DC current from flowing through the gate, further reducing power consumption and giving a very large input impedance. The insulating oxide between the gate and channel effectively isolates a MOSFET in one logic stage from earlier and consequent stages, which allows to drive a considerable number of MOSFET inputs from a single MOSFET output. Bipolar transistor-based logics (such as TTL) do not have such a high fanout capacity. This isolation also makes it easier for the designers to ignore to some extent loading effects between logic stages independently. That extent is defined by the operating frequency: as frequencies increase, the input impedance of the MOSFETs decreases.

The MOSFET's strengths as the workhorse transistor in most digital circuits do not translate into supremacy in analog circuits. The bipolar junction transistor (BJT) has traditionally been the analog designer's transistor of choice, due largely to its high transconductance and unique properties. Nevertheless, MOSFETs are widely relied upon for analog purposes as well. Some of the advantages of MOSFETs are that due to their positive temperature coefficient, they do not suffer from thermal runaway as BJTs do and that their linear region allows them to be used as precision resistors, which can have a much higher controlled resistance than BJTs. Also, they can be formed into capacitors and specialized circuits allow op-amps made from them to appear as inductors, thereby allowing all of the normal analog devices, except for diodes (which can be made smaller than a MOSFET anyway), to be built entirely out of MOSFETs. This allows for complete analog circuits to be made on a silicon chip in a much smaller space. Some ICs combine analog and digital MOSFET circuitry on a single chip, making the needed board space even smaller. This creates a need to isolate the analog circuits from the digital circuits on a chip level, leading to the use of isolation rings and Silicon-On-Insulator (SOI). The main advantage of BJTs vs MOSFETs in the analog design process is the ability of BJTs to handle a larger current in a smaller space. Fabrication processes exist that incorporate BJTs and MOSFETs into a single device, these mixed-transistor devices are called Bi-FETs (Bipolar-FETs) if they contain just one BJT-FET and BiCMOS (bipolar-CMOS) if they contain complementary BJT-FETs. This device provides for the advantages of both the insulated gate and the higher current density.

The BJT also has some advantages over the MOSFET in certain digital circuits. BJTs are currently better for at least 2 digital jobs. The first is in high speed switching because they don't have the "larger" capacitance from the gate, which when multiplied by the resistance of the channel gives the intrinsic time constant of the process. The intrinsic time constant places a limit on the speed a MOSFET can operate at because higher frequency signals are filtered out. Widening the channel reduces the resistance of the channel, but increases the capacitance by the exact same amount. Reducing the width of the channel increases the resistance, but reduces the capacitance by the same amount. R*C=Tc1, 0.5R*2C=Tc1, 2R*0.5C=Tc1. There is no way to minimize the intrinsic time constant for a certain process. Different processes using different channel lengths, channel heights, gate thicknesses and materials will have different intrinsic time constants. You can skip most of this problem with a BJT because it doesn't have a gate. The second job stems from the first. When driving many other gates, called fanning out, the resistance of the MOSFET is in series with the gate capacitances of the other FETs, creating a secondary time constant. Delay circuits use this fact to create a set signal delay by using a small CMOS device to send a signal to many other, many times larger CMOS devices. The secondary time constant can be minimized by increasing the driving FETs channel width to decrease its resistance and decreasing the channel width of the FETs being driven, decreasing their capacitance. This does have a drawback because it increases the capacitance of the driving FET and increases the resistance of the FETs being driven, but usually those drawbacks are a minimal problem when compared to the timing problem. BJTs are better to drive the other gates because they can output more current than MOSFETs, allowing for the FETs being driven to charge faster. Many chips will employ MOSFET inputs and BiCMOS (see above paragraph) outputs.

Over the past decades, the MOSFET has continually been scaled down in size; typical MOSFET channel lengths were once several micrometres, but modern integrated circuits are incorporating MOSFETs with channel lengths of less than a tenth of a micrometre. Indeed Intel began production of a process featuring a 65 nm feature size (with the channel being even shorter) in early 2006. Until the late 1990s, this size reduction resulted in great improvement to MOSFET operation with no deleterious consequences. Historically, the difficulties with decreasing the size of the MOSFET have been associated with the semiconductor device fabrication process.

Smaller MOSFETs are desirable for several reasons. First, smaller MOSFETs may allow more current to pass, due to their shorter length dimension; conceptually, MOSFETs are like resistors in the on-state, and shorter resistors have less resistance; however, they may also have smaller widths, leading to proportionally higher resistance, so the real issue is whether the ohms per square is reduced. Second, smaller MOSFETs have smaller gate areas, and thus lower gate capacitance. Scales MOSFETs also have thinner gate dielectrics, which reduces the on-state ohms per square but makes the gate capacitance per unit area higher; nevertheless, these effects still both go in the right direction. These first two factors contribute to lower switching times, and thus higher processing speeds, and lower energy per switching event. A third reason for MOSFET scaling is reduced area, leading to reduced cost. Smaller MOSFETs can be packed more densely, resulting in either smaller chips or chips with more computing power in the same area. Because the cost of fabricating a semiconductor wafer is relatively fixed, the cost of the individual integrated circuits is mainly related to the number of chips that can be produced per wafer. Hence, smaller ICs allow more chips per wafer, reducing the price per chip.

Producing MOSFETs with channel lengths smaller than a micrometre is a challenge, and the difficulties of semiconductor device fabrication are always a limiting factor in advancing integrated circuit technology. Recently, the small size of the MOSFET has created operational problems.

Because of small MOSFET geometries, the voltage that can be applied to the gate must be reduced to maintain reliability. To maintain performance, the threshold voltage of the MOSFET has to be reduced as well. As threshold voltage is reduced, the transistor cannot be completely turned off; that is, the transistor operates in weak-inversion mode, with a subthreshold leakage, or subthreshold conduction, between source and drain. Subthreshold conduction, which was ignored in the past, now can consume upwards of half of the total power consumption of modern high-performance VLSI chips.

Some micropower analog circuits are designed to take advantage of subthreshold conduction; by working in the weak-inversion region, the MOSFETs in these circuits deliver the highest possible transconductance-to-current ratio.

Traditionally switching time was roughly proportional to the gate capacitance of gates. However, with transistors becoming smaller and more transistors being placed on the chip, interconnect capacitance (the capacitance of the wires connecting different parts of the chip) is becoming a large percentage of capacitance. Signals have to travel through the interconnect, which leads to increased delay and lower performance.

The ever-increasing density of MOSFETs on an integrated circuit is creating problems of substantial localized heat generation that can impair circuit operation. Circuits operate slower at high temperatures, and have reduced reliability and shorter lifetimes. Heat sinks and other cooling methods are now required for many integrated circuits including microprocessors.

Power MOSFETs are at risk of thermal runaway. As their on-state resistance rises with temperature, the power loss on the junction rises correspondingly, generating further heat. When the heatsink is not able to keep the temperature low enough, the junction temperature may quickly and uncontrollably rise, resulting in destruction of the device.

The gate oxide, which serves as insulator between the gate and channel, should be made as thin as possible to increase the channel conductivity and performance when the transistor is on and to reduce subthreshold leakage when the transistor is off. However, with current gate oxides with a thickness of around 1.2 nm (which in silicon is ~5 atoms thick) the quantum mechanical phenomenon of electron tunneling occurs between the gate and channel, leading to increased power consumption.

Insulators (referred to as high-k dielectrics) that have a larger dielectric constant than silicon dioxide, such as group IVb metal silicates e.g. hafnium and zirconium silicates and oxides, are now being researched to reduce the gate leakage. Increasing the dielectric constant of the gate oxide material allows a thicker layer while maintaining a high capacitance. The higher thickness reduces the tunneling current between the gate and the channel. An important consideration is the barrier height of the new gate oxide; the difference in conduction band energy between the semiconductor and the oxide (and the corresponding difference in valence band energy) will also affect the leakage current level. For the traditional gate oxide, silicon dioxide, the former barrier is approximately 8 eV. For many alternative dielectrics the value is significantly lower, somewhat negating the advantage of higher dielectric constant.

With MOSFETS becoming smaller, the number of atoms in the silicon that produce many of the transistor's properties is becoming fewer. During chip manufacturing, random process variation can affect the size of the transistor, which becomes a greater percentage of the overall transistor size as the transistor shrinks. The transistor characteristics become less deterministic, but more statistical. This statistical variation increases design difficulty.

The primary criterion for the gate material is that it is a good conductor. Highly-doped polycrystalline silicon is an acceptable, but certainly not ideal conductor, and it also suffers from some more technical deficiencies in its role as the standard gate material. Nevertheless, there are several reasons favoring use of polysilicon as a gate material:

While polysilicon gates have been the defacto standard for the last twenty years, they do have some disadvantages, which could lead to their replacement by metal gates or other materials in the future. These disadvantages include:

The dual gate MOSFET has a tetrode configuration, where both gates control the current in the device. It is commonly used for small signal devices in radio frequency applications where the second gate is normally used for gain control or mixing and frequency conversion.

There are depletion mode MOSFET devices, which are less commonly used than the standard enhancement mode devices already described. These are MOSFET devices which are doped so that a channel exists even without any voltage applied to the gate. In order to control the channel, a negative voltage is applied to the gate, depleting the channel which reduces the current flow through the device. In essence, the depletion mode device is equivalent to a normally closed switch, while the enhancement mode device is equivalent to a normally open switch.

n-channel MOSFETs are smaller than p-channel MOSFETs and producing only one type of MOSFET on a silicon substrate is cheaper and technically simpler. These were the driving principles in the design of NMOS logic which uses n-channel MOSFETs exclusively. However, unlike CMOS logic, NMOS logic consumes power even when no switching is taking place. With advances in technology, CMOS logic displaced NMOS logic in the 1980s to become the preferred process for digital chips.

Power MOSFETs have a different structure than the one presented above. As with all power devices, the structure is vertical and not planar. Using a vertical structure, it is possible for the transistor to sustain both high blocking voltage and high current. The voltage rating of the transistor is a function of the doping and thickness of the N epitaxial layer (see cross section), while the current rating is a function of the channel width (the wider the channel, the higher the current). In a planar structure, the current and breakdown voltage ratings are both function of the channel dimensions (respectively width and length of the channel), resulting in inefficient use of the "silicon estate". With the vertical structure, the component area is roughly proportional to the current it can sustain, and the component thickness (actually the N-epitaxial layer thickness) is proportional to the breakdown voltage.

It is worth noting that power MOSFETs with lateral structure exist. They are mainly used in high-end audio amplifiers. Their advantage is a better behaviour in the saturated region (corresponding to the linear region of a bipolar transistor) than the vertical MOSFETs. Vertical MOSFETs are designed for switching applications, so they are only used in On or Off states.

DMOS stands for double-Diffused Metal Oxide Semiconductor. Most of the power MOSFETs are made using this technology.

MOSFET analog switches use the MOSFET channel as a low–on-resistance switch to pass analog signals when on, and as a high impedance when off. Signals flow in both directions across a MOSFET switch. In this application the drain and source of a MOSFET exchange places depending on the voltages of each electrode compared to that of the gate. For a simple MOSFET without an integrated diode, the source is the more negative side for an N-MOS or the more positive side for a P-MOS. All of these switches are limited on what signals they can pass or stop by their gate-source, gate-drain and source-drain voltages, and source-to-drain currents; exceeding the voltage limits will potentially damage the switch.

This analog switch uses a four-terminal simple MOSFET of either P or N type. In the case of an N-type switch, the body is connected to GND and the gate is used as the switch control. Whenever the gate voltage exceeds the source voltage by at least a threshold voltage, the MOSFET conducts. The higher the voltage, the more the MOSFET conducts. An N-MOS will pass through all voltages less than (Vgate-Vtn), measured with respect to the body. The switches are usually operated in the saturation region, since the drain and source tend to the same voltage when the switch is on.

In the case of a P-MOS, the body is connected to Vdd and the gate is brought to a lower potential to turn the switch on. The P-MOS switch passes all voltages higher than (Vgate+Vtp), measured with respect to the body.

A P-MOS switch will have three times the resistance of an N-MOS device of equal dimensions because electrons have three times the mobility of holes in silicon.

This "complementary" or CMOS type of switch uses one P-MOS and one N-MOS FET to counteract the limitations of the single-type switch. The FETs have their drains and sources connected in parallel, the body of the P-MOS is connected to the high potential (VDD) and the body of the N-MOS is connected to the low potential (Gnd). To turn the switch on the gate of the P-MOS is driven to the low potential and the gate of the N-MOS is driven to the high potential. For voltages between (VDD-Vtn) and (Gnd+Vtp) both FETs conduct the signal, for voltages less than (Gnd+Vtp) the N-MOS conducts alone and for voltages greater than (VDD-Vtn) the P-MOS conducts alone.

The only limits for this switch are the gate-source, gate-drain and source-drain voltage limits for both FETs. Also, the P-MOS is typically three times the width of the N-MOS so the switch will be balanced.

Tri-state circuitry sometimes incorporates a CMOS MOSFET switch on its output to provide for a low ohmic, full range output when on and a high ohmic, mid level signal when off.

/5

/5

文章评论(0条评论)

登录后参与讨论