TimeQuest Timing Analyzer工具使用一例

作者:RyudoYang

工具版本:Quartus II 13.1+TimeQuest Timing Analyzer

同事在进行SDR SDRAM时序约束时遇到工具使用和概念上的诸多问题,有些问题具有代表性,这里一并总结。

(1) 问题抽象

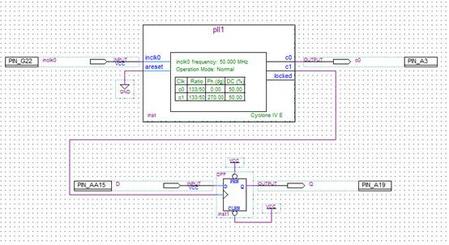

图1 SDR SDRAM约束问题抽象

图1是SDR SDRAM接口电路的抽象(以输入数据为例进行分析)。

由PLL产生2个133MHz的时钟,其中C0输出作为SDR SDRAM的芯片时钟使用,另一个时钟经过270°的移相,作为SDR SDRAM输入数据的锁存时钟使用。注意,这里时钟的用法也是解决很多时序问题的技巧之一。

以上是该问题的抽象,不需要过多解释。

(2) TimeQuest Timing Analyzer使用与分析过程

对图1所示的小工程进行全编译之后,打开TimeQuest Timing Analyzer(以下简称为TQ)进行分析。

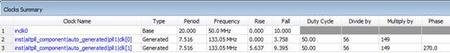

首先进行时钟设置。

图2 时钟约束

第2步,对SDR SDRAM用到的时钟进行约束,该时钟是通过PLL的C0输出得到的。采用的约束是:create_generated_clock -name clkout -source [get_pins {inst|altpll_component|auto_generated|pll1|clk[0]}] [get_ports {c0}],然后更新网表,检查约束是否生效。

图2 新的时钟约束已经生效

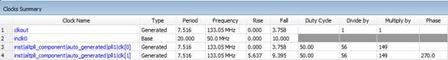

第3步,对外部输入延时进行设置,为了简化,采用的约束是:set_input_delay -clock { clkout } 5 [get_ports {D}],生效后检查建立时间,发现违规。

图3 建立时间违规

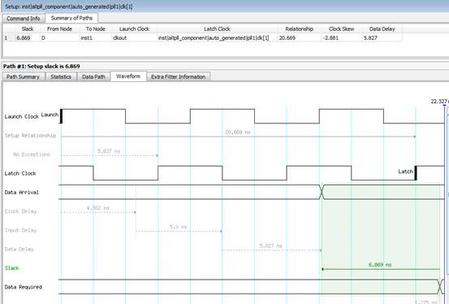

通过分析得出,违规路径有三个参数延时很大,分别是时钟延时,外部固有延时,数据输入延时。在一般情况中,外部固有延时是固定的,可更改的余地有限,主要是通过减小另外两个延时来达到时序收敛。这里假设另外两个延时也不可以更改,那么如何达到时序收敛呢?通过观察违规波形,发现如果使用锁存时钟的第3个时钟沿来锁存数据是可以满足时序收敛的,带来的影响就是必须对设计进行调整,使用锁存时钟的第3个时钟沿锁存的数据来进行后续处理,简单来说就是增加了有效数据的潜伏期。

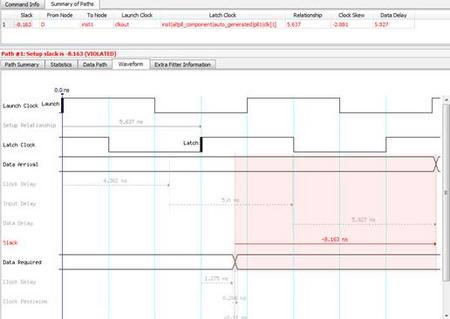

第4步,更改设计之后重新进行时序分析,这里必须使用多周期约束把设计意图告知TQ,使其能够进行正确的时序分析。采用的约束是:set_multicycle_path -from [get_clocks {clkout}] -to [get_clocks *] -setup -end 3。生效后重新检查结果,发现已经符合预期。

图4 时序已经收敛

(3) 问题总结

通过以上例子,总结一下使用TQ时应该注意的问题:

第一,使用TQ之前必须弄清楚相关概念的含义与他们之间的关系,比如Setup Time、Hold Time、Data Arrival Time、Data Required Time等概念,这样才能看懂TQ生成的波形图;

第二,先抽象出电路,再开始约束。约束对象往往比较复杂纷繁,先把其实际表达的电路,尤其是电路路径抽象出来,可以很好的辅助分析;

第三,开始约束之后,首先约束的内容必须是时钟,这些时钟包含由PLL直接产生的时钟以及各类派生时钟和虚拟时钟,只有时钟建立正确,后面的结果才有分析的价值与意义;

第四,约束必须符合设计意图,违背设计意图的约束即使达到了时序收敛,也毫无意义。这里以上面的多周期约束为例,通过分析违规时序可知必须更改设计,完成修改之后,必须把这一设计意图通过多周期约束告知TQ,使其按设计意图进行约束,否则TQ还会按默认的“单周期”进行约束,结果就是无论如何都不能达到时序收敛。

/2

/2

用户422852 2015-10-30 11:33