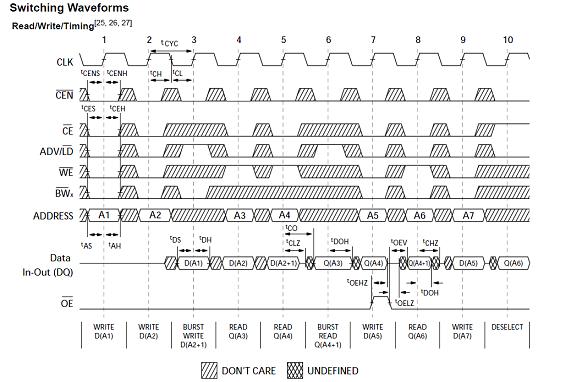

同步SRAM即是与时钟同步运行的SRAM,其地址的提取以及数据的输出全部是与时钟同步的。本例中用的SRAM为Cypress 公司的1M x 18位的cy7c1372,包括20位地址总线,18位数据线,3为片选,1位时钟输入,1位写使能,2为字节选择,1位异步输出使能,还有一些是突发模式下用到的信号线,这里就不再介绍了。以上各个信号都是基于时钟的上升沿被采样的。可见对于同步SRAM的时序约束分析,主要还是对时钟相移的约束,时钟相移约束好了,其他的可以根据时序分析结果报告,稍微的修改约束下就好了。本例为SRAM的普通读写模式,其时序图如下:

图1 SRAM读写时序图

图片不是很清楚,可以参考datasheet, 其中tAS , tAH为地址的建立保持时间,tDS ,tDH为数据的建立保持时间 。 tCO 为时钟上升沿触发后,有效数据输出延时时间。tDOH 为时钟上升沿触发后,当前数据的保持时间。

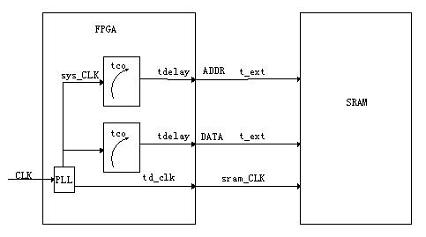

本例中工作时钟为50MHz。时序余量还是比较大的。首先分析往SRAM里面写数据,这种情况下,其信号路径还是比较简单的,在FPGA里同时产生地址和数据信号,再放送给SRAM,其模型如下:

图2 写SRAM模型

只要保证以下两个公式成立就可以了:

(sram_CLK 相对于 sys_CLK 的相移 + td_clk + sram_CLK)-(tco+tdelay+t_ext)< tAS 和 tDS

(sram_CLK 对于sys_CLK 的相移 + td_clk + sram_CLK+Tclk)-(tco+tdelay+t_ext)> tAH 和 tDH

其中Tclk为时钟周期。这里为20ns。

由以上两个公式容易看出,sram_CLK相对于sys_CLK的相移应该为负,既sram_CLK比sys_CLK要晚点触发。由于时钟周期高达20ns,所以以上两个公式还是很容易满足的。在没有做别的约束下,只设个偏移值,基本上在2ns和18ns的偏移情况下都能满足要求。当然具体情况下会有点区别。

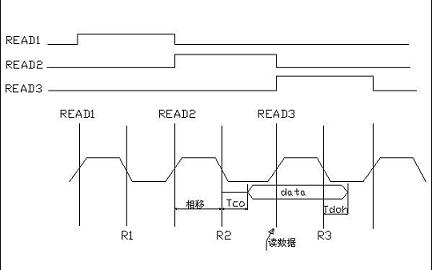

再分析下读取SRAM数据的情况。建立一个读模型的时序图:

图3 读SRAM数据模型

其中READ1,READ2,READ3是系统时钟sys_CLK触发的,R1,R2,R3是供给外部SRAM的时钟sram_CLK触发的。根据图1 SRAM读写时序图,可以看出sram在读信号触发后,延时两个时钟周期,数据线上才有数据,这时候FPGA才可以去读取数据。

根据图3,在R1处触发读sram数据,只有在R3处,数据才有效。而相对于FPGA,读有效数据并不一定出现在READ3处,这里就要看这个相移。要满足FPGA可以在READ3处读取数据,必须下面公式:

相移 + Tco + t_ext + FPGA内部的一些走线延时 + FPGA内部寄存器建立时间< Tclk

相移 + Tdoh > t_ext + FPGA内部的一些走线延时 + FPGA内部寄存器建立时间

可见相移不能太大,也不能太小,太大太小都不能在READ3处读取到正确的数据。具体值可以通过上面两个公式可以得出,由于写SRAM的时序余量比较大,满足上面两公式的相移值,基本上也能满足写SRAM的时序要求。FPGA内部的一些走线延时是通过对I0进行时序约束得到的。这个以后有时间再讨论。

/5

/5

用户1000403 2012-4-18 11:26