用SignalTapII测量时钟频率<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

昨日写了一个串口波特率发生器,写好下到板子上后因为身边没有任何可以测频率的仪器,无法实际测量应验,于是我想到何不用SignalTapII 逻辑分析仪一试?

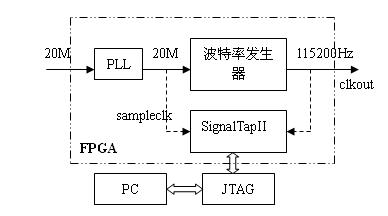

整个系统的框图如下所示:

图1:系统总体框图

SignalTapII从波特率发生器的输出115200Hz处采样,采样时钟设为PLL的输出20M,由逻辑分析仪的界面捕获到如下波形:

图2:clkout处采样到的波形

测量相邻两个上升沿间的采样个数:

图3:图2中256位置附近放大波形

图4:图2中512位置附近放大波形

由上三图可算出clkout每周期含454-284=170个采样点,因为采样时钟是20M,所以clkout的输出频率为20000000/170=117647Hz,与设计频率输出值115200Hz的相对误差约为2%。

需要说明的是,以上输出频率的计算方法是以假定clkout每周期均含170个采样点为前提的,事实上,每个周期的采样点并不都是170,而是在这个值上小范围的上下波动,这是由波特率产生器(即分频器)设计原理决定的。

因此,用这种方法测得的频率不具备统计意义,但可以粗略估计时钟的频率。当被测信号频率较高时,对采样时钟会提出更高的要求。

/3

/3

文章评论(0条评论)

登录后参与讨论