关于飓风II的资料

http://www.altera.com.cn/support/devices/cyclone2/dev-cyclone2.html

Altera存储

存储分为内部和外部

Cyclone 内部有M4K存储,接口支持SDRAM等外部存储

外部flash存储器一般有SPI接口和并行接口,又分norflash和nandflash。

内部存储:

Cyclone®II devices feature embedded memory structures to address the

on-chip memory needs of FPGA designs.

The embedded memory structure consists of columns of M4K memory blocks that can be

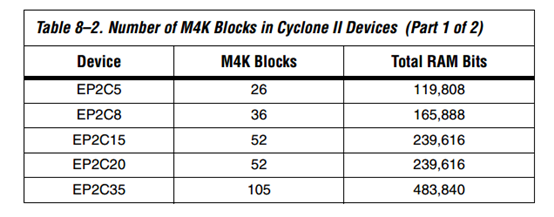

configured to provide various memoryfunctions such as RAM, first-in first-out (FIFO) buffers, and ROM. M4K memory blocks provide over 1 Mbit of RAM at up to 250-MHz operation (see Table 8–2 on page 8–2for total RAM bits per density).

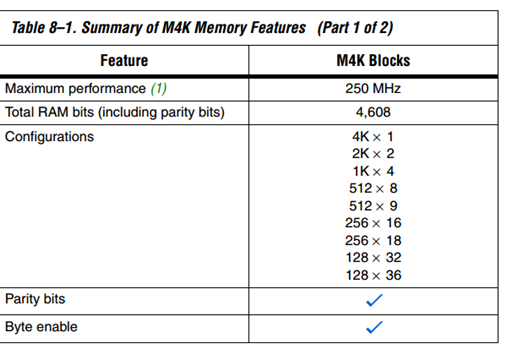

The M4K blocks support the following features:

■ Over 1 Mbit of RAM available without reducing available logic

■ 4,096 memory bits per block (4,608 bits per block including parity)

■ Variable port configurations

■ True dual-port (one read and one write, two reads, or two writes)

operation

■ Byte enables for data input masking during writes

■ Initialization file to pre-load content of memory in RAM and ROM

modes

■ Up to 250-MHz operation

不同型号器件 ram块

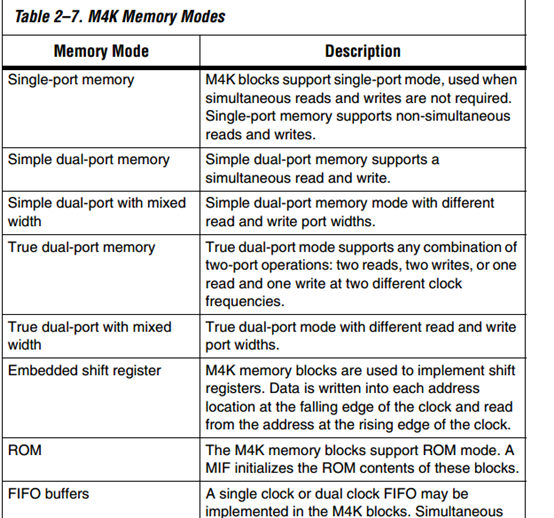

其中内部M4K支持以下模式

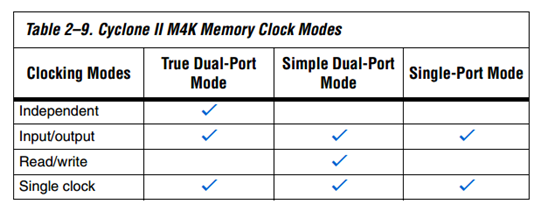

支持的时钟模式

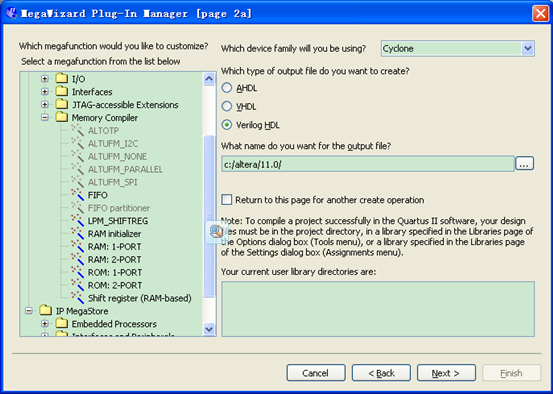

可用quartus进行配置

外部RAM(不涉及sram)

Altera官网-外部存储器接口设计向导

http://www.altera.com.cn/literature/lit-external-memory-interface.jsp

表1列出了Altera 器件支持的外部存储器接口。使用我们的外部存储器接口规格估算器获得更多信息。

|

表 1. Altera FPGA支持的外部存储器接口 | |||||||||

|

器件 |

存储器类型 | ||||||||

|

DDR4 |

DDR3 SDRAM |

DDR2 SDRAM |

LPDDR3 |

LPDDR2 |

RLDRAMII |

RLDRAMIII |

QDRII SRAM |

QDRII+ SRAM | |

|

Arria 10 |

2,666 Mbps |

2,133 Mbps |

800 Mbps |

1,600 Mbps |

800 Mbps |

1,067 Mbps |

2,400 Mbps |

1,400 Mbps |

1,266 Mbps |

|

Stratix V (1) |

- |

1,866 Mbps |

1,066 Mbps |

- |

- |

1,067 Mbps |

1,600 Mbps |

1,400 Mbps |

2,200 Mbps |

|

Stratix IV |

- |

1,066 Mbps |

800 Mbps |

- |

- |

1,067 Mbps |

- |

1,400 Mbps |

2,200 Mbps |

|

Stratix III |

- |

1,066 Mbps |

800 Mbps |

- |

- |

800 Mbps |

- |

1,400 Mbps |

1,600 Mbps |

|

Stratix II 和 Stratix II GX |

- |

- |

667 Mbps |

- |

- |

600 Mbps |

- |

1,200 Mbps |

1,200 Mbps |

|

Arria V (1) |

- |

1,334 Mbps |

800 Mbps |

- |

800 Mbps |

800 Mbps |

- |

1,600 Mbps |

1,600 Mbps |

|

Arria V GZ |

- |

1,600 Mbps |

800 Mbps |

- |

- |

700 Mbps |

1,334 Mbps |

1,400 Mbps |

2,000 Mbps |

|

Arria II GZ |

- |

800 Mbps |

666 Mbps |

- |

- |

700 Mbps |

- |

1,200 Mbps |

1,400 Mbps |

|

Arria II GX |

- |

800 Mbps |

666 Mbps |

- |

- |

- |

- |

1,000 Mbps |

1,000 Mbps |

|

Cyclone V (1) |

- |

800 Mbps |

800 Mbps |

- |

667 Mbps |

- |

- |

- |

- |

|

Cyclone IV |

- |

- |

400 Mbps |

- |

- |

- |

- |

668 Mbps |

- |

|

Cyclone III LS |

- |

- |

333 Mbps |

- |

- |

- |

- |

600 Mbps |

- |

|

Cyclone III |

- |

- |

400 Mbps |

- |

- |

- |

- |

668 Mbps |

- |

|

HardCopy IV |

- |

1,067 Mbps |

667 Mbps |

- |

- |

800 Mbps |

- |

1,200 Mbps |

1,400 Mbps |

|

HardCopy III |

- |

800 Mbps |

667 Mbps |

- |

- |

800 Mbps |

- |

1,200 Mbps |

1,400 Mbps |

注释

1. 所有数值为预测值。Arria V和Cyclone V仅支持单排LPDDR2 SDRAM

相关链接

· 查看外部存储器接口手册

· 下载 Board Skew Parameter Tool (XLS)

· 注册教师指导培训: 采用Altera® FPGA连接外部存储器

关于存储器英文介绍

Altera' External Memory Interface Spec Estimator, a parametric tool, allows you to find and compare the performance of the supported external memory interfaces in our FPGA devices. You’ll have the ability to filter down to specific performances based on your own search specifications, and then compare performances across FPGA devices side-by-side by filtering the criteria you choose for analysis. The External Memory Interface Spec Estimator supports DDR3 SDRAM, DDR2 SDRAM, DDR SDRAM, LPDDR2 SDRAM, RLDRAM 3, RLDRAM II, QDR II+ SRAM, and QDR II SRAM interfaces.

根据外部存储器控制器选型FPGA

http://www.altera.com/technology/memory/estimator/mem-emif-index.html#

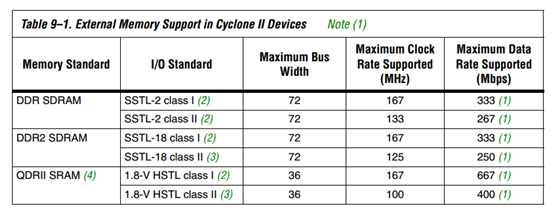

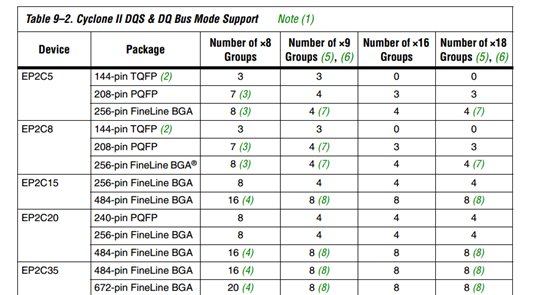

Cyclone II系列外部存储控制能力:

Cyclone® II devices support a broad range of external memory interfaces,

such as SDR SDRAM, DDR SDRAM, DDR2 SDRAM, and QDRII SRAM.

Dedicated clock delay control circuitry allows Cyclone II devices to

interface with an external memory device at clock speeds up to

167 MHz/333 Mbps for DDR and DDR2 SDRAM devices and

167 MHz/667 Mbps for QDRII SRAM devices. Although Cyclone II

devices also support SDR SDRAM, this chapter focuses on the

implementations of a double data rate I/O interface using the hardware

features available in Cyclone II devices and explains briefly how each

memory standard uses the Cyclone II features.

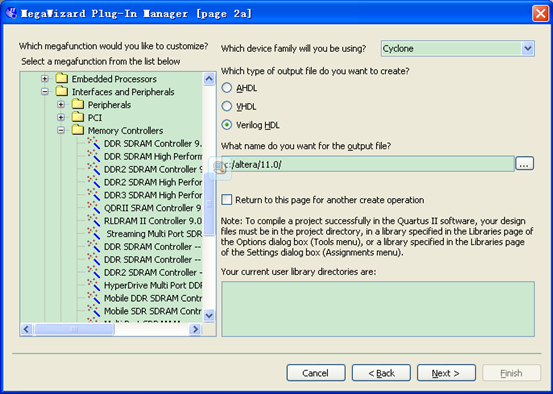

使用altera的IP核可以很方便的实现外部存储器控制

external memory IP cores listed below.

■ DDR2 SDRAM Controller MegaCore®

Function

■ DDR SDRAM Controller MegaCore Function

■ QDRII SRAM Controller MegaCore Function

这里只列举基本功能,后续将继续学习

详细参数参考

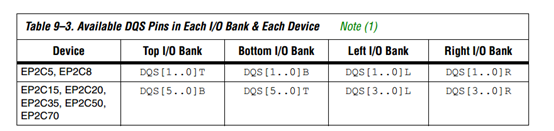

Handbook 第三部分MEMORY 第9节

emi_intro_specs_select_memory_CH.pdf 存储器设计

111

/5

/5

文章评论(0条评论)

登录后参与讨论