推荐两篇不错的参考文章:

http://wenku.baidu.com/view/08dcbd365727a5e9856a619c.html

http://wenku.baidu.com/view/a658888984868762caaed526.html

更多资料可擦考sdram厂商数据手册

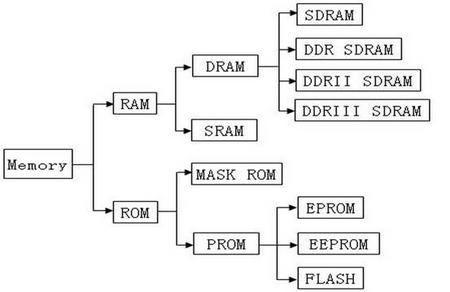

存储分类

SDRAM:Synchronous Dynamic Random Access Memory,即同步动态随机存取存储器。“同步”是指其时钟频率与CPU前端总线的系统时钟频率相同,并且内部命令的发送与数据的传输都以此频率为基准;“动态”是指存储阵列需要不断的刷新来保证所存储数据不丢失;“随机”是指数据不是线性一次存储,而是自由指定地址进行数据的读写。

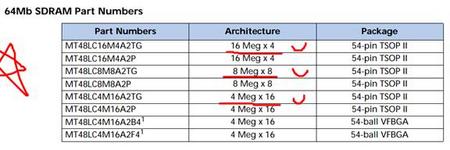

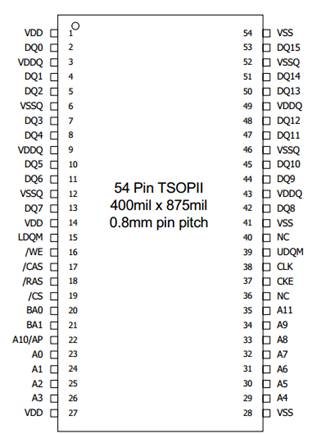

SDRAM数据线接口有4位 8位 16位 32位和64位的根据需要选择不同的芯片比如

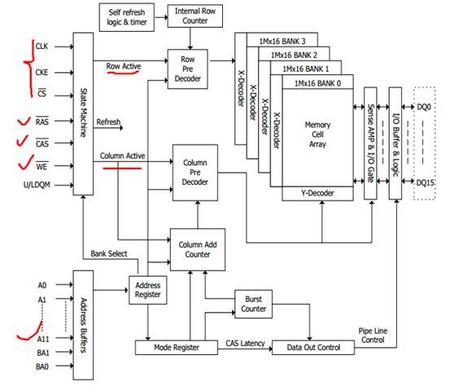

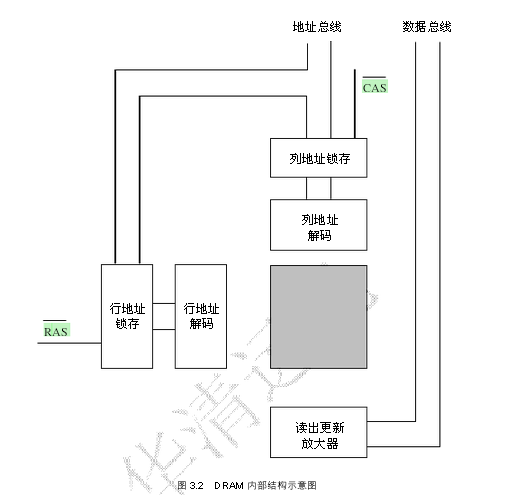

SDram内部构成(HY57V641620ETP-6 64MBIT 4M*16bit 166Mhz)

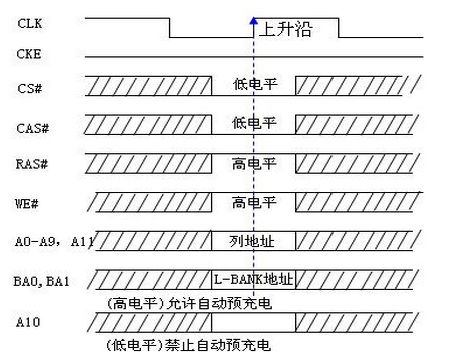

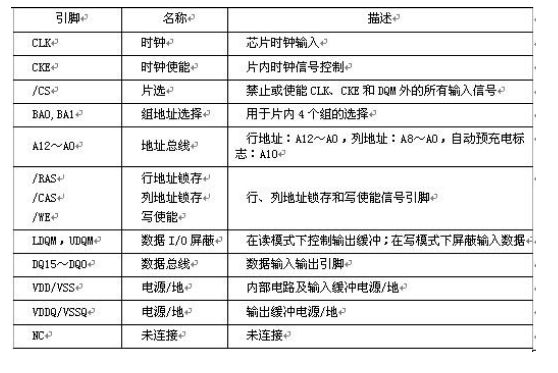

控制信号 CLK CS CKE RAS CAS WE DQM

行列地址输入信号A0---A11 bank选择信号 B0 B1

地址解码器,计数器

Bank存储颗粒

数据输出IO

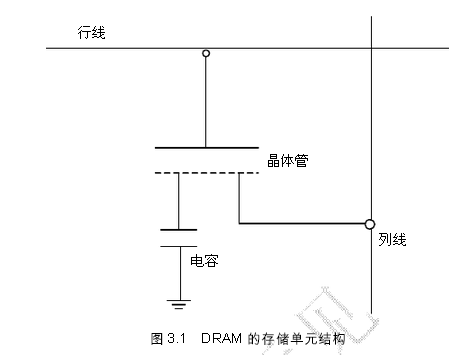

上图只是DRAM一个基本单位的结构示意图,电容器的状态决定了这个DRAM单位的逻辑状态是1还是0。一个电容器可以存储一定量的电子或者电荷。一个充电的电容器被认为是逻辑上的1,而“空”的电容器则是0。但是电容器被利用的这个特性也是它的缺点。因为电容器不能持久地保持存储的电荷,所以内存需要不断定时刷新,才能保持暂存的数据。电容器可以由电流来充电(当然这个电流是有一定限制的,否则会把电容击穿);同时电容的充放电需要一定的时间,虽然对于内存基本单位中的电容来说这个时间很短,大约只有0.18~0.2μs,但是这个期间内存是不能执行存取操作的。

DDR SDRAM:Double Data Rate SDRAM,即双倍速率SDRAM,普通SDRAM只在时钟信号的上升沿采样数据,而DDR SDRAM在时钟信号的上升沿和下降沿都采样数据,这样,在时钟频率不变的情况下,DDR SDRAM的数据存取速度提高了一倍,所以叫双倍速率SDRAM。

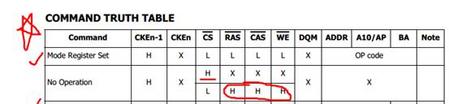

SDRAM的初始化(重要)

数据手册讲的很详细

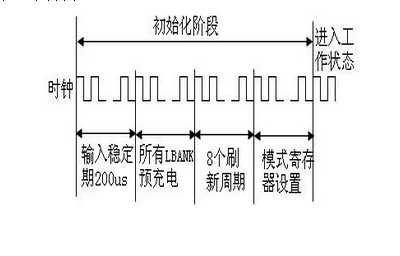

The recommended power-up sequence for SDRAMs:

1. Simultaneously apply power to VDD and V DDQ.

2. Assert and hold CKE at a LVTTL logic LOW since all inputs and outputs are LVTTL-compatible.

3. Provide stable CLOCK signal. Stable clock is defined as a signal cycling within timing

constraints specified for the clock pin.

4. Wait at least 100µs prior to issuing any command other than a COMMAND INHIBIT

or NOP.

5. Starting at some point during this 100µs period, bring CKE HIGH. Continuing at least

through the end of this period, 1 or more COMMAND INHIBIT or NOP commands

must be applied.

6. Perform a PRECHARGE ALL command.

7. Wait at least tRP time; during this time NOPs or DESELECT commands must be given.

All banks will complete their precharge, thereby placing the device in the all banks

idle state.

8. Issue an AUTO REFRESH command.

9. Wait at least tRFC time, during which only NOPs or COMMAND INHIBIT commands

are allowed.

10. Issue an AUTO REFRESH command.

11. Wait at least tRFC time, during which only NOPs or COMMAND INHIBIT commands

are allowed.

12. The SDRAM is now ready for mode register programming. Because the mode register

will power up in an unknown state, it should be loaded with desired bit values prior to

applying any operational command. Usin g the LOAD MODE REGISTER command,

program the mode register. The mode register is programmed via the MODE REGIS-TER SET command with BA1 = 0, BA0 = 0 and retains the stored information until it is

programmed again or the device loses power. Not programming the mode register

upon initialization will result in default settings which may not be desired. Outputs

are guaranteed High-Z after the LOAD MO DE REGISTER command is issued. Outputs

should be High-Z already before the LOAD MODE REGISTER command is issued.

13. Wait at least

t

MRD time, during which only NOP or DESELECT commands are

allowed.

At this point the DRAM is ready for any valid command.

Note: If desired, more than two AUTO REFRESH commands can be issued in the sequence.

After steps 9 and 10 are complete, repeat them until the desired number of AUTO

REFRESH + tRFC loops is achieved.

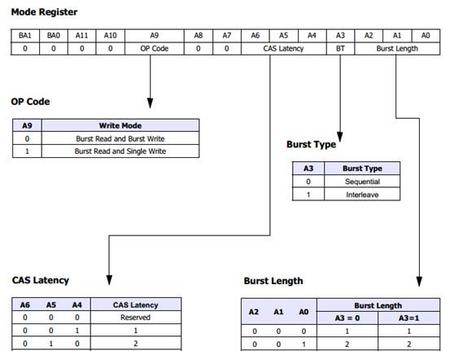

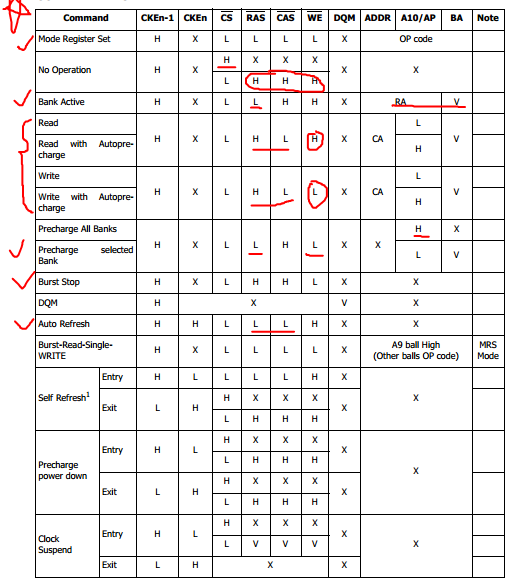

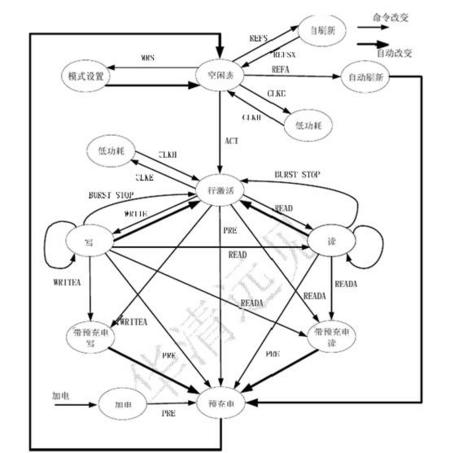

SDRAM的运行模式(配置参数):

包括突发长度(BL)、突发类型(Burst Type)、CAS延迟(CAS Latency)、运行方式(Operating Mode)和写入突发模式。

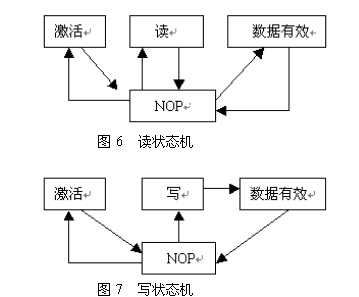

读写sdram之前需要先选择要读写的行和bank (有时称为激活 打开行)

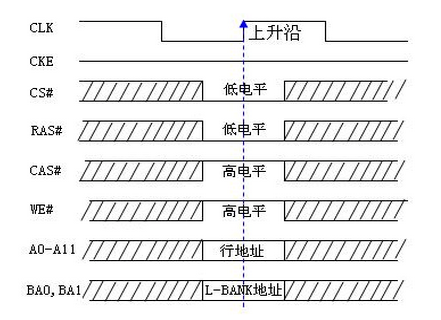

行有效(激活/打开行)

初始化完成后,要想对一个L-Bank中的阵列进行寻址,首先要确定行(Row),使之处于活动状态(Active),然后再确定列。虽然之前要进行片选和L-Bank的地址,但它们与行有效可以同时进行。通一个L-Bank中,两个相邻的Active命令之间的时间间隔被定义为 tRC,在不同L-Bank中,执行两个Active命令之间的时间间隔被定义为tRRD(RAS to RAS Delay)。行有效时序图如下所示。

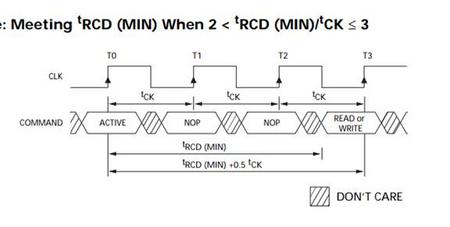

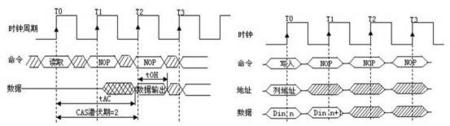

列读写 行地址确定之后,就要对列地址进行寻址了。在SDRAM中,行地址与列地址线是共用的,仍然是A0-A11。读/写命令是通过WE#信号的状态去区分的,当WE#为低电平有效时是写命令,为高电平无效时是读命令。列寻址信号与读写命令是同时发出的。虽然列地址线与行寻址共用,但是CAS(Column Address Strobe,列地址选通脉冲)信号则可以区分开行与列寻址的不同。列读写时序如图所示.

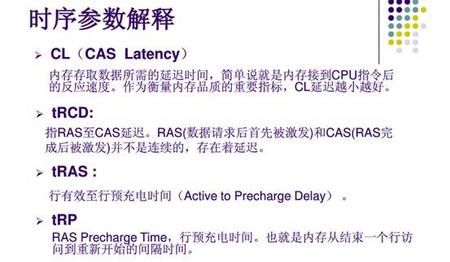

在发送列读写命令时必须要与行有效命令有一个间隔,这个间隔被定位为tRCD,即RAS to CAS Delay(RAS 至CAS延迟),大家也可以理解为行选通周期。tRCD时SDRAM的一个冲要时序参数,可以通过主板BIOS经过北桥芯片进行调整,但不能超过厂商的预定范围。广义的tRCD以时钟周期为单位,比如tRCD=2,就代表延迟周期为两个时钟周期。

在选定列地址后,就已经确定了具体的存储单元,剩下的事情就是数据通过I/O通道输出到内存总线上了。但是在CAS发出之后,仍要经过一定的时间才能有数据输出,从CAS与读取命令发出到第一笔数据输出的这段时间,被定位为CL(CAS Latency,CAS潜伏期)。由于CL只在读取时出现,所以CL又被称为读取潜伏期(RL,Read latency)。

(在DRAM读取方式中,当一个读取周期结束后,CAS和RAS都必须失效,然后再进行一个回写过程才能进入到下一次的读取周期中。 )

由于芯片体积的原因,存储单元中的电容容量很小,所以信号要经过放大来保证其有效的识别性,这个放大/驱动工作由S-AMP负责,一个存储体对应一个S-AMP通道。但它要有一个准备时间才能保证信号的发送强度(事前还要进行电压比较以进行逻辑电平的判断),因此从数据I/O总线上有数据输出之前的一个时钟上升沿开始,数据就已传向S-AMP,经过一定的驱动时间最终传向数据I/O总线进行输出,这段时间被定位为tAC(Access Time from CLK,时钟触发后的访问时间)。tAC的单位是ns,并且需要小于一个时钟周期。下面为SDRAM读操作中CS与tAC关系示意图。

SDRAM的数据写入操作也是在tRCD之后进行,但此时没有CL,寻址方式跟读操作一样,只是在写操作时,WE#信号为低电平有效。下图为SDRAM写操作时序。从图中可以看出,由于数据信号由控制端发出,输入时芯片无需做任何调校,只需直接传到数据输入寄存器中,然后再由写入驱动器进行对存储器电容的充电操作,因此数据可以与CAS同时发送,也就是说写入延迟为0。不过,数据并不是即时地写入存储电容,因为选通三极管(就如读取时一样)与电容的充电必须要有一段时间,所以数据的真正写入需要一定的周期。为了保证数据的可靠写入,都会留出足够的写入/校正时间(tWR,Write Recovery Time),这个操作也被称作写回(Write Back)。tWR 至少占用一个时钟周期或再多一点。

突发长度 突发(Burst)是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输所涉及到存储单元(列)的数量就是突发长度(Burst Lengths,简称 BL)。

在目前,由于内存控制器一次读/写 P-Bank 位宽的数据,也就是 8 个字节,但是在现实中小

于8 个字节的数据很少见,所以一般都要经过多个周期进行数据的传输。

上文讲到的读/写操作,都是一次对一个存储单元进行寻址,如果要连续读/写就还要对当前存储单元的下一个单元进行寻址,也就是要不断的发送列地址与读/写命令(行地址不变,所以不用再对行寻址)。虽然由于读/写延迟相同可以让数据的传输在 I/O 端是连续的,但它占用了大量的内存控制资源,在数据进行连续传输时无法输入新的命令,效率很低(早期的 FPE/EDO 内存就是以这种方式进行连续的数据传输)。

为此,人们开发了突发传输技术,只要指定起始列地址与突发长度,内存就会依次地自动对后面相应数量的存储单元进行读/写操作而不再需要控制器连续地提供列地址。这样,除了第一笔数据的传输需要若干个周期(主要是之前的延迟,一般的是 tRCD+CL)外,其后每个数据只需一个周期的即可获得。在很多北桥芯片的介绍中都有类似于 X-1-1-1 的字样,就是指这个意思,其中的 X 代表就代表第一笔数据所用的周期数。

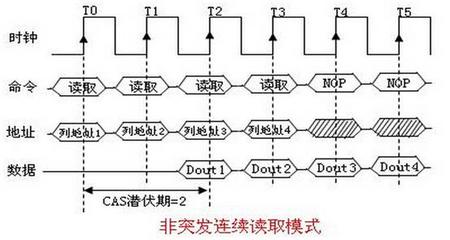

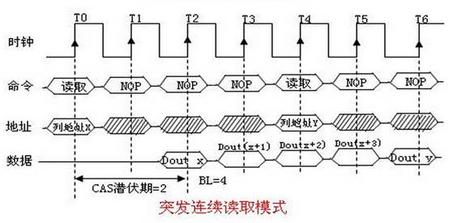

非突发连续读取模式:不采用突发传输而是依次单独寻址,此时可等效于 BL=1。虽然可以让数据是连续的传输,但每次都要发送列地址与命令信息,控制资源占用极大。突发连续读取模式:只要指定起始列地址与突发长度,寻址与数据的读取自动进行,而只要控制好两段突发读取命令的间隔周期(与 BL 相同)即可做到连续的突发传输。 至于 BL 的数值,也是不能随便设或在数据进行传输前临时决定。在上文讲到的初始化过程中的MRS 阶段就要对 BL 进行设置。目前可用的选项是 1、2、4、8、全页(Full Page),常见的设定是 4 和8。下图为突发连续读取模式与非突发连续读取模式时序对比图

预充电 由于 SDRAM 的寻址具体独占性,所以在进行完读写操作后,如果要对同一 L-Bank 的另一行进行寻址,就要将原来有效(工作)的行关闭,重新发送行/列地址。L-Bank 关闭现有工作行,准备打开新行的操作就是预充电(Precharge)。

预充电可以通过命令控制,也可以通过辅助设定让芯片在每次读写操作之后自动进行预充电。实际上,预充电是一种对工作行中所有存储体进行数据重写,并对行地址进行复位,同时释放 S-AMP(重新加入比较电压,一般是电容电压的 1/2,以帮助判断读取数据的逻辑电平,因为 S-AMP 是通过一个参考电压与存储体位线电压的比较来判断逻辑值的),以准备新行的工作。

在发出预充电命令之后,要经过一段时间才能允许发送 RAS 行有效命令打开新的工作行,这个

间隔被称为 tRP(Precharge command Period,预充电有效周期)。和 tRCD、CL 一样,tRP 的单位也是时钟周期数,具体值视时钟频率而定。

刷新 所以称为 DRAM,就是因为它要不断进行刷新(Refresh)才能保留住数据,因此它是 DRAM 最重要的操作。刷新操作与预充电中重写的操作一样,都是用 S-AMP 先读再写。

但为什么有预充电操作还要进行刷新呢?因为预充电是对一个或所有L-Bank 中的工作行操作,并且是不定期的,而刷新则是有固定的周期,依次对所有行进行操作,以保留那些久久没经历重写的存储体中的数据。但与所有 L-Bank 预充电不同的是,这里的行是指所有 L-Bank 中地址相同的行,而预充电中各 L-Bank 中的工作行地址并不是一定是相同的。

那么要隔多长时间重复一次刷新呢?目前公认的标准是,存储体中电容的数据有效保存期上限是64ms(毫秒,1/1000 秒),也就是说每一行刷新的循环周期是 64ms。这样刷新速度就是:行数量/64ms。我们在看内存规格时,经常会看到 4096 Refresh Cycles/ 64ms 或 8192

RefreshCycles/64ms 的标识,这里的 4096 与 8192 就代表这个芯片中每个 L-Bank 的行数。刷新命令一次对一行有效,发送间隔也是随总行数而变化,4096 行时为 15.625μs(微秒,1/1000 毫秒),8192 行时就为 7.8125μs。

刷新操作分为两种:自动刷新(Auto Refresh,简称 AR)与自刷新(Self Refresh,简称 SR)。不论是何种刷新方式,都不需要外部提供行地址信息,因为这是一个内部的自动操作。

对于 AR, SDRAM 内部有一个行地址生成器(也称刷新计数器)用来自动的依次生成行地址。

由于刷新是针对一行中的所有存储体进行,所以无需列寻址,或者说 CAS 在 RAS 之前有效。所以,AR 又称 CBR(CAS Before RAS,列提前于行定位)式刷新。

SR则主要用于休眠模式低功耗状态下的数据保存,这方面最著名的应用就是 STR(Suspend to

RAM,休眠挂起于内存)。在发出 AR 命令时,将 CKE 置于无效状态,就进入了 SR 模式,此时不再依靠系统时钟工作,而是根据内部的时钟进行刷新操作。在SR 期间除了 CKE 之外的所有外部信号都是无效的(无需外部提供刷新指令),只有重新使 CKE 有效才能退出自刷新模式并进入正常操作状态。

Refresh:就是刷新小电容的电量,电量来源于内存行列的一个旁路大电容。

Precharge:就是将旁路大电容预先充满电,以提供给小电容充电的电量。

数据掩码(DQM) 在讲述读/写操作时,我们谈到了突发长度。如果 BL=4,那么也就是说一次就传送 4×64bit 的数据。但是,如果其中的第二笔数据是不需要的,怎么办?还都传输吗?为了屏蔽不需要的数据,人们采用了数据掩码(Data I/O Mask,简称 DQM)技术。通过 DQM,内存可以控制 I/O 端口取消哪些输出或输入的数据。这里需要强调的是,在读取时,被屏蔽的数据仍然会从存储体传出,只是在“掩码逻辑单元”处被屏蔽。

DQM 由北桥控制,为了精确屏蔽一个 P-Bank 位宽中的每个字节,每个 DIMM 有 8 个 DQM 信

号线,每个信号针对一个字节。这样,对于 4bit 位宽芯片,两个芯片共用一个 DQM 信号线,对于 8bit 位宽芯片,一个芯片占用一个 DQM 信号,而对于 16bit 位宽芯片,则需要两个 DQM 引脚。SDRAM 官方规定,在读取时 DQM 发出两个时钟周期后生效,而在写入时,DQM 与写入命令一样是立即成效。

预存取 预存取概念是针对DDR SDRAM的。

SDRAM内存频率可细分为:数据频率、时钟频率和内核频率三种。对于普通SDRAM而言,这三

者相同,也就不存在预存取的概念。但是对于DDR而言,由于其在时钟信号的上升沿和下降沿都采样数据,所以其数据频率等于时钟频率的两倍,内核频率与时钟频率相同。DDR读操作时,需要在一个时钟周期内给I/O总线提供双倍数据量,实现这一功能的就是所谓的2倍预存取,其原理就是DDR SDRAM存储阵列的位宽增加一倍。这些数据被转化为宽度为1/2的两通道数据分流,分别从时钟信号的上升沿和下降沿发送出去。

DDR2的预存取能力为4位,也就是说其L-Bank的宽度是芯片位宽的四倍。此时,时钟频率是

内核频率的两倍,数据频率又是时钟频率的两倍。由此可见,DDR2在数据频率与DDR1相同的情况下,内核频率只有DDR1的一半。我们不要小看这个内核频率,其实它对内存的稳定性和可靠性非常重要,内核频率越低,意为着功耗越小,发热量越低,内存越稳定。实验证明,在目前的技术条件下,200MHz差不多是内存内核的极限频率。

DDR3有8位预存取能力,它的最大可支持1600MHz的数据存取速率,但是它的内核频率其实

也只有1600MHz/8=200MHz。时钟频率为:1600MHz/2=800MHz。

在《内存器件介绍之RAM篇(四)》中我们介绍了SDRAM的“突发长度”、“预充电” 、“刷新”、“数据掩码”以及DDR“预存取”等一些基本参数和概念。下面重点介绍下DDR、DDR2、DDR3的管脚功能和它们之间的差异。

初始化 上电之后外部产生Reset命令送给SDRAM控制器,SDRAM控制器由此进入初始化状态。对SDRAM进行初始化执行一系列操作,完成上电、预充电、自动刷新和模式寄存器设置,在进行Verilog程序设计时,可以通过状态机来实现这一过程。

1111

miaozengxue_503596631 2015-6-15 14:51

用户377235 2015-6-9 14:33

用户1199704 2015-6-8 12:59

用户377235 2015-6-1 18:53

用户377235 2015-6-1 09:03

2005jiangxu_694877046 2015-6-1 09:01

用户1442844 2015-5-30 23:01

saj 2015-5-30 08:45

用户377235 2015-5-30 01:15

用户1696924 2015-5-29 13:03