第一个工程的建立

我的环境:Window 7旗舰版 64位,Vivado 2014.1

目前,ISE开发环境已经停止了版本的更新,Vivado将在未来成为Xilinx开发的主导开发环境,而且它基于系统的开发环境和优化的综合编译算法都吸引着无数工程师们。这里我们以一个简单的计数器为例子开启Vivado开发的征程。

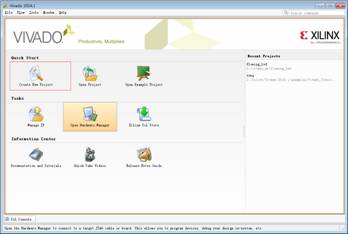

打开Vivado 2014.1集成开发环境:开始---所有程序---Xilinx Design Tools---Vivado2014.1--- Vivado2014.1。如下图所示

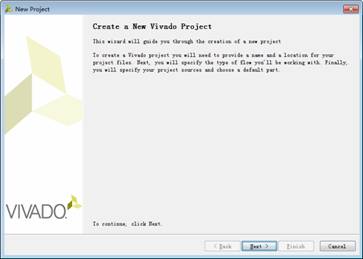

选择Quick Start—Create New Project,建立新工程,这时就会弹出工程向导,见下图

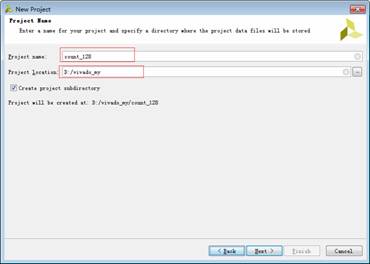

点击“Next”,在弹出的窗口中输入工程名和工程存储的位置。

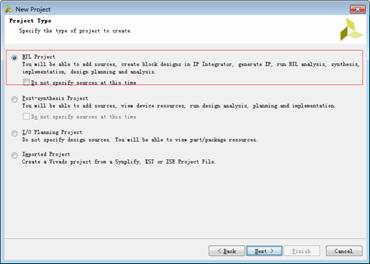

继续点击“Next“在弹出的窗口中选择第一项。

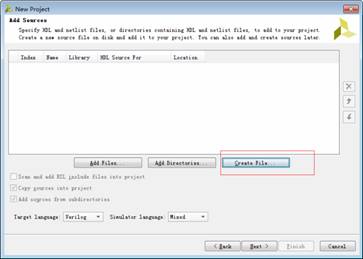

继续选择“Next“,弹出下图所示窗口,选择“Create File”

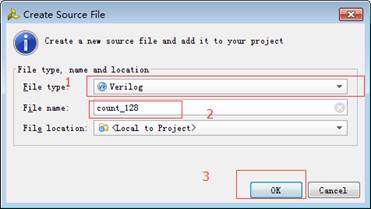

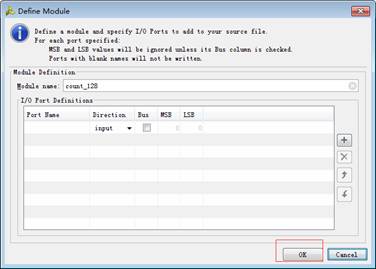

在弹出的的窗口中选择源文件类型,可以选择VHDL和Verilog HDL,我使用的是verilog HDL,并写上文件名,点击OK。

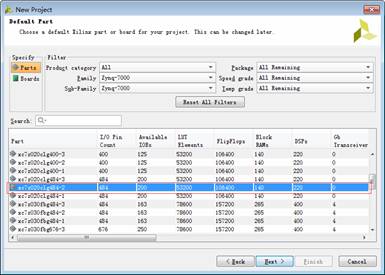

然后一直点击”Next”,直到出现下图芯片选择窗口:

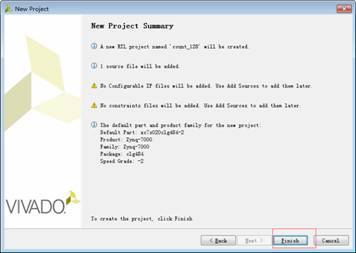

选择ZYNQ上芯片型号(这里我使用的是ZYNQ开发板),然后点击“Next”,在弹出的窗口中选择”Finish”。

直接点击OK。

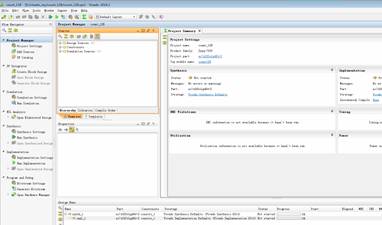

这样就建立了一个新的工程,如下图所示。

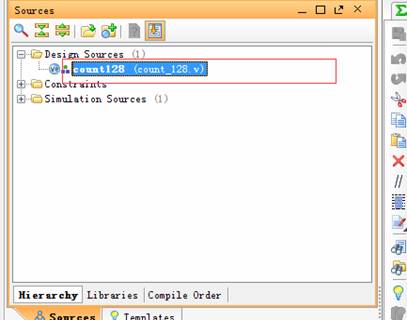

打开工程后,双击Project Manager的Source窗口中的verilog文件名(我这里是count_128),打开编辑界面

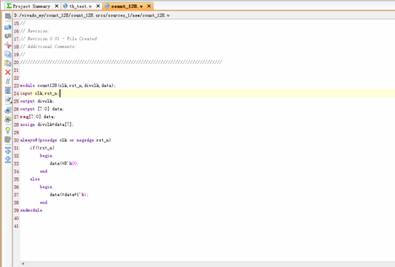

在编辑窗口输入计数器代码,如下图所示

其中的代码如下所示:

module count128(clk,rst_n,divclk,data);

input clk,rst_n;

output divclk;

output [7:0] data;

reg[7:0] data;

assign divclk=data[7];

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin

data<=8'h00;

end

else if( data == 127)

begin

data <= 0;

end

else

begin

data<=data+1'b1;

end

endmodule

到这里,我们的工程就建立完成了,并且有了一个verilog源文件。

/5

/5

用户1849145 2015-12-10 15:18