Vivado和ModelSim联合仿真

以前在使用Xilinx芯片时,用的开发环境都是ISE,最近做项目需要用到ZYNQ,就开始学习Vivado开发环境了,没办法,搞技术就得不断学习。Vivado是基于系统设计的开发环境,具有更加优秀的综合、布局布线算法,在进行系统设计时可以显著提高开发速度。虽然Vivado自带有功能强大的仿真工具Vivado Simulator,但是个人由于熟悉ModelSim环境,因此还是使用vivado与ModelSim进行联合仿真。我的环境:Window 7旗舰版 64位,Vivado 2014.1(C:\Xilinx\Vivado),Modelsim SE-64 10.1c(C:\modeltech64_10.1c\win64)。

一:编译仿真库

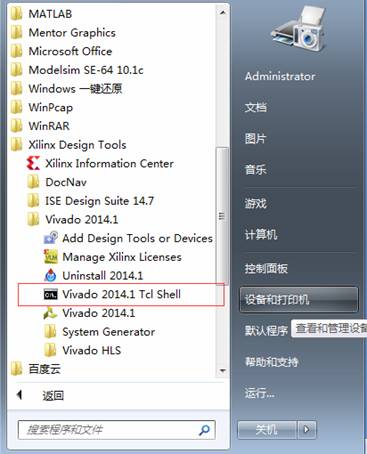

首先,打开编译库工具:开始---所有程序---Xilinx Design Tools---Vivado 2014.1--- Vivado 2014.1 Tcl Shell,如下图所示:

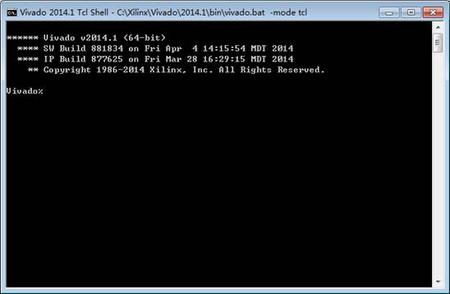

鼠标左键点击后,弹出Tcl脚步编辑器

在弹出的界面中输入下列格式的TCL脚本:

“compile_simlib -directory -simulator

-simulator_exec_path”(不含引号)

其中,表示编译后的库文件放置位置。

表示使用的仿真工具。(这里使用的是Modelsim)

表示Modelsim安装的位置。

一般而言,使用上述语句就足够了,如果还想使用别的语句请参看Xilinx的用户手册UG835,我的完整tcl语句是这样的:

“compile_simlib -directory D:/xilinx_sim_lib_vivado -simulator modelsim

-simulator_exec_path C:\modeltech64_10.1c\win64“(不含引号)

其中,D:/xilinx_sim_lib_vivado就是编译后,库文件放置的位置。C:\modeltech64_10.1c\win64是我电脑Modelsim安装的路径。

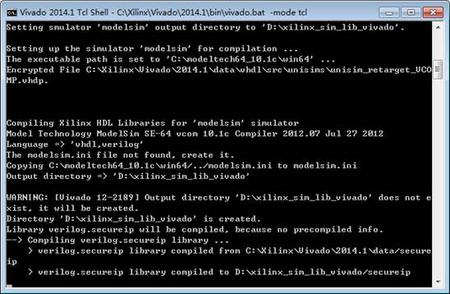

复制上述tcl命令,在界面中粘贴后显示下图所示界面,然后我们就耐心的等到半个小时左右!有时间可以去吃个饭了~~

经过漫长的等待,仿真库编译成功:

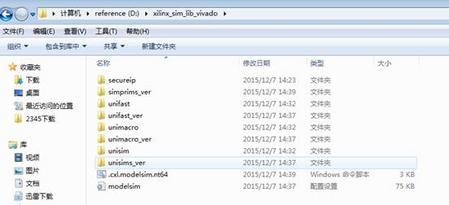

打开D:/xilinx_sim_lib_vivado文件夹可以发现,所有的库文件和Modelsim.ini文件均已生成。

二、关联设置

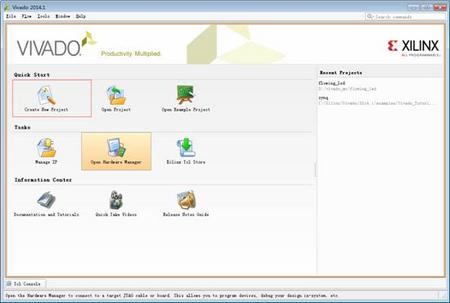

打开Vivado 2014.1集成开发环境:开始---所有程序---Xilinx Design Tools---Vivado2014.1--- Vivado2014.1。如下图所示

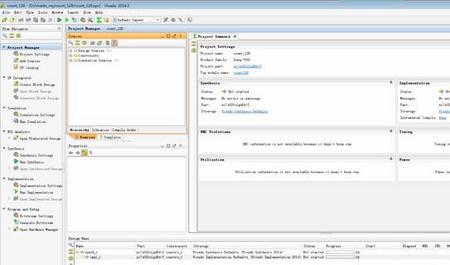

选择Quick Start—Create New Project,按照上一个文章的步骤,建立新工程,见下图

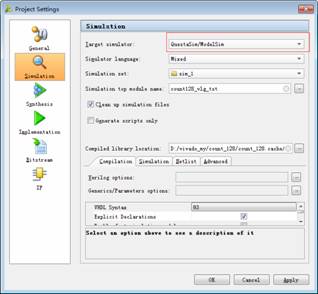

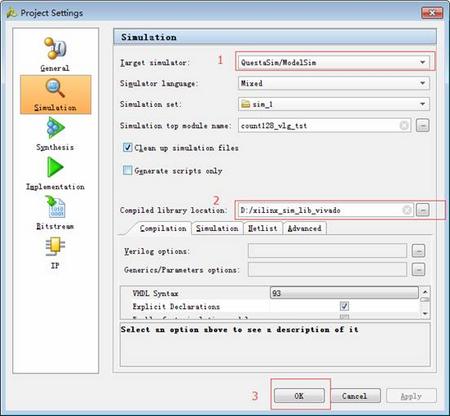

接下来,还需要进行仿真设置,选择流程向导中的Simulation—Simulation Setting

在弹出的窗口中, Simulation栏中,仿真工具选择“Target Simulation”选“QuestaSim Modelsim”

接着需要选择仿真库的路径,这个仿真库就是上节中花了半个小时编译的库,我的仿真库路径是D:/xilinx_sim_lib_vivado。

选择OK,就将Vivado2014.1和Modelsim10.1c关联在一起了。

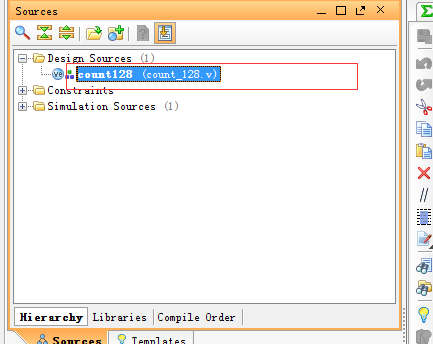

打开工程后,双击Project Manager的Source窗口中的verilog文件名(我这里是count_128),打开编辑界面

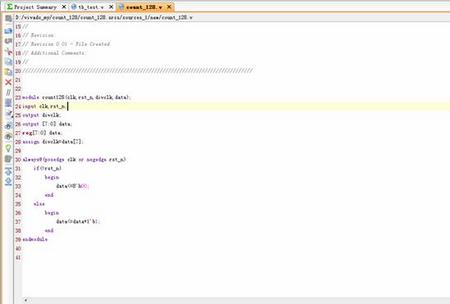

在编辑窗口输入计数器代码,如下图所示

其中的代码如下所示:

module count128(clk,rst_n,divclk,data);

input clk,rst_n;

output divclk;

output [7:0] data;

reg[7:0] data;

assign divclk=data[7];

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin

data<=8'h00;

end

else if( data == 127)

begin

data <= 0;

end

else

begin

data<=data+1'b1;

end

endmodule

接下来就是编写测试文件了。

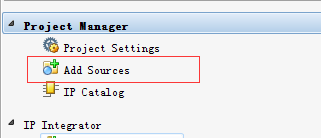

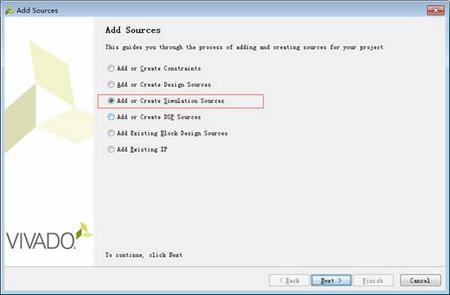

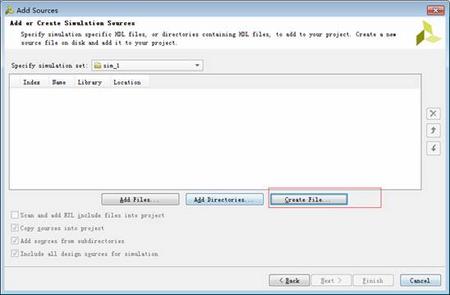

在文件管理区选择Add Sources,

然后新建仿真源文件,点击“Next”

在弹出的窗口中点击“Create File”,

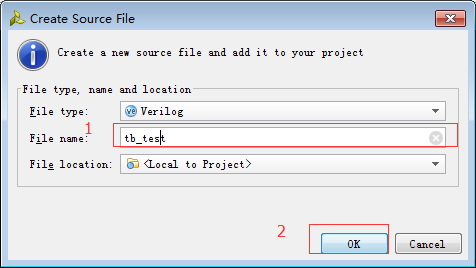

在弹出界面中输入仿真测试文件的文件名,然后点击OK。

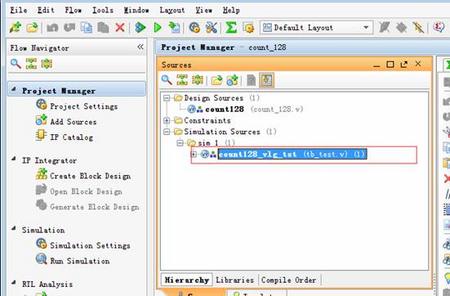

使用鼠标左键双击测试文件名,如下图所示

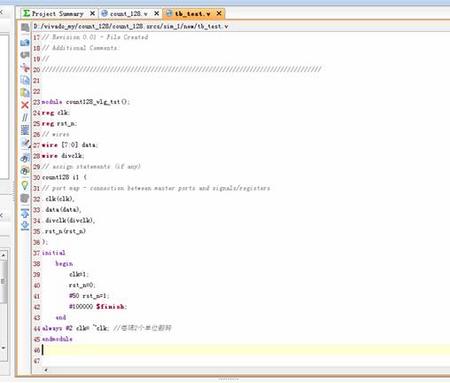

在弹出的tb_test编辑界面中输入下图所示源代码:

代码如下

module count128_vlg_tst();

reg clk;

reg rst_n;

// wires

wire [7:0] data;

wire divclk;

// assign statements (if any)

count128 i1 (

// port map - connection between master ports and signals/registers

.clk(clk),

.data(data),

.divclk(divclk),

.rst_n(rst_n)

);

initial

begin

clk=1;

rst_n=0;

#50 rst_n=1;

#100000 $finish;

end

always #2 clk= ~clk; //每隔2个单位翻转

endmodule

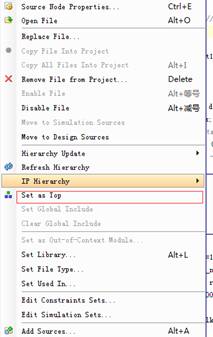

接下来,就是设置测试文件tb_text为顶文件。选中测试文件,然后点击右键,在弹出的窗口中选择“set as Top”。

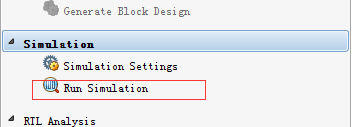

选择左侧向导中的Simulation-Run Simultaion,然后选择弹出的Run Behavioral Simulation项

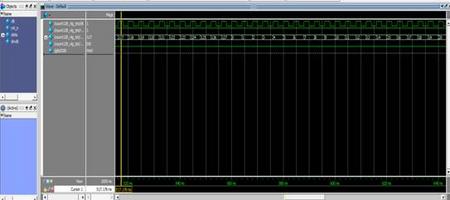

接着就会弹出ModelSim程序,结果如下图所示

/1

/1

文章评论(0条评论)

登录后参与讨论