简介

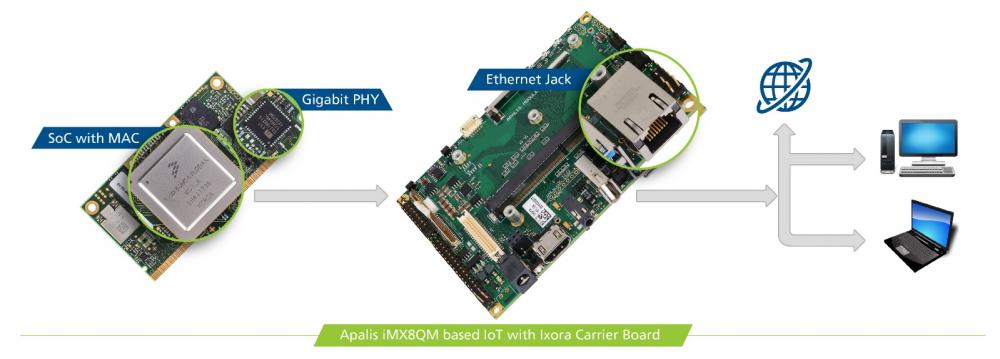

Toradex 供应稳健而可靠的嵌入式系统,它们被要求在严苛的环境能够不间断地运行。以太网是物联网 (IoT)的重要接口之一。我们将会查阅一些以太网标准并向您展示 Toradex 测试的合规情况。

在研究以太网标准之后,我们将会说明我们的测试配置、测试步骤和测试结果。 Colibri iMX6ULL 模块 和 Iris 载板 将被用于本次测试,如果您的验证流程同样需要这些测试,那么您可以将本测试作为定制化载板测试的一个模型。

为什么我们需要采用以太网标准并做一致性测试

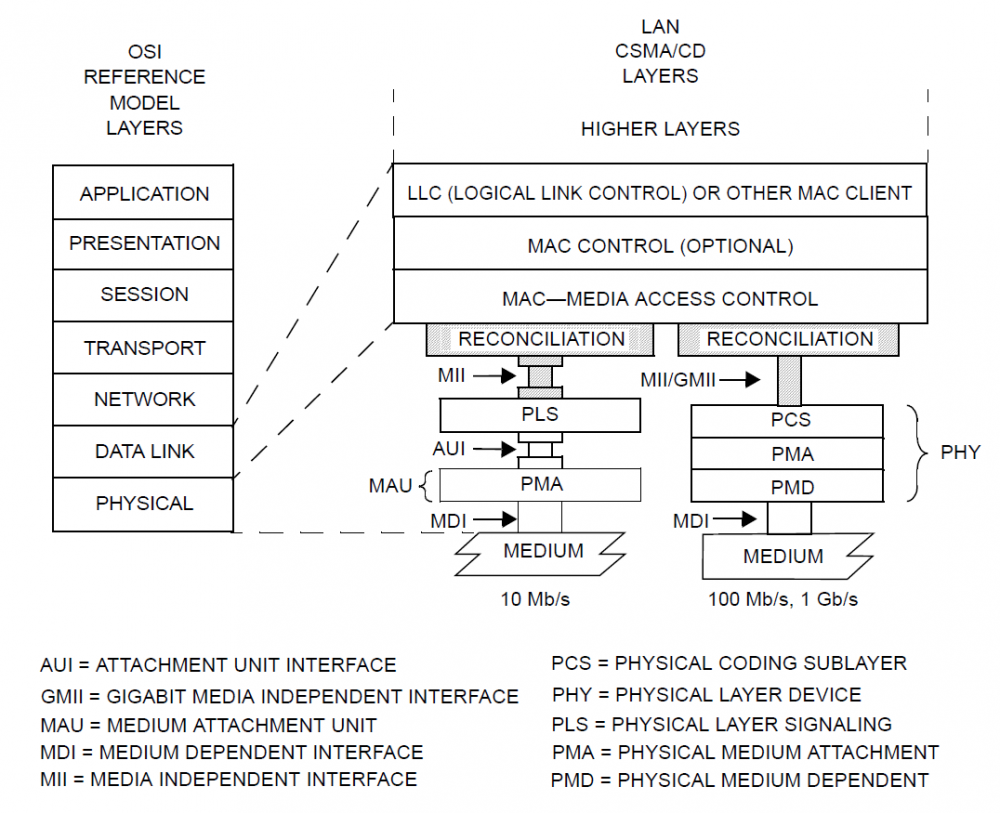

以太网设计遵循 IEEE 802.3 标准,其定义了 7 层 OSI 模型的物理和数据链路层。标准中规范了波形特征。依照该标准设计能够确保和全世界所有其他设备的兼容和交互。否则可能会出现传输问题和数据丢失。一致性测试保证设计能够符合标准。

除了在 IEEE 802.3 标准中规定的波形特征,University of New Hampshire InterOperability Laboratory (UNH-IOL) 也为这些信号提供标准的一致性测试流程。

可以在下面的链接中查看相关文档:

https://ieeexplore.ieee.org/browse/standards/get-program/page/series?id=68

https://www.iol.unh.edu/

以太网物理层基本知识

以太网标准有数千页之多,我们仅涉及一些最重要的概念和关键的术语。

图1 IEEE 以太网标准 OSI 参考模型

我们从物理介质开始。信号通常通过同轴双绞线达到我们载板上以太网接口,然后在阻抗匹配的 PCB 差分线路上继续传输至以太网 PHY 芯片。该设备为处理器将介质上的模拟信号转为数字信号,反之亦然。

电信号首先抵达作为物理层一部分的 PHY 的 Medium Dependent Interface (MDI)。不同的物理介质具有不同的特性。根据特定的介质种类,信号被传输并发送到OSI 的下一层数据链路层。在我们的 Colibri 模块上我们提供 10Base-T 和 100Base-TX (Fast Ethernet) ,Apalis 模块则为 1000Base-T。OSI 前两层之间的标准接口成为Media Independent Interface (MII) ,独立于物理层。

表1 Media Independent Interface 概览

MII | Media Independent Interface |

RMII | Reduced Media Independent Interface |

GMII | Gigabit Media Independent Interface |

RGMII | Reduced Gigabit Media Independent Interface |

SGMII | Serial Gigabit Media Independent Interface |

QSGMII | Quad Serial Gigabit Media Independent Interface |

XGMII | 10 Gigabit Media Independent Interface |

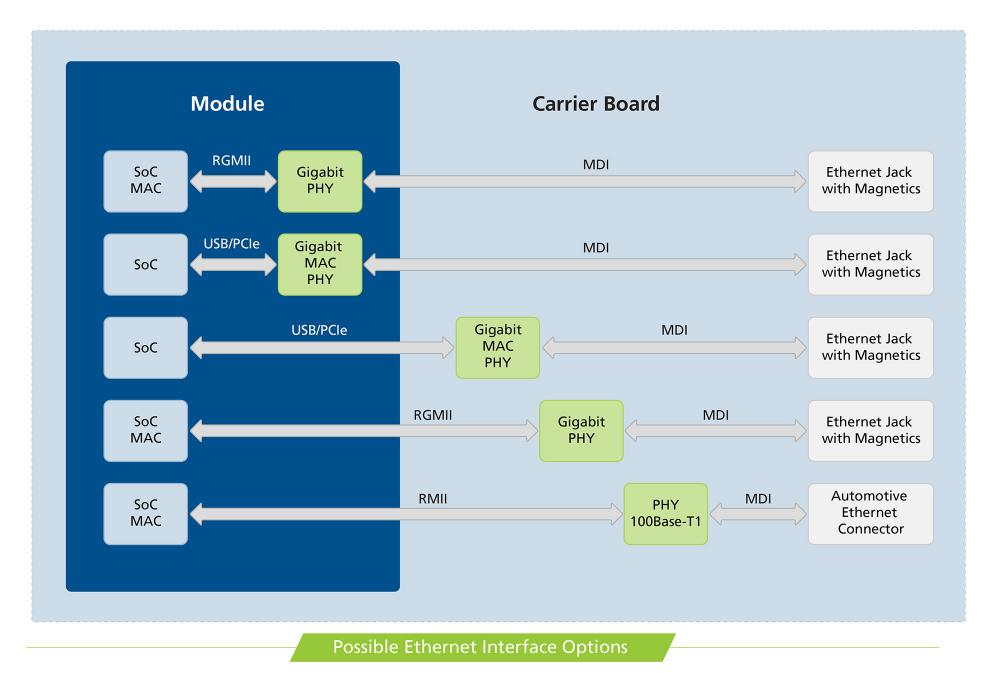

同时,我们将讨论高级的向后兼容的 Reduced Gigabit Media Independent Interface (RGMII) ,10 Gigabit 下一代接口已经命名为 XGMII。Reduced 意味着相同的标准仅需要更少的信号线。xMII 则是并行总线。出于管理目的,还有一个辅助的串行总线称为 Management Data Input/Output (MDIO)。 XMII 终止于 Media Access Control (MAC) 层。广为所知的 MAC 地址这里被用作唯一的标识。MAC 层可以被集成在处理器 SoC,如 NXP®处理器。然而它也可以嵌入到 同一个 PHY 芯片,这更多被叫作以太网控制器。太网控制器再通过诸如 USB 或者 PCIe 接口连接到 SoC。我们将不会讨论更高的 OSI 层以及 ARP、NDP、IP、TCP、UDP 等协议,这些都被组织成帧或者包,因为对于所有这些协议,在第一个物理层的电信号都是一样的!

现在我们再回到物理层。物理链路上有两个主要的特征我需要解释,分别是速度和双工模式。我们的模块在 Apalis 上最高支持 Gbit ,Colibri 为 100Mbit,以及半双工和全双工两种模式。在全双工模式下,两端的 PHY 可以同时和对方通信。对于半双工,PHY 不能同时接收和发送数据,需要借助 Carrier Sense Multiple Access with Collision Detection (CSMA/CD) 来避免冲突和控制数据流。

我们之前已经提到,Apalis 模块可以支持千兆以太网,但是对于通信的对方来说要如何才能知道以何种速度发送数据?自动协商流程因此产生,通信双方通过 16ms 链路脉冲来确定最好的连接。需要注意自动协商的设置,当通信双方配置为固定方式时会出现双工不匹配的问题。在电气方面,10Base-T 和 100Base-TX 物理层使用 2 对双绞线,1000Base-TX 使用 4 对。由于采用了比 10 MHz 更高的频率 62.5 MHz 和更密集的信号调制方案(PAM-3),100Base-TX 比 10Base-T 会更快。1000Base-TX 采用和 100Base-TX 一样的频率,但在 4 对双绞线上传输和采用更高的调制模式(PAM-5)。最后还有一个特性称为 EEE, Energy Efficient Ethernet。 该标准旨在节能。

https://www.analog.com/media/en/technical-documentation/application-notes/EE-269.pdf

https://en.wikipedia.org/wiki/Duplex_mismatch

https://en.wikipedia.org/wiki/Media-independent_interface

https://www.asix.com.tw/new_alias.php?alias=93&full=http://www.embedded.com/design/202804534

下图概括了在 Toradex 计算机模块上的几种以太网方案:

汽车级以太网

在我们继续一致性测试前,我想告诉你我们经常收到关于 100Base-T1 的问题,其更多被称作汽车级以太网。客户想要知道是否可以将汽车级以太网连接到快速以太网 PHY。 100Base-T1 拥有不同的物理层规范来满足更加严格的汽车环境需求。因此无法直接连接,但是 MII 确是相同的。所以解决方案是将 100Base-T1 PHY 直接连接到 SoC 的 Multimedia Independent Interface。因而必须选择一款将 xMII 引出到金手指的模块。当然,你也需要设计支持 100Base-T1 PHY 的定制载板。下面你可以找到将 xMII 引出到金手指的模块。请注意这不是标准的 Toradex 接口,模块模块的引进分配各不相同。

Apalis iMX8

Colibri iMX8X

Colibri iMX7

Colibri iMX6ULL

Colibri Vybrid

Toradex 模块以太网一致性测试

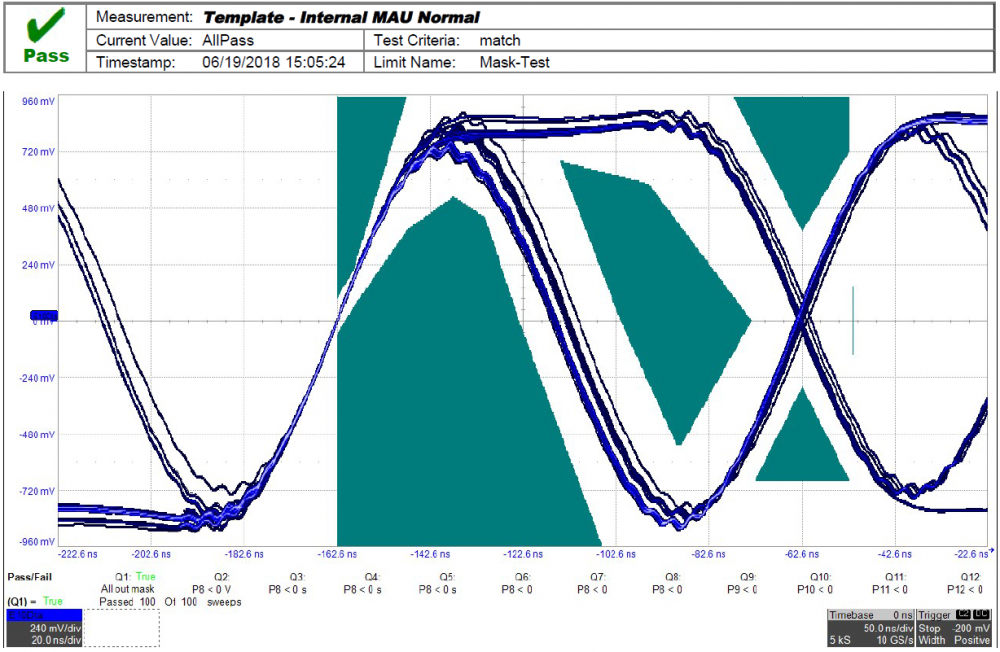

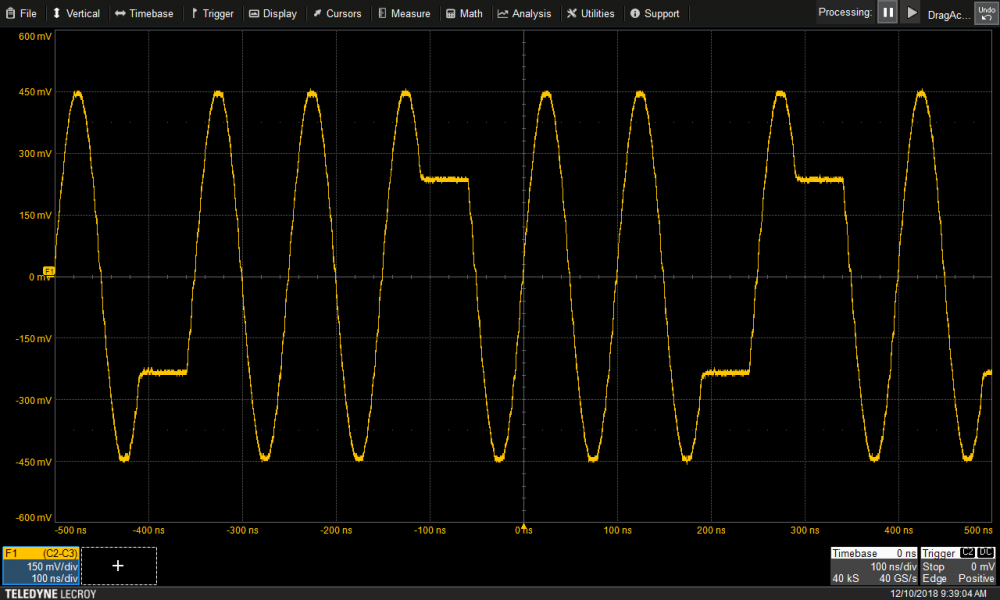

图 2 10Base-TX 测试:DOV Internal MAU Normal

在非常简短的概述后,我们继续一致性测试,我们将从时间和电压角度测量电气信号。如你在示波器里看到的,10/100/1000 Mbps 电信号看起来完全不一样并且有这不同的要求。

本次测试评估电压幅度、抖动值、上升/下降时间和其他信号特征。每一次测试需由 DUT 产生特定的测试信号,例如发送连续的伪随机信号。测试信号要求最简单方法就是定义一个测试模板。信号不能和模板相交从而满足规范。10Base-T 测试经常借助模板,如在第一个图看到的。我想提及一些值,差分输出峰值电压必须在 2.2V 和 2.8V 之间。差分输出电压谐波需要大于 27dB 并且抖动值小于 22ms。10Base-T 的双绞线模型很有意思,其会被用于一些一致性测试。通过基于集中元件的等效电路,可以为只使用被动元件的不同的传输因素建立模型。根据所使用的 PHY,10Base-T 一致性测试可能需要一个链路对端节点。你可以下载 Colibri iMX6ULL 测试报告 作为一个例子,从中你会发现所有的测试。

图 3 无负载 10Base-T 随机差分信号测量

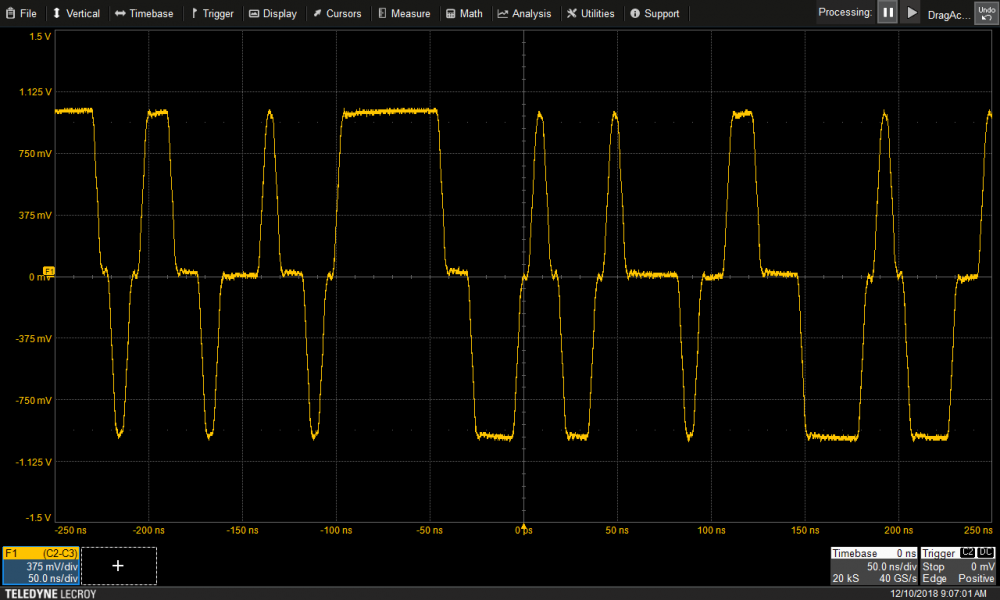

基于 3 级 MLT-3 电压信号,表 2 定义了100Base-TX 的接口特征。数据采用 4B5B 算法编码,由于强制发送一个信号,因此可以从数据流中恢复出时钟。对于我们的测试设备,一个伪随机测试模式(PRBS7)可以用于所有的测试。但是其他的一些测试只会在特定的模式触发并仅在特定值的时刻测量。

表 2 100Base-TX 接口特征

Characteristics | Min | Max | Unit |

UTP DOV Base to Upper/Lower | 950 | 1050 | mV |

Signal Amplitude Symmetry | 98 | 102 | % |

Rise/Fall Time | 3 | 5 | ns |

Rise/Fall Time Symmetry | 0 | 500 | ps |

Duty Cycle Distortion | -250 | 250 | ps |

Transmit Jitter | 0 | 1.4 | ns |

Overshoot | 0 | 5 | % |

图 4 100Base-TX 差分随机信号测量

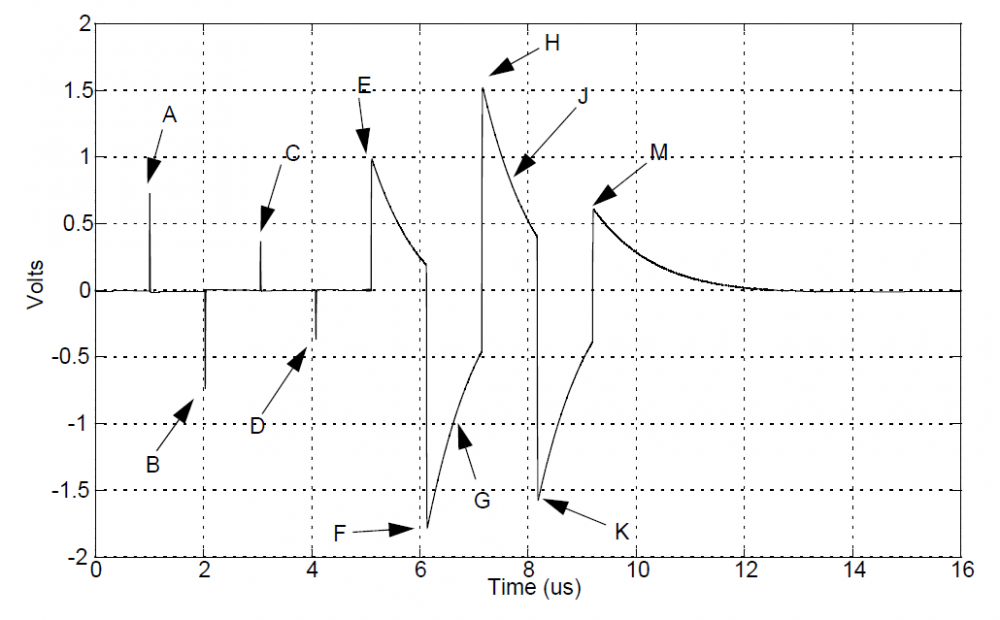

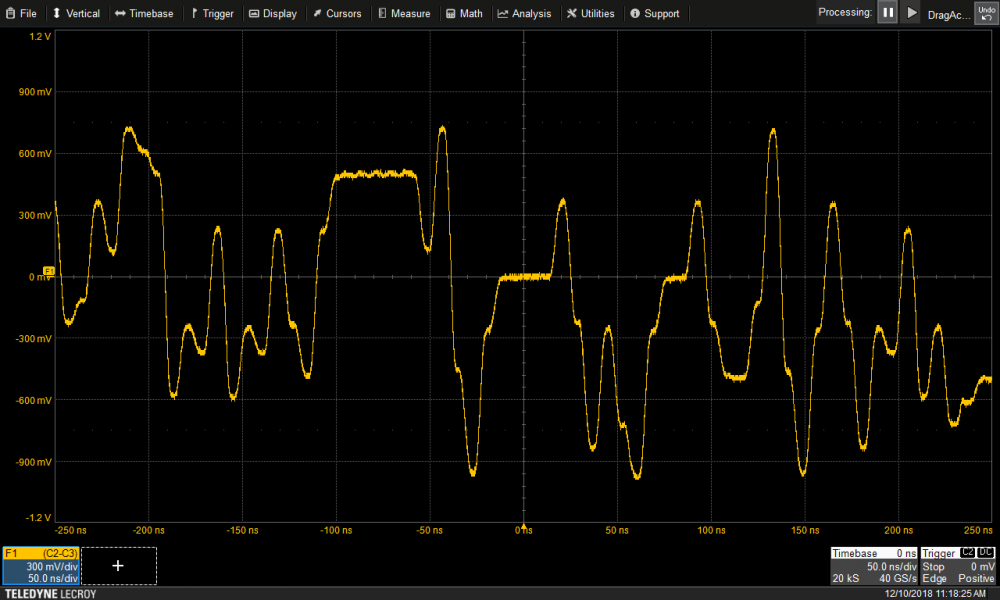

测试标准和 1000Base-T 定义的方法类似。我将不去列出它们。这些测试还需要引入 Arbitrary Waveform Generator (AWG) 形式的干扰源,用于创造 31.25MHz 和 20.833MHz 的干扰信号。在图 5 中你可以看到由 PHY 产生的测试模式 1 的测试图案。一共有 4 个测试图案,可以通过 PHY 的 MIDO 寄存器设置产生。请不要忘记我们需要进行 4 次一致性测试,因为有 4 对双绞线。

图 5 1000Base-T IEEE 以太网标准测试模式 1 波形定义

图 6 1000Base-T 无干扰差分测试模式 4 失真测试测量

我们现在已经看到一些电气要求必须被满足从而符合接口定义的一致性。在我们进一步研究测试设备之前,我想要尝试解决本博文中一个重要的问题:如何产生这些信号?

每个 PHY 厂商都有特定的方法修改相关的寄存器来进入测试模式。这通常不是公开的,你需要向你的 PHY 厂商咨询。Microchip 是一个很好的例子,他们自去年开始公开了一个关于以太网一致性测试所有信息的文档。在我们的模块上有使用 KSZ8041 和 KSZ9031。我还会共享一个 TI 的文档,作为另一个例子。如果你正在研究新的以太网 PHY 并想要进行以太网一致性测试,请提前向你的供应商索要关于寄存器配置的详细信息。

http://ww1.microchip.com/downloads/en/AppNotes/AN2686-Ethernet-Compliance-Test-10BASET-100BASETX-1000BASET.pdf

http://www.ti.com/lit/an/snla239a/snla239a.pdf

测试设备

如上面描述,我们必需能够精确地测量皮秒级别的精度。因此我们需要非常好的工具。你应该使用至少1 GHz 带宽和 4MS 存储的示波器。你一般还需要一个测试夹具,将以太网信号从以太网接口传输至示波器输入通道。因此我们和 Teledyne LeCroy 紧密合作。在技术层面我们有很深入的协作。我们使用 WaveMaster 系列的高端示波器,以及合适的硬件和软件工具 。当然,也有其他厂商可以提供相关设备如Tektronix、Rhode&Schwarz、Keysight 等。

引述自 Teledyne LeCroy 的专家 Hofferbert 先生:

“Teledyne LeCroy 是一家领先的数字存储示波器 DSO 制造商。现代的 DSO 能够进行资质测量。Toradex 选用了 Teledyne LeCroy 合适的设备来测试以太网 PHY 设计。借助我们的 QualiPHY 软件和最新的示波器,一项半自动的测试可以根据 IEEE 802.3 规范测量以太网 PHY 物理层信号。该测量方案能够让 Toradex 的研发工程师在他们的嵌入式系统早期设计阶段就可以测试并解决信号完整性的问题。Toradex 对尽可能高效地使用测量设备很感兴趣。如果出现不确定或者测量偏差的情况,我们合作快速解决问题,并提供我们在测量方面的专业知识。”

Gregor Hofferbert, Teledyne LeCroy

www.teledynelecroy.com

http://cdn.teledynelecroy.com/files/manuals/qualiphyenetmanual.pdf

总结

在完成一致性测试后,我们可以创建一个测试报告来验证我们的 PCB 设计。如你在 Teledyne LeCroy 测试报告中看到的,Colibri iMX6ULL 和 Iris 载板符合 10Base-T 和 100Base-TX 标准。所以我们相信我们的方案可以和其他兼容系统正常工作。我们很有信心和客户共享我们的以太网接口 PCB 设计。你可以在下面看到载板设计指导:

https://developer.toradex.com/carrier-board-design

我们还免费向我们的客户开放我们载板设计的 Altium Designer 项目。我们还在我们的在线社区提供大量的帮助:

https://www.toradex.com/community

我们在最新的 BSP 中开始提供我们的测试软件。我们采用现有的驱动,使其可以在我们的模块上方便地进行一致性测试。但仍需注意,对于每个 PHY 你需要使用不同的软件技术来获得测试图案。并没有一个简单的手册。例如:

https://git.toradex.com/cgit/linux-toradex.git/commit/?h=tegra-next&id=13bd0f089ac6babeb7248fe3db4b9c19233cce3c

然而错误的走线、不良的接地布局或者不精确的晶振电路设计都可能引发问题。这还取决于测试环境。接地环路和噪音或者不足的供电可能引起测量误差。遵循 PHY 厂商的 设计指导,这一点很重要。我个人喜欢 Intel 的故障排除文档,你可以用它作为第一个调试参考。里面有关于错误的概况和可能的原因。设计时过长的走线、低品质变压器或者不正确的测量设备使用总会引起一致性测量的失败。但是也有一些特定问题具有强相关性。例如错误的电压幅值往往是偏置电阻不当或者中心抽头电路有问题。而高抖动会和晶振问题、阻抗不匹配或者供电问题有关。总的来讲,你的 PHY 厂商应该可以给予帮助,甚至可能是原理图或者布线核验。

https://www.intel.com/content/dam/www/public/us/en/documents/application-notes/ieee-conformance-phy-app-note.pdf

在本博文中,我想你展示了 Toradex 用于保证高品质产品的诸多验证测试中的其中一个。我们内部的测试以及您参考我们设计指导可以将风险降到最小。为了最好的品质要求,你可以对你定制的载板做验证,采用系统工程方法(例如 NASA所著的文档),推荐在早期进行测试从而降低风险和成本。我希望已经为你提供了详实的信息作为起步。如果你还想要了解更多,欢迎和我们取得联系。

/1

/1

文章评论(0条评论)

登录后参与讨论