某个模块需要把clk信号作为data信号用的时候,例如:

c = clk ? a : b ;

直接使用会导致逻辑综合、物理综合的大量时序问题。个人觉得解决方法如下(不对的请指正!)

1、如果clk直接由系统外部进入,可以简单地把clk作为enable信号使用。(如SPI的sclk信号)

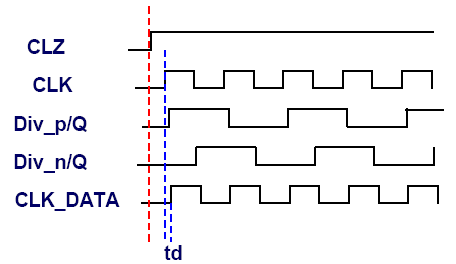

2、使用时钟隔离方法。如下图。

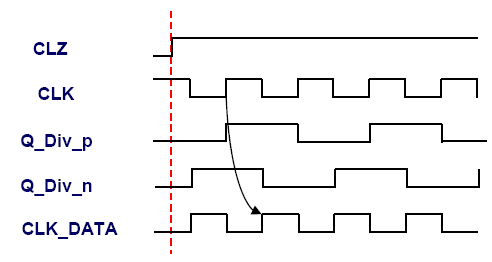

这里存在一个问题,就是reset信号在clk的不同电平情况下得到的CLK_DATA的相位差会相差180度。如下两图。

为了消除这个不确定性,就需要用clk信号对reset进行同步了!

/5

/5

文章评论(0条评论)

登录后参与讨论