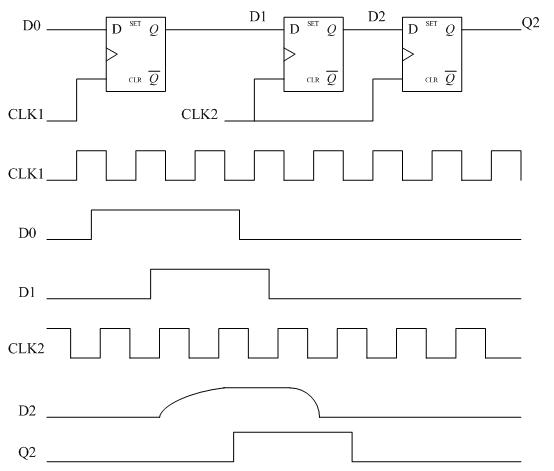

同频异相传递:

一种简单的解决办法是用两级寄存器pipe一下,第二级寄存器的输出Q基本上不会有亚稳态,但是这种办法并不能保证最后的输出结果一定是正确的,因为第一级可能发生亚稳态而产生了一个错误的采样值。

可靠的方法还是用双口RAM或者FIFO来缓存一下,由于是同频异相,因此吞吐速率一致,实现起来比较简单。

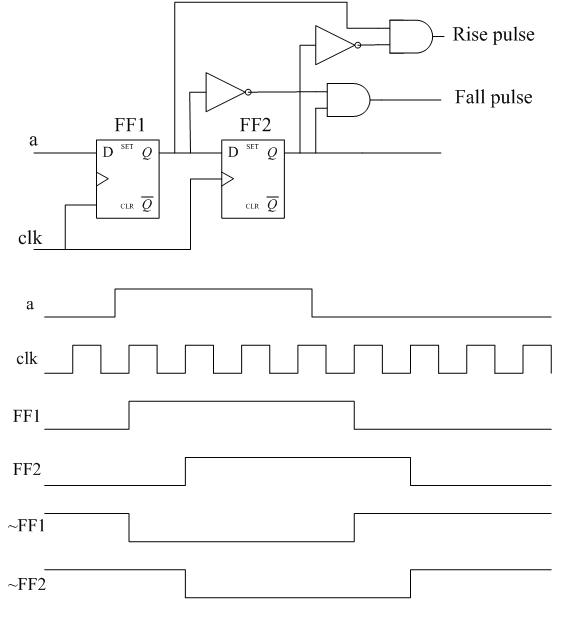

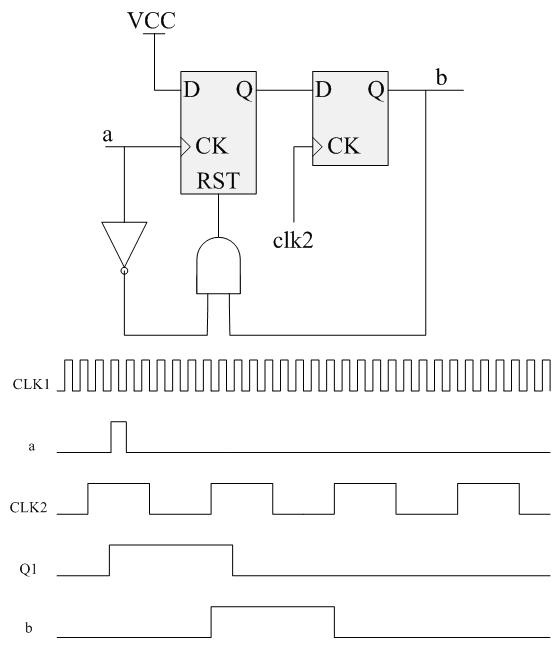

低频传递到高频:

在FPGA设计中经常会遇到这样的情况:一个异步的或者低频时钟域的信号要触发某个高频时钟域的动作,处理方法也是用两级寄存器pipe一下,然后用组合逻辑产生出高频时钟域的脉冲,这个脉冲可以作为消息传递去控制高频系统的相应动作。

/5

/5

用户213742 2012-3-20 22:30

用户213742 2012-3-20 22:15

用户1708388 2012-3-19 22:54

用户1660450 2012-3-19 12:05