下面开始来仔细研究研究这个增量编译。

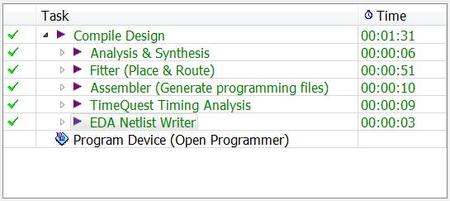

首先,得先看看QuartusII的编译过程是个怎么样的,要了解这个过程很简单,看看下面这张图,谁都不陌生:

当我们点全编译之后,下面的几个过程就会一个一个打上勾,而我们编译的过程也就是和这个运行过程是一致的:先是分析综合,再是布局布线,然后是汇编(这里不是指汇编语言的汇编,而是说将布局布线后的“电路”汇编成可下载到芯片内的“程序”),还有时序分析以及生成网表。

我们仔细看它编译的过程会发现其中耗时最多的是分析综合和布局布线(这点从上图右侧的时间标注也能看出来),所以我们想提高编译速度也应该从这点入手。

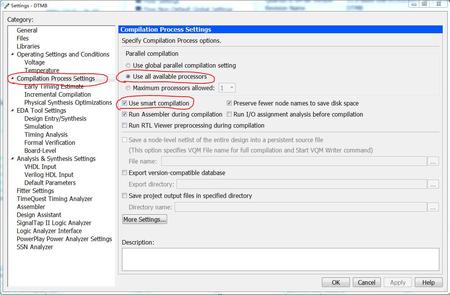

Quartus也有相关的自动增量编译的设置,如下图:

第一个是多核处理器的设置,这样可以提高整体的速度;第二个则是采用Smart Compilation,智能编译方式,它可以完成的功能——如果设计源文件没有改动,那Quartus将不再进行分析综合,而直接进入布局布线阶段。另外,还有一个设置也可以勾选上:

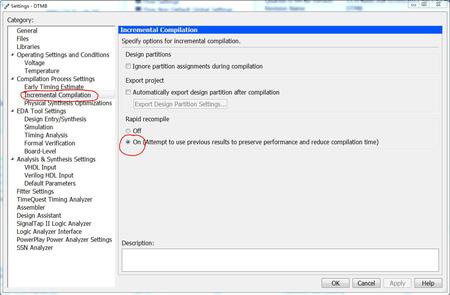

Rapid recompile,即如果设计没有修改那不进行重新编译。

从编译过程,我们再来看看我们的设计流程:

可以发现,其实设计过程和编译过程是一样的。而增量编译的原理就是,减少每次编译里我们设计已经完成的部分,进而不需要再重复设计者认为已经完成的工作。说得再直白一点:我们设计者手动得将整个工程分成N个子模块(此处指的是逻辑模块),并设定各个模块的状态(已经完成了,不需要更改了,编译时就采用上一次的结果),这样编译器在分析综合的时候便可以对那些不需修改的部分直接采用上次的结果。布局布线的时候也是一样的,如果该子模块不需要更改了就采用上次的结果,如需更改再重新进行布局布线,只不过布局布线的过程要相比分析综合复杂一些。

而上面提到的将整个工程手动分成N个模块,我们就要用到Quartus提供的两个高级工具——Design Partitions和LogicLock Regions。

/2

/2

文章评论(0条评论)

登录后参与讨论