原文:ALTERA官方英文版。需要的点下载![]() SignalTap.pdf。

SignalTap.pdf。

本文由本人原创翻译,水平有限,仅学习所用,有错误请指正。

一、例子

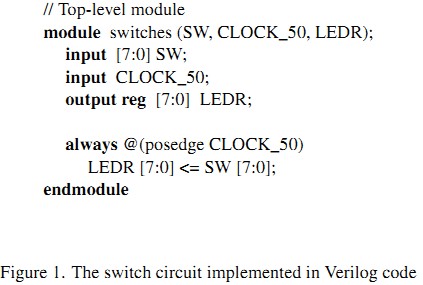

我们使用如图1所示的verilog代码所实现的开关电路作为例子。这个电路把DE系列开发板上的前8个开关简单的和对应的8个红色LED相连接。它是这样工作的:在时钟(CLOCK_50)的上升沿读取开关的值,放入对应的寄存器,寄存器的输出与红色LED直接相连接。

按照图1代码实现该电路,锁定引脚,编译整个工程等等,这些在这里不再重复累述。

二、使用SignalTap II软件

在本文的第一部分,我们将建立SignalTap逻辑分析仪来探测8个LED开关的值,同时,我们将设定逻辑分析仪的触发信号为当第一个开关(LED[0])为高电平。

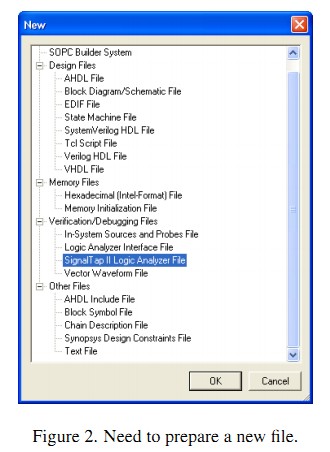

1. 选择File->New打开逻辑分析仪窗口,该窗口如图2所示。选择SignalTap II逻辑分析仪文件并点击OK。

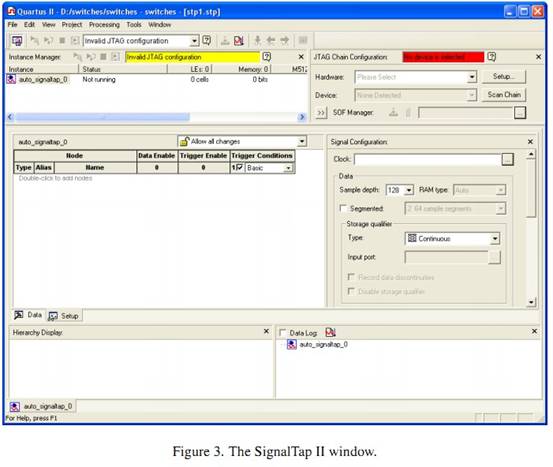

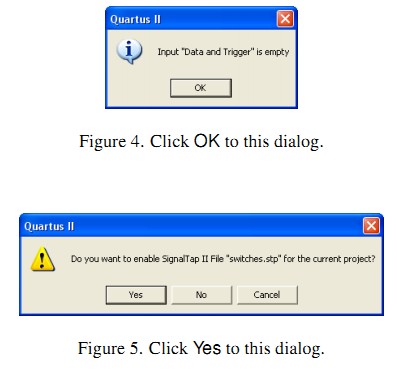

2. SignalTap II界面如图3所示。保存文件并命名为switches.stp。在下一步如图4所示对话框中点击OK,接下来出现对话框”Do you want to enable SignalTap II file ‘switches.stp’ for the current project?”询问是否在当前工程中使用SignalTap II,点击Yes(图5)。现在,SignalTap II文件switches.stp已经和当前工程相关联了。

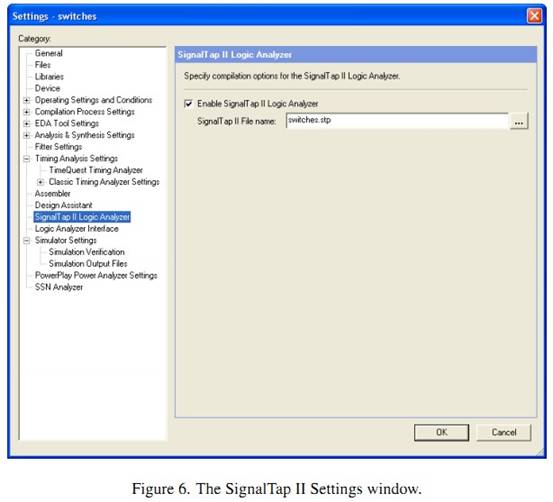

注意:如果我们需要在工程中不使用该SignalTap II文件,或者不使用SignalTap II逻辑分析仪,在Quartus II界面中选择Assignments->Settings。然后在打开窗口左边的分类列表中选择SignalTap II Logic Analyzer,如图6所示。可以把Enable SignalTap II Logic Analyzer前面的勾去掉来关闭逻辑分析仪。在一个工程中可能同时会有多个SignalTap文件,但在同一时刻只能有一个有效。多个SignalTap II文件是非常有用的,比如工程很大,在工程中不同的部分都需要用SignalTap II来捕捉信号,这样探测不同的部分时我们只需要使用不同的SignalTap II文件就可以了,避免反复设定SignalTap II文件。按照步骤1和步骤2可以建立新的SignalTap II文件,不同的SignalTap II文件拥有不同的文件名。如果要改变当前工程中已经关联的SignalTap II文件,在图6中的SignalTap II File name选择框中点右边的浏览按钮,选择所需要的SignalTap II文件,然后点击Open,最后点击OK就可以了。在本教程中,我们选中Enable SignalTap II Logic Analyzer选项并使用switches.stp文件。设定好后点击OK按钮关闭设置窗口。

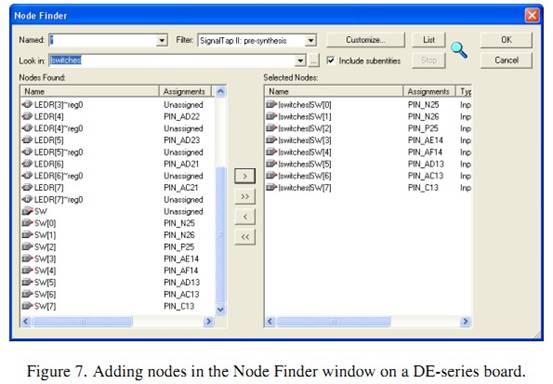

3. 现在我们需要把工程中想要观察的信号结点添加进来。在SignalTap II窗口中的Setup标签页中,双击灰色字体记号”Double-click to add nodes”的区域,就会打开Node Finder窗口,如图7所示。在Filter区域中,选择SignalTap II:pre-synthesis,然后单击List,在Nodes Found区域中将会显示在工程中能被观察到的节点列表。在这里我们选中SW[0],SW[1]…到SW[7],然后单击”>”按钮,这样就把要观察的开关节点添加到SignalTap II中。最后单击OK。

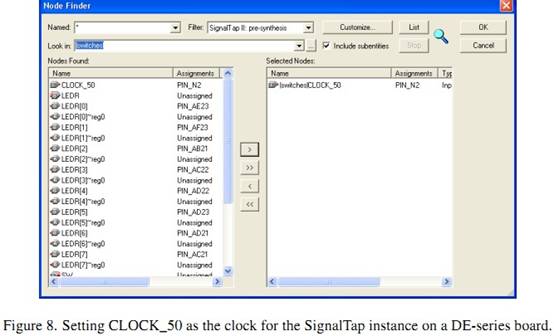

4. 在SignalTap II逻辑分析仪能正常工作之前,我们需要为SignalTap II模块指定驱动时钟,在例化时,SignalTap II模块包含在我们的设计中。在SignalTap窗口Signal Configuration面板中的单击Clock部分右边的”…”打开Node Finder窗口。点击List,显示所有能被添加为时钟的信号节点,然后双击CLOCK_50,结果如图8所示,最后点击OK。

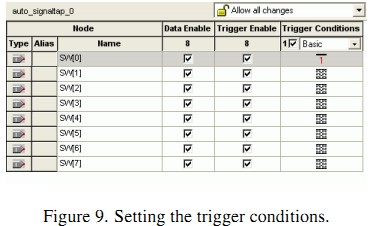

5. 在SignalTap窗口中Setup标签页中,选中Trigger Conditions列中的单选框,然后在单选框右边的下拉菜单中选择Basic。右键节点SW[0]相对应的Trigger Conditions单元,选择High,如图9所示。这样设置以后,当DE系列开发板上对应的第一个开关被设置为高电平时,逻辑分析仪将会开始运行捕捉数据。注意到我们可以右键Trigger Conditions列单元中的添加进来的任何信号节点,并可以选择一系列不同的触发条件。当所有这些条件都同时满足时实际的触发条件才成立。在本文中,我们选择触发条件SW[0]为高电平,SW[1],SW[2]…SW[7]设为默认值Don’t Care,即触发条件和SW[1],SW[2]…SW[7]的值无关。

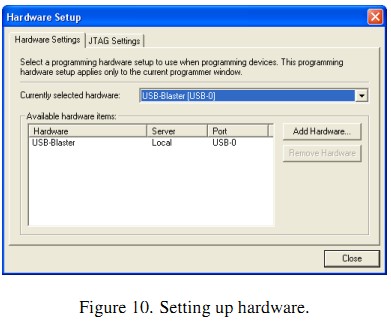

6. 接下来我们还需要正确的建立硬件环境。首先,确保DE系列开发板已经和电脑连接好且电源已经开启。然后,在SignalTap II窗口右上方中的Hardware部分,单击Setup,打开如图10所示的窗口,在Available Hardware Items菜单中双击USB-Blaster,最后点击Close。

7. 最后一步就是重新编译整个工程。在Quartus II窗口中,选择Processing->Start Compilation,接下来会弹出提示说需要保存改动,这里选择Yes。编译完后,打开Tools->Programmer,把重新编译的工程下载到DE系列开发板上。

三、使用逻辑分析仪观察信号

现在工程中嵌入的SignalTap II逻辑分析仪已经例化完成,并已经加载到DE系列开发板上,我们可以像使用外部的逻辑分析仪一样使用SignalTap II逻辑分析仪来观察信号。

1. 首先把DE系列开发板上所有的开关(0-7)设为低,当开关0的值变为1时,我们将会观察到这些开关的值。

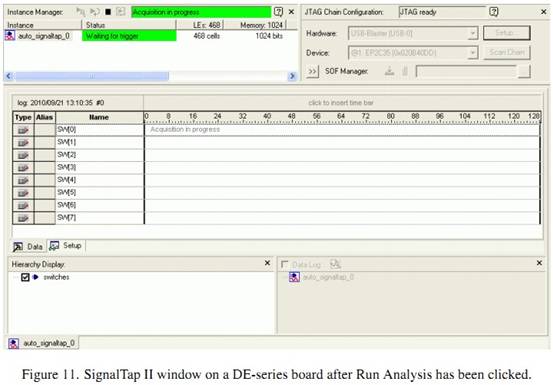

2. 在SignalTap窗口,选择Processing->Run Analysis或者单击![]() 图标。接着,单击SignalTap II窗口中的Data标签页。这时,我们应该得到和图11相似的界面。注意到这时SignalTap II Instance Manager面板中状态Status中显示”Waiting for trigger”,这是因为触发条件(开关0的值变为1)没有满足。(我们在之前的步骤中把开关0的值初始化设为0,如果没有初始化开关0的值为0,现在可以把它设为0然后再一次点击Run Analysis)。

图标。接着,单击SignalTap II窗口中的Data标签页。这时,我们应该得到和图11相似的界面。注意到这时SignalTap II Instance Manager面板中状态Status中显示”Waiting for trigger”,这是因为触发条件(开关0的值变为1)没有满足。(我们在之前的步骤中把开关0的值初始化设为0,如果没有初始化开关0的值为0,现在可以把它设为0然后再一次点击Run Analysis)。

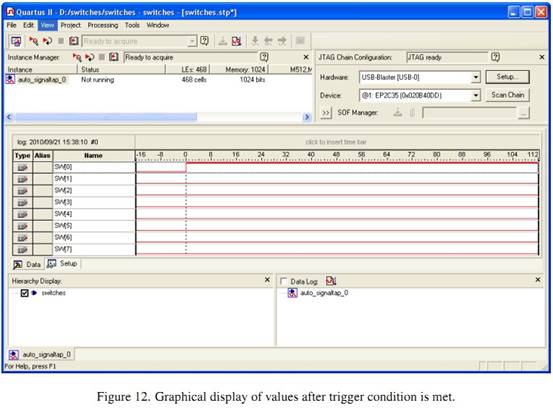

3. 现在,我们可以把DE系列开发板上的开关0的值设为1来观察逻辑分析仪的触发特性。我们应该会得到如图12所示的数据。注意到数据窗口中不仅显示了8个开关节点在满足触发条件之后的数据值,还包含触发之前的一段数据值。为了更进一步的观察,我们可以把开关0-7的值设置为任意组合然后再次单击Run Analysis。当开关0的值再一次被设为1时,我们将在SignalTap II Logic Analyzer中观察到所有开关的数值。

四、高级触发选项

相比如上述的SignalTap II的基本触发控制,有时在一个设计中我们可能会需要一个更复杂的触发条件。在下面的部分中,我们将讲述如何使用高级触发条件来设置更复杂的触发条件。

4.1 多级触发

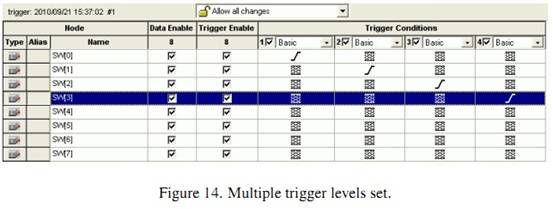

在这部分中,我们设置SignalTap II的触发条件为:当开关0,1,2,3的值依次从0变为1,即开关0-3的上升沿按顺序到来时。

1. 单击SignalTap II窗口中的Setup标签页。

2. 在Signal Configuration面板中,在Trigger Conditions下拉菜单中选择4,如图13所示(你可能需要往下滚动Signal Configuration面板才能看到该菜单)。这样,我们将在节点列表窗口中看到3个新的触发条件列表。

3. 右键点击触发条件1中对应SW[0]的单元,并选择上升沿Rising Edge。进行同样的操作把触发条件2中SW[1],触发条件3中SW[2]和触发条件4中SW[3]的触发条件设为Rising Edge。这时,我们应该会得到如图14相似的Setup标签页界面。

4. 重新编译整个工程然后把配置文件重新加载到DE系列开发板上。

5. 回到SignalTap II窗口,单击Data标签页,然后点击Processing->Run Analysis。注意到窗口显示状态将一直会是”Waiting for trigger”直到满足相应的触发条件。接下来,按顺序依次把开关的值从0设为1,开关1的值从0设为1,开关2的值从0设为1,开关3的值从0设为1。

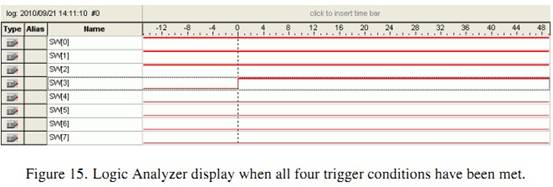

完成这些工作后,我们将会观察到如图15所示的所有开关的值。我们可以按照这一部分所讲述的方法建立不同的触发条件,然后在DE系列开发板上检验这些触发条件。

如果我们需要连续的观察逻辑分析仪,可以点击”Run Analysis”旁边的”Autorun Analysis”按钮,这样,在任何时刻,只要满足触发条件,要观察的信号值就会立刻得到更新显示而不需要再次选择”Run Analysis”。点击![]() 图标可以停止”Autorun Analysis”功能。

图标可以停止”Autorun Analysis”功能。

4.2 高级触发条件

在这个部分中,我们将学习如何设置高级触发条件。这次,我们将把触发条件设为:当开关0,开关1和开关2中的任何一个发生跳变(上升沿或下降沿)。这意味着当这3个开关中的一个的值改变时,逻辑分析仪将会更新显示所有观察信号的值。注意,我们可以把要观察信号的不同组合逻辑功能来作为逻辑分析仪的触发条件。作为本例,我们设置为上诉的触发方式,当我们学会了本教程后,可以自己体验下设置不同的高级触发方式。

1. 打开switches工程。

2. 打开SignalTap窗口并选择Setup标签页,在Signal Configuration面板中确认多级触发的值为1。

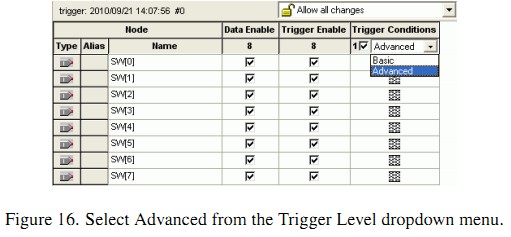

3. 在信号节点列表中的Trigger Conditions列中,确认Trigger Conditions复选框已经选中,然后在下拉菜单中选择Advanced,如图16所示。这将立即弹出如图17所示的窗口,该窗口允许你使用SignalTap中观察的信号节点中的不同信号来建立一个逻辑电路,作为触发条件。

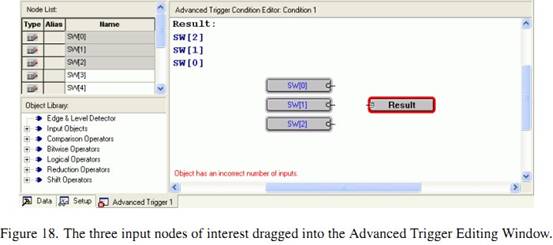

4. 在图17窗口的Node List部分中,高亮选中SW[0],SW[1]和SW[2],然后把它们拖曳到右边空白处的Advanced Trigger窗口,如图18所示。注意,我们也可以单独的对每个信号节点进行拉入和拖出。

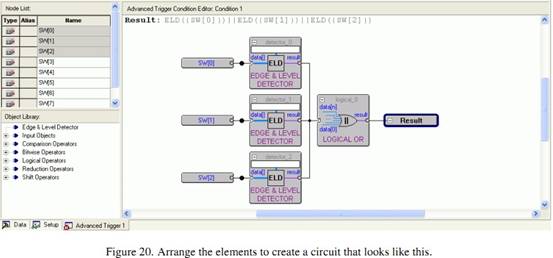

5. 现在,我们需要添加必须的逻辑运算符到我们的电路中。我们需要1个OR门和3个边沿检测器。单击左下Object Library窗口Logical Operators左边的+号,可以找到OR门,如图19所示,然后把OR门拖入到Advanced Trigger Condition Editor窗口中。

6. 这次,单击Edge & Level Edtector并把它拖入编辑窗口中。重复3次,然后把这些元件组成如图20所示的电路。3个输入SW[0],SW[1]和SW[2]分别和3个edge and level detector连接,3个detector的输出再和OR门相连。OR门的输出连接到输出脚Result上,输出脚本身就已经在编辑窗口中的了。

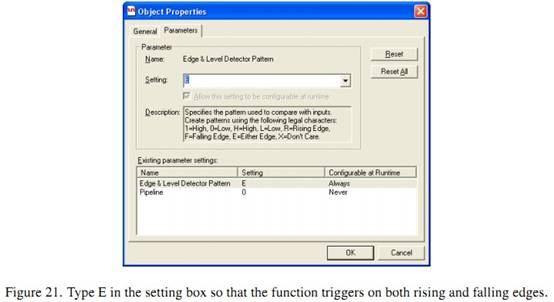

7. 我们现在需要设置每个edge and level detector,让它们都能检测到下降沿或者上升沿。双击第一个detector,打开如图21所示窗口,在Setting输入框中输入E然后单击OK。这代表着当输入出现下降沿或者上升沿时,detector的输出为1。重复上诉步骤设置第二和第三个detector。

8. 为了测试上诉高级触发条件,重新编译工程然后重新配置DE系列开发板。接下来按照之前部分的方法运行SignalTap。我们应该会注意到,每当板上的开关0,1,2中的其中一个的值发生改变,SignalTap II逻辑分析仪都将会被触发。

五、采样深度和缓存获取模式

在本部分中,我们将学习怎样设置采样深度逻辑分析仪的Sample Depth和两种缓存获取模式。我们将使用之前的工程并使用分段缓存。分段缓存允许我们把数据获取缓存分成几个独立并划分好大小的部分。本例中,我们将把采样深度为256bits的缓存分成8个32bits的部分。这样将会允许我们捕捉发生在8个连续触发时间附近的8个不同事件。

1. 把触发配置设回Basic并只有一级触发。检查触发条件是否为SW[0]的跳变沿。

2. 在SignalTap II窗口中的Signal Configuration面板中的Data面板的Sample Depth下拉菜单中选择256。这个选项允许我们指定在我们的设计中的触发时刻附近总共有多少个采样点。如果我们需要更多的采样点来调试我们的设计,可以选择更大的采样深度。注意,如果采样深度选择过大,在我们的设计中将可能会不够资源来实现,这样,设计就会编译不过。如果这种情况发生,请减小采样深度的大小。

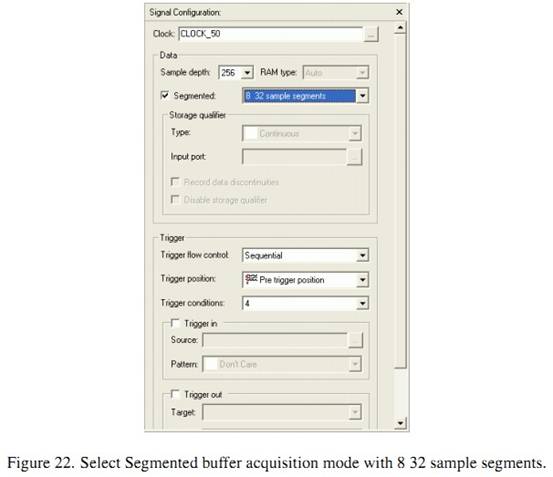

3. 在SignalTap II窗口的Signal Configuration面板中的Data部分,选中Segmented。然后在Segmented右边的下拉菜单中,选择8 32 sample segments。完成后的类似界面如图22所示。

4. 重新编译工程并加载配置文件。好了,我们可以使用分段获取模式Segmented Acquistion mode来观察我们的设计。

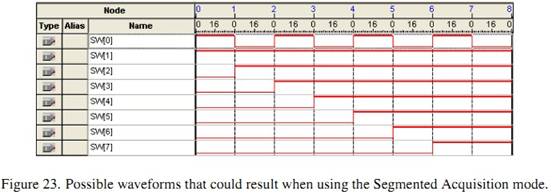

5. 回到SignalTap II窗口并单击Processing->Run Analysis。现在,反复拨动开关SW[0]并在两次拨动之间改变其他7个开关的值。当我们完成8次SW[0]的值改变时,采样缓存中的值将显示在data窗口中,这些显示的采样值是8个开关在触发时刻附近的数值。一种可能出现的波形如图23所示。该波形来源于实践者在改变SW[0]的值时同时改变其他开关的状态。

5.1使用Synthesis Keep指令

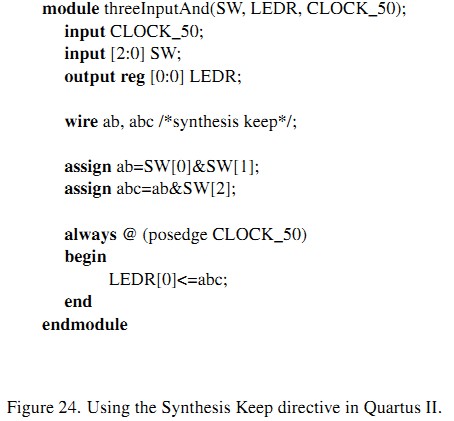

有时我们设计中的线网型wire变量在Quartus II编译中有可能会被优化掉。一个简单的例子如下面的verilog代码所示:

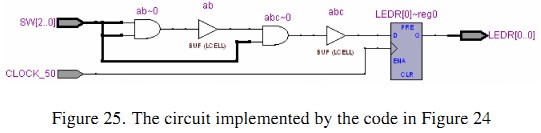

该电路的原理图如图25所示。标注ab和abc的三角符号元件为Quartus II插入的缓存模块,这些缓存并不改变通过它们的信号的值。

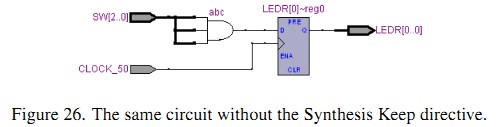

我们想利用SignalTTap II来观察输入SW[2:0]和输出LEDR[2:0]的值。同时,我们也想要观察内部信号wire ab的值。然而,如果没有加/*synthesis keep*/指令,只是按通常的verilog代码来编译,wire ab将会被优化掉,如图26所示:

因此,如果我们需要观察这个内部信号,我们可以告诉Quartus II我们不想把这个线网信号优化掉。加入/*synthesis keep*/指令在所声明的wire类型变量所在行的分号之前。图24所示代码已经包含了这句指令。按下面操作我们将可以观察到这个线型变量。

1.建立新的Quartus II工程threeInputAnd,并把图24所给出的verilog代码输入到工程文件中,编译工程。

2.打开Tools->SignalTap II Logic Analyzer,然后在SignalTap II窗口的Setup面板中,右键并选择Add Nodes。

3.在Filter区域中,选择SignalTap II:pre-synthesis,点击List。然后把节点ab,SW[0],SW[1],SW[2]和LEDR[0]加入到Selected Nodes List中并单击OK。

4.在Signal Configuration面板中,选择CLOCK_50作为时钟信号。

5.设置触发条件为当ab的值变高电平。

6.导入相关的引脚分配文件。

7.重新编译工程。

8.打开Tool->Programmer下载配置文件到DE系列开发板上。

9.再次打开SignalTap窗口,选择Data标签页。把DE系列开发板上的所有开关拨到值为0的位置。然后,单击Processing->Run Analysis启动逻辑分析仪。

10.把前两个开关拨到值为1的位置,这时,触发条件满足,观察信号。

用户377235 2015-8-12 21:27

用户1820115 2015-4-20 22:29

用户401816 2013-1-21 11:01

用户426241 2013-1-14 10:45

用户432934 2012-11-12 11:22

用户1644795 2012-5-24 18:35