夏宇闻《verilog数字系统设计教程》语法注意事项—总结

第三章:数据类型及其常量和变量

1)网络(wire)类型的变量不能存储值,而且必须受到驱动器(如门,连续赋值语句)的驱动,否则默认情况下其值为高阻Z。

2)寄存器(reg)是数据存储单元的抽象,默认初始值为不定态X。always赋值语句中的每个信号都必须为reg类型。Reg的数据可以赋值为正,也可以赋值为负,当一个reg数据是一个表达式中的操作数时,它的值被当做无符号值,如一个4位的reg,初始化时赋值-1,表达式进行计算时值被默认为+15。

3)对存储器(reg[m:0] mem[n:0])进行地址索引的表达式必须是常数表达式。

第四章:运算符、赋值语句和结构说明

1)不同长度的数据进行位运算,系统会自动的将数据按右端对齐,位数少的操作数在相应高位用0填满,以使两个操作数据按位进行操作。

2)一个m位的数左移n位,则移位后要用m+n位的数表示才可,一个m位的数右移n位后,仍可用m位表示。

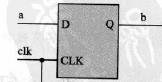

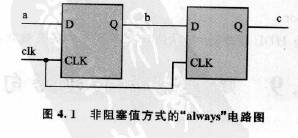

3)非阻塞赋值语句(<=)上面的赋值语句不能被下面立即使用,块操作完后才能完成这次赋值操作,所赋值是上一次得到的,在编写可综合时序逻辑时,这是常用的赋值方法。

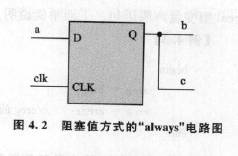

4)阻塞赋值语句(=)赋值语句执行完块才结束,在赋值语句执行完立刻生变,时序逻辑中使用时会产生意想不到的结果。

Always @(posedge clk)

Begin

b<=a;

End

和

Always @(posedge clk)

Begin

b=a;

End

综合结果实际上是一样的

但是,

Always @(posedge clk)

Begin

b<=a;

c<=b;

End

和

Always @(posedge clk)

Begin

b=a;

c=b;

End

综合结果却不同,

写代码时一定要注意!!

5)begin end用于标识顺序执行的语句,也就是说begin end内的语句是顺序执行的,被称为顺序执行块;fork_jion语句用来标识并行执行的语句,也就是说fork_jion内的语句是并行执行的,被称为并行执行块。顺序执行块的起始时间是第一条语句开始执行的时间,结束时间是最后一条语句执行完的时间,并行执行块的每条语句开始时间是相同的,结束时间是按时间排序在最后结束的语句的执行时间。

第五章:条件语句、循环语句、块语句和生成语句

1)条件语句必须在过程语句块中使用(initial ,always),其他地方不能使用。

2)initial语句只执行一次,always语句不断重复的执行。

第六章:结构语句、系统任务、函数语句和显示系统任务

1)新版verilog1364-2001版的语法中always语句中的关键词“or”也可以用“,”来代替。也可以用always@(*)表示所有的敏感列表。

2)函数的定义不能包含任何的时间控制语句,即任何使用#,@,或wait来标识的语句。函数只能与主模块共用一个仿真时间,而任务可以定义自己的仿真时间。函数不能启动任务,任务能启动其他任务和函数。函数至少要有一个输入变量,而任务可以没有或有多个任何类型的变量。函数返回一个值,而任务不返回任何值。

第十四章 深入理解阻塞与非阻塞赋值的不同

1) 在描述组合逻辑的always块中用阻塞赋值,则综合成组合逻辑的电路结构;

2) 在描述时序逻辑的always块中非阻塞赋值,则综合成时序逻辑的电路结构;

为什么一定要这样做,为的是保证综合前仿真和综合后仿真一致的缘故。如果不

按照上面的要求做,也有可能综合出正确的逻辑,但前后仿真结果不一致。

3) 阻塞赋值过程中,先计算右值,这时赋值语句不允许任何别的verilog语句的干扰,直到现行的赋值语句完成时刻,即把右值赋给左值时,它才允许别的赋值语句执行,所谓阻塞赋值从概念上讲后面的赋值语句是在前一句结束后才开始赋值的。

4) 非阻塞赋值过程中,在赋值操作开始的时刻计算非阻塞赋值语句的右值,赋值操作结束后才更新左值,相当于在赋值语句结束时刻将右值集体赋给左值,在计算右值期间不影响其他语句的执行(如计算右值)。

5) Verilog编程要点:1、时序电路建模时,用非阻塞赋值;2、锁存器电路建模时,用非阻塞电路赋值;3、always块建立组合逻辑时,用阻塞赋值;4、always块又有时序逻辑又有组合逻辑时用非阻塞;5、不要在多个always语句中对同一个变量赋值。

触发器电路:

Always @(posedge clk)

Begin

Q<=d;

End

锁存器电路:

Always @(en,d)

Begin

If (en)Q<=d;

end

/2

/2

文章评论(0条评论)

登录后参与讨论