一:模块划分技巧:

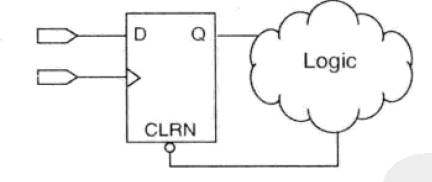

1) 对每个同步时序设计的子模块的输出使用寄存器;

2) 将相关的逻辑或者可以复用的逻辑划分在同一模块内;

3) 将不同优化目标的逻辑分开;

4) 将松约束的逻辑归到同一模块中;

5) 将存储逻辑独立划分为模块;

6) 合适的模块规模。

二:组合逻辑注意事项

1) 避免组合逻辑反馈环路,牢记任何反馈环路必须包含寄存器,检查综合和实现报告,发现combinational loops必须修改

2) 替换延迟链

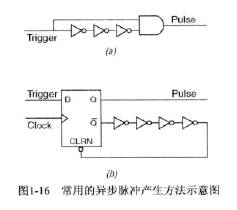

异步时序中,在两个节点中插入buffer或门延迟进行时间调整,如ASIC设计中

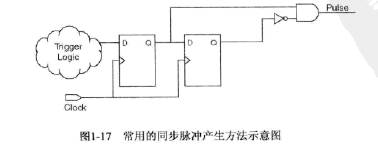

同步时序中,常用方法是分频或倍频或者计数器完成延时功能。

3) 替换异步脉冲产生单元

4) 避免使用锁存器(latch)

不完整的if 和case语句,组合逻辑反馈环路等都可能产生lactch。

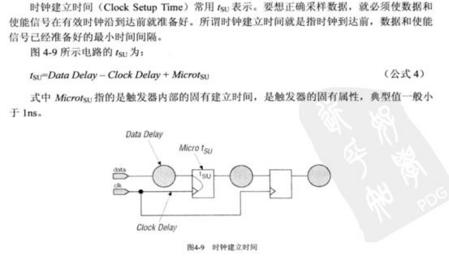

三:时钟建立时间

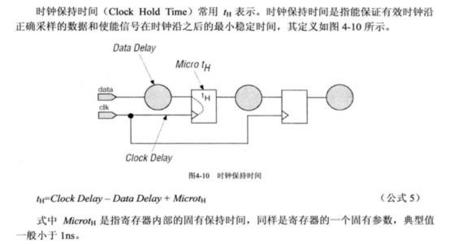

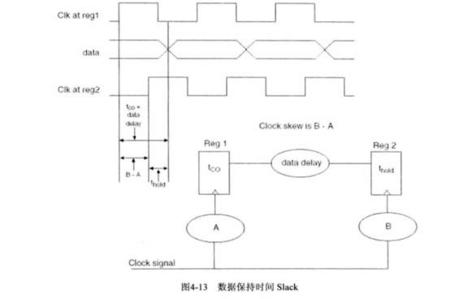

四:时钟保持时间

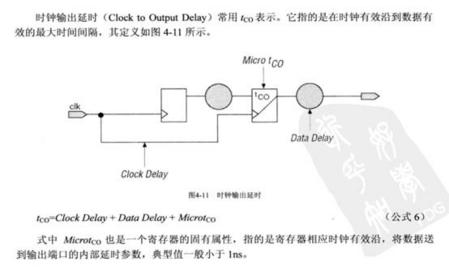

五:时钟输出延时

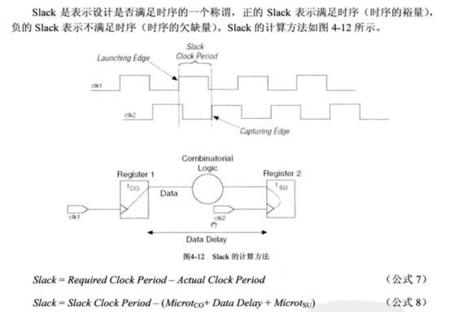

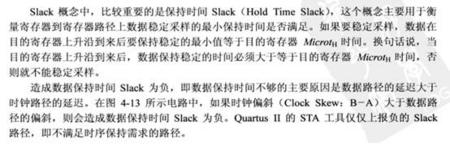

六:时钟裕量

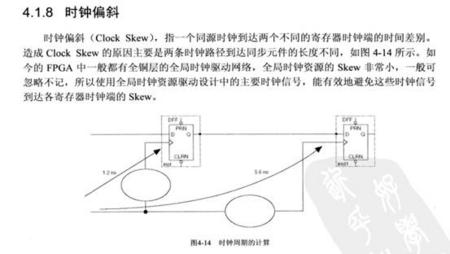

七:时钟偏移

/5

/5

文章评论(0条评论)

登录后参与讨论