2.2)如何从优化的角度写代码

上面试从partition的角度来讲解在写代码的时候如何注意优化,下面注重从一行行代码的角度讲解如何写出比较好的代码,利于优化。我上面也讲到,好的开始是成功的一半,否则会出现南辕北辙的局面。

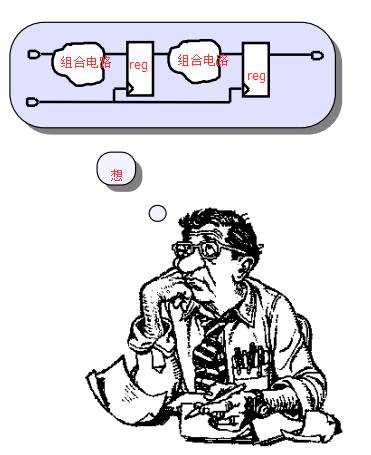

2.2.1)从电路的角度思考问题

我们在写代码的时候,脑海里最好有一块块的电路,RTL的含义就是register transfer level,所以你的脑海中要有一块块的电路,这个电路后面接着寄存器来敲一拍保证好的时序。

写出能够综合的代码,切记像写c语言一样去写代码(当然现在有些工具已经能够将c语言转换成rtl代码,但是还不够成熟)。

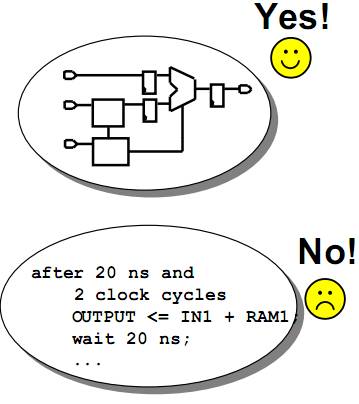

2.2.1)注意不同语句的影响

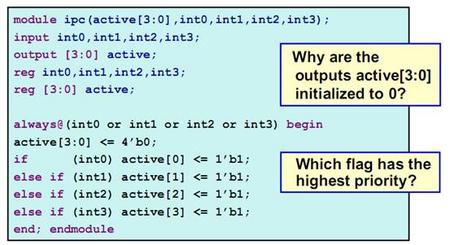

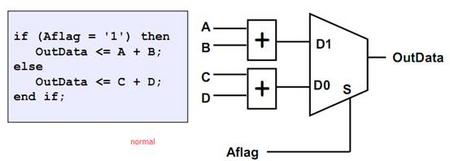

If-else语句,具有优先级,串行,比较省面积,速度慢;

该语句比较慢的原因就是因为它具有优先级的原因,如果if-else-else-else太长,会导致组合逻辑链太长进而影响速度,但是现在的工具都已经很智能了,不会蠢到一直延长逻辑链。

注意:纯组合逻辑的if-else if语句,最后不要忘了加上else,否则会综合出latch(电平触发,纯组合逻辑有时会出现,不必要的latch会导致电路面积很大,影响时序),latch在数字逻辑设计中是忌讳有的。在FPGA中根本没有锁存器这种东西,所以说,如果你的电路产生了锁存器latch的话,将耗费更多的资源来构成它。

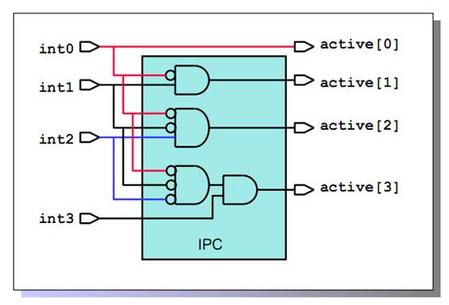

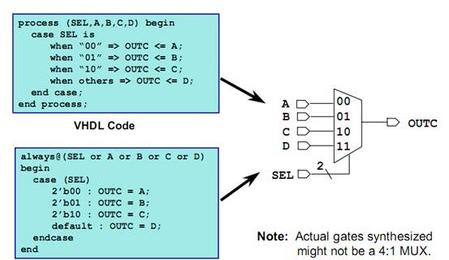

Case语句,并行,面积大,速度快

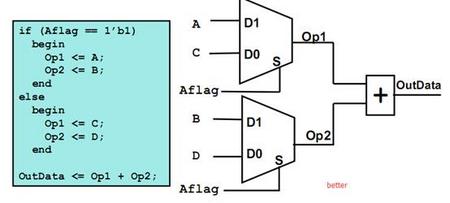

上图的mux4-1采用case语句实现,最终是并行的,组合逻辑链不会太长,所以速度比较快,缺点是面积会比较大,这其实就是面积和速度之间的互换。注意最后不要忘了加default。

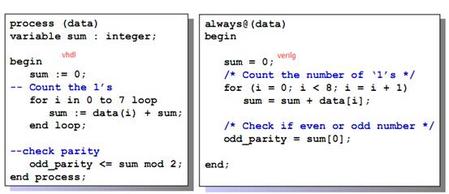

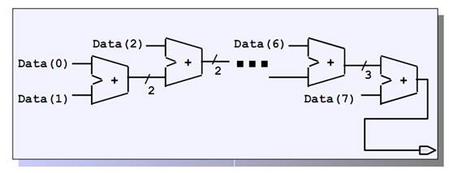

For语句循环

这类语句一般用在产生电路中,其中for循环必须是确定的值,不能是变量,否则不可能综合出电路。

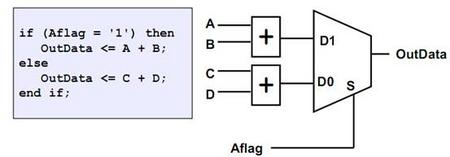

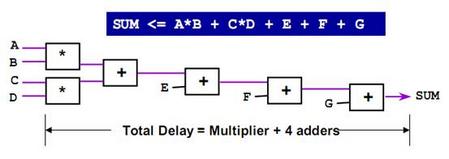

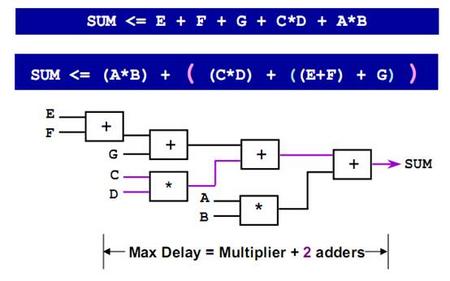

2.2.2)注意调整计算公式的架构

组合逻辑链路延时少了

多了mux,少了加法器,面积少了

现在的工具已经相当的智能了,可以将上面比较蠢的写法综合成很聪明的方式,列出这项的目的是希望大家平时写代码的时候还是要注意一下的,不要写出自己都觉得很傻的代码出来。

/5

/5

文章评论(0条评论)

登录后参与讨论