3、建立时间时序路径逐个解析

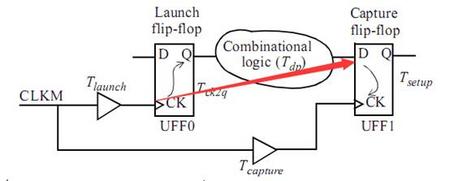

1)Path2:从DFF的clk pin到另一个DFF/D端;

建立时间可以看成是最大的delay。

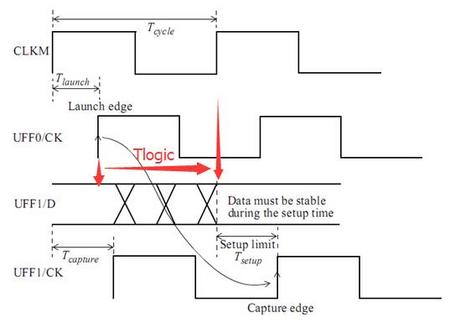

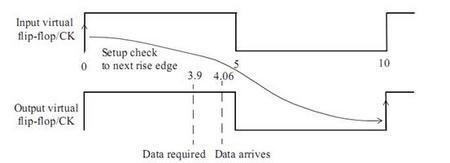

从上图的波形可以看出,要想让uff1稳定的采样到uff0的数据输出,也就是uff1/d,数据必须在红色箭头之前稳定,则根据上图的时序关系不难得出如下公式。

Tlaunch + Tlogic + Tsetup <= Tcapture + Tcycle,

其中Tlogic = Tck2q + Tdp,Tlanch-Tcapture = Tuncertainty;上式变为

Tuncertainty + Tlogic + Tsetup <= Tcycle

从上式可以看出,如果Tlogic + Tsetup一定的话,Tuncertainty为负,实际上是有利于时序的。另外delay不能太大,否则不能满足setup的关系。

再变换公式有:

Tlogic <= Tcycle – Tsetup – Tuncertainty;

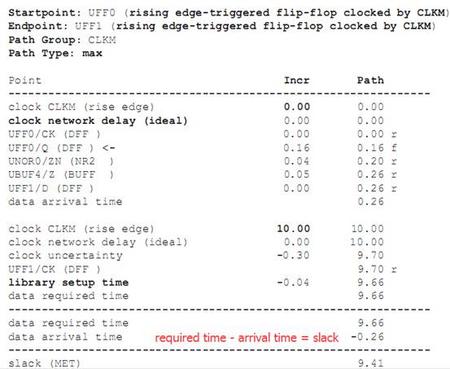

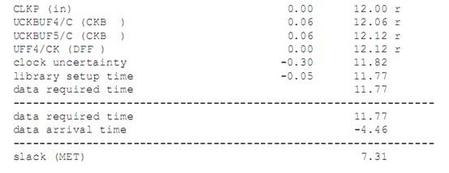

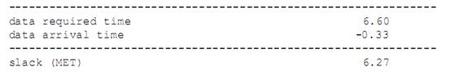

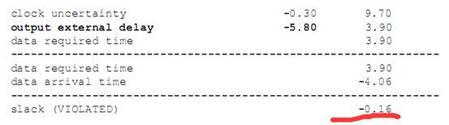

如下面的时序分析路径:

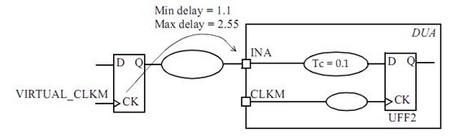

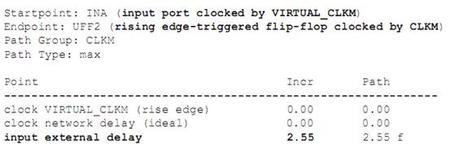

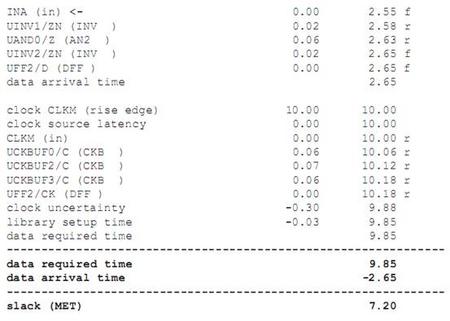

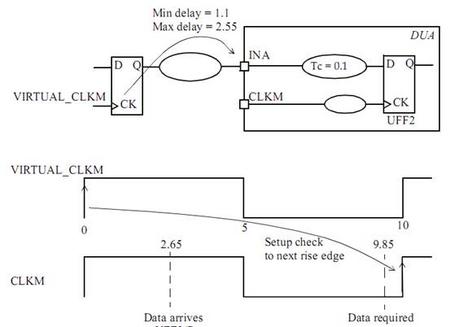

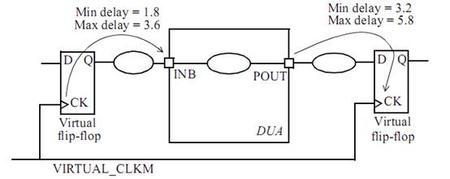

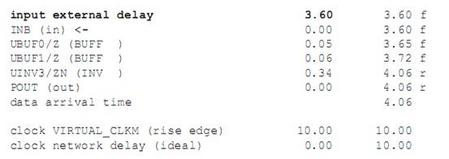

2)Path1:从input port端到DFF/D端,一般需要对clk和rst外的所有input port设置input_delay,通常情况下设置比较紧的时序时为2T/3(不知道input_delay是多少的时候给出的预估),也就是给input port端到DFF/D端留T/3的时间;

虚拟clk

实际clk

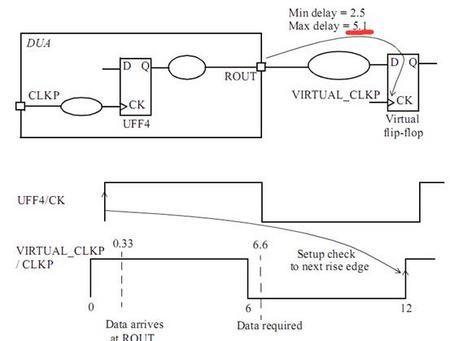

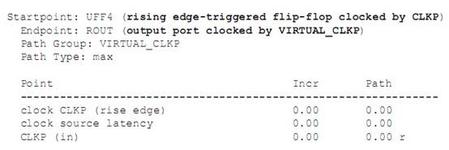

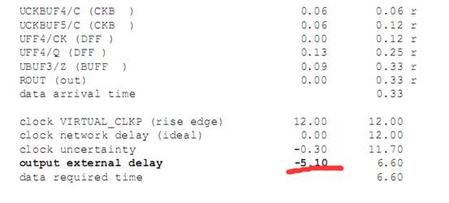

3)Path3:从DFF的clk pin到output port,一般而言,需要对所有output port设置output_delay,通常情况下设置比较紧的时序时为2T/3(不知道output_delay是多少的时候给出的预估),也就是给DFF的clk pin到output port端留T/3的时间;

4)Path4:纯组合逻辑,从input port到output port,一般而言其延时设置为5T/3,(减去2T/3的input delay和2T/3的output delay,也就是给组合逻辑留了T/3的时间)。

/5

/5

文章评论(0条评论)

登录后参与讨论