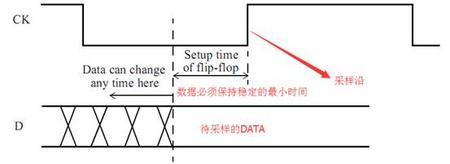

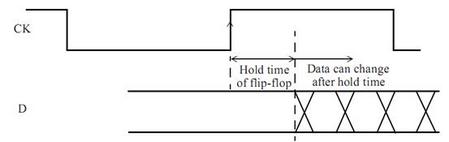

2、 为什么会有setup(建立时间)和hold(保持时间)(注:这部分参考了网上的资料)

建立时间粗略示意

保持时间简单示意

图1经典的上升沿D触发器内部结构

关于为什么会有建立时间和保持时间,我曾试图从触发器或锁存器内部的结构去分析和证实,但是看了许多资料,由于触发器的内部结构有很多,所以分析方法很多,说法也很多。下面针对上图比较经典的结构来分析一下建立时间和保持时间。

如上图1所示,这是一个上升沿触发的D触发器,需要注意的是,图中的6个与非门都是有延迟的,也就是在某一时刻输入组合逻辑的数据,在一段时间之后才能影响其输出,这是产生建立时间和保持时间要求的最根本原因。

首先,我们在假设所有的与非门的延迟为0,叙述一下这个触发器的整体工作流程。

当CLK=0时,与非门G3和G4的输出均为1,输出的1反馈到G1和G2作为输入,导致G1和G2的输出分别为D和/D,输出的D和/D又反馈到G3和G4;而G5和G6在此期间一直锁存着之前的数据,不受输入影响。

图2 CLK=0时触发器内部信号详情

当CLK=1时,与非门G3和G4的输出变为/D和D,输出到G5和G6作为输入,根据锁存器的原理,G5和G6最终会稳定的输出Q和/Q。

图3 CLK=1时触发器内部信号详情

然后我们把门电路的时延加上。设G2和G1 的延迟为T1,当CLK=0时,如果D在时钟跳变前的T(T)时间才从d1更新为d2,那么G1和G2在时钟跳变时刻的输出值肯定是d1和/d1,而不是d2和/d2,进而影响到G3和G4的输出。如果要使得G1和G2的输出为d2和/d2,就必须要求D起码在时钟跳变之前的T1时间内维持d2稳定不变。这个T1就是建立时间Tsu。<>

当CLK=1时,G3和G4的延迟为T2,当CLK=1时,如果D在时钟跳变之后的T(T)时间从d2更新为d3,由于G3和G4的输出在T的时间内还保持为1,所以D的更新会影响G2和G1的输出,进而影响G3和G4的输出,进而影响G5和G6的输出,造成输出Q和/Q不稳。<>

<><>

/5

/5

文章评论(0条评论)

登录后参与讨论