译码器是组合逻辑电路的一个重要的器件,其可以分为:变量译码和显示译码两类。 变量译码一般是一种较少输入变为较多输出的器件,一般分为2N次方译码和8421BCD码译码两类。

74138是一种3线—8线译码器 ,三个输入端CBA共有8种状态组合(000—111),可译出8个输出信号Y0—Y7。3-8译码器的详细说明请参考相关资料,本文使用Verilog实现一个简单的3-8译码器,并在硬件上验证,供FPGA初学者参考。

所用软件:Quartus 10.0 SP1

硬件:FPGA礼物开发板A3 mini 核心芯片为CycloneIII EP3C5

3-8译码器有3个输入,8个输出,和3个使能位。

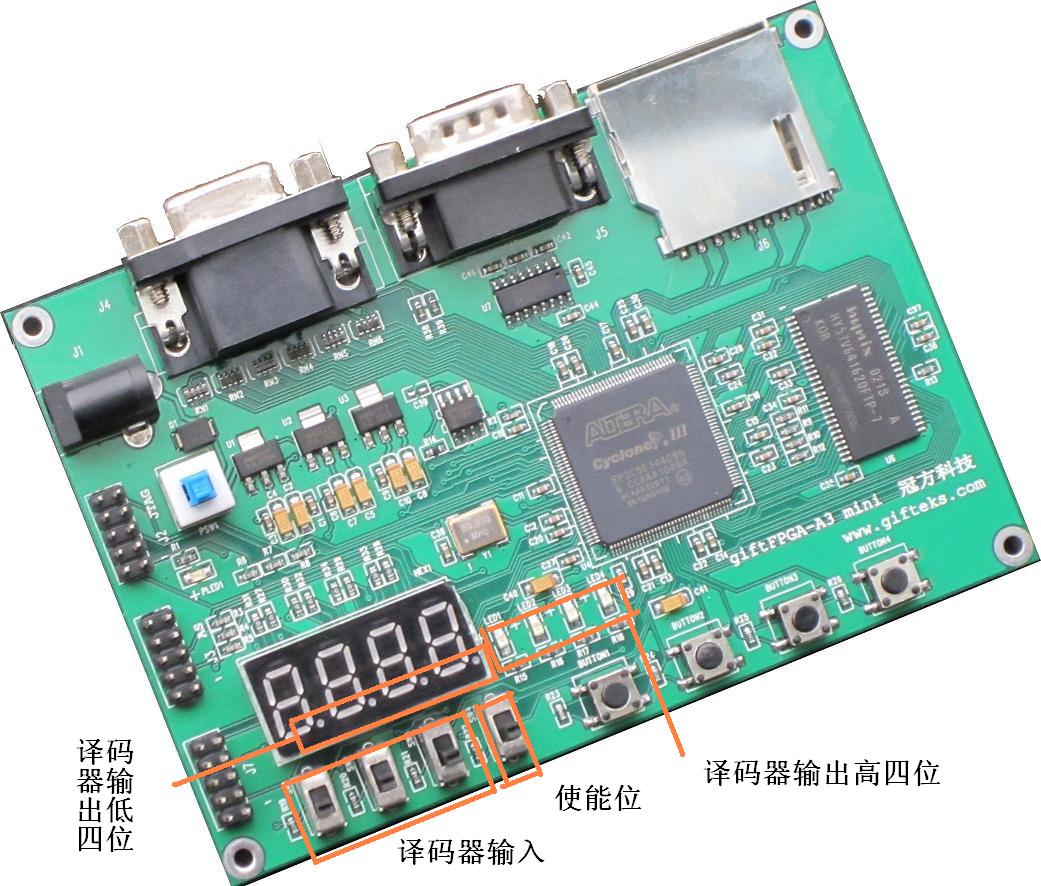

FPGA礼物开发板A3 mini上有四个滑动开关,可以选择三个作为译码器输入,为了简化,使能位我们只用一个,使用第四个滑动开关作为使能位输入。开发板上有四个LED,作为译码器输出的高四位,使用数码管的四个小数点做为译码器输出的低四位。参照下图。

Verilog代码

module decoder3_8(dout,din,de,dp,);

output[7:0] dout;

input[2:0] din;

input de;

output dp;

reg[7:0] dout_r;

always @(de)

begin

if(de==0) dout_r=8'b11110000;

else

begin

dout_r=8'b00000001<<din;

dout_r=~dout_r;dout_r=((~dout_r)|8'b11110000)&(dout_r|8'b00001111);

end

end

assign dout=dout_r;

assign dp=1;

endmodule

其中,dout为译码器输出,din为译码器输入,de为使能端。dp为数码管小数点,因为fpga礼物开发板上使用的是共阴数码管,dp需要一直保持高电平,通过给数码管选择位低电平来点亮数码管小数点。而点亮led需要给高电平,为了保持显示效果一致,我们在相应位需要取反。

if(de==0) dout_r=8'b11110000;本来输出应该为8’b11111111,为了显示效果,第四位取反

dout_r=8'b00000001<<din;

dout_r=~dout_r;这两行代码实现了3-8译码器逻辑,不清楚的可以参照3-8译码器真值表。

dout_r=((~dout_r)|8'b11110000)&(dout_r|8'b00001111);也是为了显示效果需要,低四位取反。

3-8译码器是组合逻辑的典型,初学者可以自己动手,练练其他的组合逻辑,练习多了,自然就掌握了。

冠方科技 http://www.gifteks.com

/4

/4

文章评论(0条评论)

登录后参与讨论