随着FPGA的基础的学习…

随着Verilog基础的学习…

随着工作的“乏味”…

随着时间的推移…

随着就开始了NIOS的学习,刚开始,可能是初生牛犊不怕虎,还是眼高手低,反正感觉自己学学NIOS还是比较有优势,因为硬件软件都都通“吃”的缘故吧,可是,转折了,肯定不好了,从软件遇到的问题,到下载的问题,到SDRAM时序的问题,等等…

最后自己还是被撞的头破血流,所以又回来了,回到了时序的分析,时序的建模,就开始了TimeQuest的学习。自己以前也看过特权同学的《深入浅出玩转FPGA》一书,也看了看时序的静态分析,可能是笨的缘故,没有一点点的感觉,之后看了特权同学的《爱上FPGA...》一书的时序分析四部曲,对时序分析确实有感觉了,可是基础还是欠缺一点,那就好好看看--瞎搞TimeQuest和无责任笔记,感觉自己和时序分析的那张纸视乎真的被捅破了,真的假的,就让下面几张图和几个公式证明。

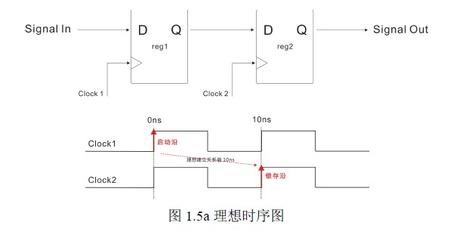

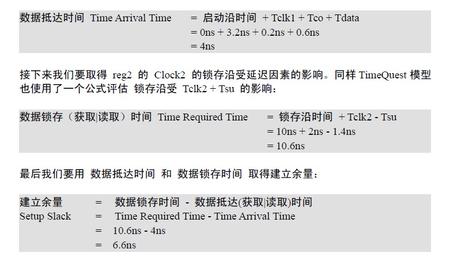

所谓的时序建立就是从时钟启动的那一刻开始到数据所存的那一刻所经过的时间。

上面三幅图将时序的建立时序分析的已经很清楚了,我们只需加以记忆,加以分析,就OK!!

下面我们看看保持时间的建立过程:

这是一张用屁股来求保持余量的公式图。最后我们用一张头和屁股的合体来看看数据保持的余量建立时序图。

最后真正理解了这几张图之后,我发现自己真的有点感觉了,哪怕是一点,反正就是有,真的,呵呵…

/5

/5

用户377235 2013-3-10 14:46