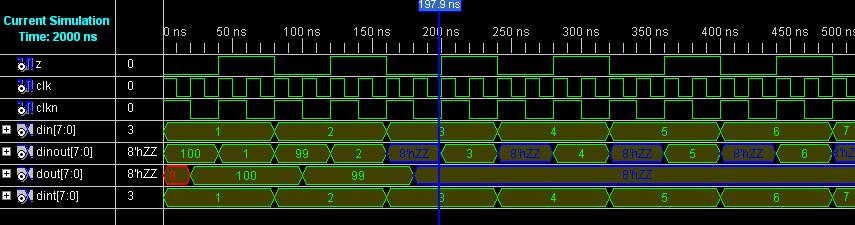

在做USB与上位机通信时,碰到一些时序问题,调试了近两周时间,最后将整个USB控制程序仿真发现了一些问题。INOUT端口总线的释放问题:也就是要确保INOUT端口的输入输出状态,保证时序的稳定性。

下面代码请结合附件源程序查看。

INOUT1完成测试的是INOUT端口的输入状态到输出状态转变;INOUT2完成测试的是INOUT端口的输入输出状态的连续转变。

测试文件里的RELEASE需要特别注意!不是输入状态到输出状态只需要让标志信号变化就可以了的,这里需要将总线释放。当然这里指的是测试仿真过程中,硬件里面具体变化还有待考证,这里给出目前所做一部分工作给需要的同学,希望能够相互学习讨论,谢谢!

----------------------------------------------------------------------------------------------------

TEST1 MODULE部分代码:

initial begin

// Initialize Inputs

clk = 0;

din = 0;

i = 0;

// Wait 100 ns for global reset to finish

#210;

release dinout;

#25

force dinout = 8'd20;

#35

release dinout;

#40

release dinout;

//#200 for (i=0;;i=i+1)

//#20 force dinout = dinout - 1;

//#200

//release dinout;

//#300 ;

//force dinout = 8'bz;

//#110 z= 0;

// Add stimulus here

end

always #10 clk = !clk;

always #20 din = din + 1;

TEST2 MODULE部分代码:

initial begin

// Initialize Inputs

clk = 1;

din = 8'd1;

// Wait 100 ns for global reset to finish

force dinout = 8'd100;

#40

release dinout;

#40 force dinout = 8'd99;

#40 release dinout;

// Add stimulus here

end

always #10 clk = !clk;

always #80 din = din + 1;

/5

/5

用户270837 2014-5-14 23:29

用户1494336 2013-7-4 13:38

用户403664 2012-6-18 15:05