0805与0603贴片电容封装差异与ESD验证通过性的内因研究

作者:韩增值

摘要:

本文通过研究0805与0603两种不同封装的常用贴片电容的内在差异,揭示了为何小封装的0603及0402的贴片电容在等容值的情况下,相较大些封装的0805电容出现更多的ESD验证不通性原因,从根本上说明端口电路电容在抗ESD设计时为何要优先0805封装,本文有助于硬件设计人员更好理解端口电容的选型要点及电容内部构造带来的设计注意事项,加深应用电路设计与器件选用的关键特性理解,减少设计的不确定性与失误发生,提高电路设计质量。

关键词:ESD、MLCC、贴片电容、汽车电路接口、静电击穿

引言:

在汽车电子电路设计中,需要考虑的是在ESD验证下产品的健壮性问题,当电路的设计不充分时,ESD作用下接口部分的电路器件将因为过载损坏,从而造成整个电子产品的功能失效。为了提供静电保护,常见的做法是在接口电路上使用保护器件,TVS抑制或电容吸收都是不错的方法,由于电容的成本较低,在一些对于信号的速率要求不高的场合下优先使用这种方法进行。随着电容制造的不断小型化,端口保护电容的封装从以往的1206渐渐转向了更小的封装,常用的是0805,也有使用了0603,到目前0402的引入,尽管在设计上设计人员会遵守使用相同容值的小封装电容,但实际ESD试验中多次证实了小封装的电容并不能有效保证通过验证,其中的原因根据差异识别可以理解为器件更小带来的,但更为深入的分析与解释并未从机理上进行根源阐述,从而对电容小型化的未来趋势如何判断缺乏更有力的说明分析,也难以深入理解为何有些车企标准中声明的接口电路推荐使用0805的原因,在客户要求与内部的成本利益上一直纠结,缺乏令人信服的判断依据。

1概述:

ESD作用下电路器件损坏的主要体现是端口的电容击穿或是电容出现较大的容值异常,说明电容已经在验证过程中损伤,无法长期保证正常了。而端口部分的电路异常一方面会影响到后面的工作电路是否正常,与对产品外的其它连接电路构成过载损伤或损坏,从而使车载系统出现不良率升高的问题。现有我司的设计主要是采用100nF的电容进行静电吸收的,目前使用最多的还是MLCC的构造电容,即片式多层陶瓷电容器(multilayer ceramic capacitor),在1uF以下的容值领域,这种电容很适合贴片生产,相比传统的直插电容贴片方式可以在SMT制造过程中全自动完成,减少了人工。另外MLCC电容体积小,成本也低,适于大规模生产。这种电容的一些特性决定了其在ESD中的承受程度,然而在器件的数据手册上并没有提到这些与ESD之间的关联性,而更深入的分析与理解电容在电路设计中的作用里有必要了解电容的构造与材料特点 ,通过这些关系的综合分析后可以分析清楚ESD下小封装电容的先天不足在哪里。

1.1ESD的主要特点与损害简述

以电压最高的验证25KV来看,其主要的电量是通过存储在一个100pF的高压电容内的,通过静电枪中串接的1.5k的电阻对被测产品进行放电测试,当产品里的电路构成对地的静电释放回路时,静电便会流经相关的电路器件。由于电压高在放电的回路中可以构成瞬间的大电流,大电流通过相应的器件时,由于器件的阻抗一般相较导线回路阻抗高,因而在器件上会形成较大的瞬间功率,这种较大的瞬间功率作用于器件而器件的能量释放不及时会积累成较高的热量,造成器件过载损坏,严重的还可以看到器件物理损坏,例如开裂、爆坑、熔融和断开内部连接线。对于电容器件其在ESD后的损坏主要是击穿,电特性为短路。由于电容中的极板间介质在静电后变异,由不导电转为受损坏或污染变异后的导电质或是开口使得两个极板搭在一起,形成电容的失效。而这种失效在后续的工作电压作用下又可能转变为严重的过载燃坏或是过载烧断,至使产品的功能失效。

1.2电容的主要参数与设计构造

电容的主要参数为容值、耐压值、容值偏差,目前贴片电容主要是多层陶瓷电容器。主要参数这块由于大家经常有接触就不再细讲,对于多层陶瓷电容器的内部构造进行介绍,有助于理解电容的主要参数是由哪些主要因素决定的。

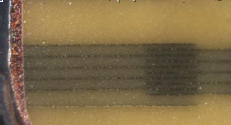

图片是一个贴片MLCC的切片放大图,左侧部分就是电容的端部,主要焊接的金属部分;中间可以看到有一些横着的线,这些线代表了从端部连接出来的导体,这些导体构成了多层结构;图的另一侧有不接触的水平横线,连接到电容的另一端,由于横线极板的平行位置形成了电容。黄色的是陶瓷,作为电介质隔开了两个极板,避免了短路情况。电容的容值主要是由于极板的平行相对面积决定的,由于贴片器件尺寸限制在较小的范围中,为了获得更多的极板平行相对面积,采用多层的办法使得总电容量可以得到增加。容值的另一个决定因素是电介质,由于贴片电容中对于极性并不做要求,因而多采用较便宜的陶瓷作为电介质,如果电介质换作其它的材料,电容的容值也会有所变化。极板层与层之间的间隔距离与介质的材料会影响电容的耐压值,一般讲间隔越大,耐压越高,但由于间隔增大后电容的容值又会显著减小,因而在容值与耐压之间往往要平衡选择,一般相同尺寸下小电容值的耐压往往容易做高,但容值增大后受器件尺寸的制约,耐压值会做的小些。关于容值偏差是因为层与层之间有尺寸波动,极板相对面积也会有波动再加上陶瓷介质也会有参数波动最终使得成品的电容值呈现偏差。

1.3电容对ESD的吸收耐受因素

通过上面的介绍可以得知ESD与电容在电路关系时主要考虑的是电容的电荷接纳大小能力(即容值大小)和电荷所在分布的极板间的介质是否可以承受的问题,如果这两方面都没有问题,则电容在ESD验证后就没有问题,而两者之一无法达到要求,则会加剧电容器件走向损坏。根据C=Q/U知道,当电容容值较大时,ESD下获得的电荷转变为加于电容两端的电压则低,极板间的电压低则电场低,对电介质的破坏就小或是不够成破坏。反之电容容值小,ESD后积累出来的电压就高,对电介质的损坏风险就大。电容对ESD的吸收耐受因素可以总结为电容容量,极板间的介电耐压能力。由于在本文中我们主要遇到的情况是电容值相同的不同封装电容在ESD验证下的通过与否差异,因而由上面的论述后可以把重点转为极板间的介电耐压能力来研究。

2分析:

由于我们采用比较的是同一品牌的不同封装贴片电容,我们可以认定电容所使用的主要设计结构与材料应该是相同的,只是由于结构中的一些参数发生变化,从而表现出ESD性能的差异。通过上面的说明已经使我们聚焦到了极板间的介电耐压能力下,接下来对这方面展开分析。

2.1极板尺寸与层数的差异分析

封装 尺寸 高度 容量 耐压 ESD后表现

0603 60X30mil 0.8mm 100nF 50V 失效

0805 80X50mil 1.25mm 100nF 50V 正常

通过上面的分析,主要的差异点是由于物理大小尺寸带来的ESD表现不同。一般目前做25V的耐压采用的是12um的层厚,0603封装下需要20层达到100nF【参考资料1】,如果做50V耐压则应该把层厚加大一倍,即24um,由于业内一般是25um工艺,我就取值25um 作为间隔,由于间隔加大容值会降为1/2,则为了达到100nF,使用的层数应该要做到40层。

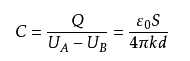

UA-UB为两平行板间的电势差,介电常数真空ε0=1,k为静电力常量8.987551×10^9,S为两板正对面积,d为两板间距离。C,单位为F(法拉)

根据40层,每层25um的分析数据可以得到整个电容的厚度应该是40X25=1000um=1mm,而实际0603尺寸只有0.8mm的高度,即使采用24um进行计算,也应该达到960um还是大于0.8mm的实际高度,说明极板的层间距做到了25um以下,大约是800/40=20um的样子。

反观0805封装大小,其尺寸长宽的面积本身就相对于0603要大,这个优势足以使极板面积多出120%的电容,同时降低了其对于高度的要求。即使采用与0603一样的极板面积进行设计,其高度有1.25mm,也可以满足上面计算得出的1mm厚度要求。因而在0805的封装下相较0603封装可以获得更大的极板间的介电耐压能力。

按0603高度0.8mm共计40层的情况20um最大的极板间隔考虑,陶瓷材料的典型介电数值为80kV/cm,则0603的50V耐压电容的介电耐压能力为80/(10000/20)=0.16kV=160V

而0805的尺寸面积可以扩大到2倍,则其层数就可以降到40层的一半即20层就足够达到相同的容值,间隔可以适当放宽,同时增加层数来达到相同的容值。以采用的典型的制作25um进行计算,采用40层的方式,厚度为1mm仍在1.25mm的高度范围中,相应的极板面积扩大到1.25倍就可以抵消25um 带来的影响,实现100nF,50V耐压的电容成品要求。产品的介电耐压能力为80/(10000/25)=200V

这里计算出来了由于0603电容与0805 电容在高度与尺寸长宽的不同,内部结构的设计在极板大小与间隔上进行差异化后最终会体现出介电耐压能力分别为160V与200V的差别。

封装 极板尺寸极限 极板间距 层数 介电耐压 ESD后表现

0603 60X30mil 20um 40 160V 失效

0805 60X30X1.25mil 25um 40 200V 正常

2.2ESD下对介电耐压能力差别的影响

根据上面的公式可以得知,在ESD的放电模型下,静电枪中100pF的高压电容与1.5k的高压限流电阻构成与外界端口电容的ESD测试。接口上采用的100nF电容吸收静电设计与静电枪中的100pF的高压电容构成分压吸收。根据电量总量不变的原理,100nF上的电容在吸收电荷后积累形成的电压将达到25000*100/100000=25V,这个电压并不高,并不会构成损坏电容。但是ESD的本质并不是缓慢充电的过程,由于ESD的上升延只有1ns,整个周期也在100ns内完成,是个窄脉冲,在对电容充电的过程中更像是对40个并着的小电容进行充电,单个小电容的容量约为2.5nF,这样来估算的话对应的放电值约为1000V。考虑到层叠结构的双面电容分布情况,一侧的极板对应边上的两个极板面,得到的电容值就可以有5nF,又考虑到变化的电流下趋肤效应(1G时约2um),主要的电极板应该在两侧的两个极板,电容约大于10nF,这样的电压会降到250V左右。由于电容截面两侧的分流大约是0.5倍的上下两面的分流情况,电容按接近15nF估算,换算出的获得电压约167V。这个值小于0805的介电耐压值200V,而略大于0603的介电耐压值160V,故出现的情况往往是0805封装的电容可以经受ESD测试,而0603封装的电容在一些情况下介电耐压值波动到较有利的情况下可以满足测试,而一些情况下无法通过ESD测试的情况。

结论:由于贴片电容的多层结构受制造工艺及材料的介电层间距差异影响,较大封装的MLCC电容由于可以采用更大的层与层间隔使其ESD表现优于较小封装的MLCC电容。所以在接口电路的设计中目前采用0805封装的设计仍具有ESD参数的优势。

参考资料:

1、多层陶瓷电容(MLCC)的基本原理 深圳宏力捷PCBA部 2016-07-20

http://www.greattong.com/archives/view-461-1.html

2、能够击穿空气的电压

https://www.zhihu.com/question/20072799

作者: youreneet, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3854496.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/4

/4

文章评论(0条评论)

登录后参与讨论