分享个人的ESD保护9大措施

最近在做电子产品的ESD测试,从不同的产品的测试结果发现,这个ESD是一项很重要的测试:如果电路板设计的不好,当引入静电后,会引起产品的死机甚至是元器件的损坏。以前只注意到ESD会损坏元器件,没有想到,对于电子产品也要引起足够的重视。

ESD,也就是我们常说的静电释放(Electro-Static discharge)。从学习过的知识中可以知道,静电是一种自然现象,通常通过接触、摩擦、电器间感应等方式产生,其特点是长时间积聚、高电压(可以产生几千伏甚至上万伏的静电)、低电量、小电流和作用时间短的特点。对于电子产品来说,如果ESD设计没有设计好,常常造成电子电器产品运行不稳定,甚至损坏。

在做ESD放电测试时通常采用两种方法:接触放电和空气放电。

接触放电就是直接对待测设备进行放电;空气放电也称为间接放电,是强磁场对邻近电流环路耦合产生。这两种测试的测试电压一般为2KV-8KV,同地区要求不一样,因此在设计之前,先要弄清楚产品针对的市场。

以上两种情况是针对人体在接触到电子产品时,因人体带电或其他原因引起电子产品不能工作而进行的基本测试。下图是一些地区在一年中不同月份的空气湿度统计。从图中可以看出Lasvegas全年的湿度最少,该地区的电子产品要特别注意ESD的保护。

全球各地的湿度情况不一样,但是同时在一个地区,若空气湿度不一样,产生的静电也不相同。下表是搜集到的数据,从中可以看出静电随着空气湿度的减小而变大。这也间接的说明北方的冬天,脱毛衣时产生的静电火花很大的原因。“既然静电这么大的为危害,我们如何进行防护呢?我们在进行静电防护设计时通常分三步走:防止外部电荷流入电路板而产生损坏;防止外部磁场对电路板产生损坏;防止静电场产生的危害。

在实际电路设计中我们会采用以下几种方法的一种或几种来进行静电保护:

1雪崩二极管来进行静电保护

这也是设计中经常用到的一种方法,典型做法就是在关键信号线并联一雪崩二极管到地。该法是利用雪崩二极管快速响应并且具有稳定钳位的能力,可以在较短的时间内消耗聚集的高电压进而保护电路板。

2使用高压电容进行电路保护

该做法通常将耐压至少为1.5KV的陶瓷电容放置在I/O连接器或者关键信号的位置,同时连接线尽可能的短,以便减小连接线的感抗。若采用了耐压低的电容,会引起电容的损坏而失去保护的作用。

3采用铁氧磁珠进行电路保护

铁氧磁珠可以很好的衰减ESD电流,并且还能抑制辐射。当面临着两方面问题时,一个铁氧磁珠会时一个很不错的选择。

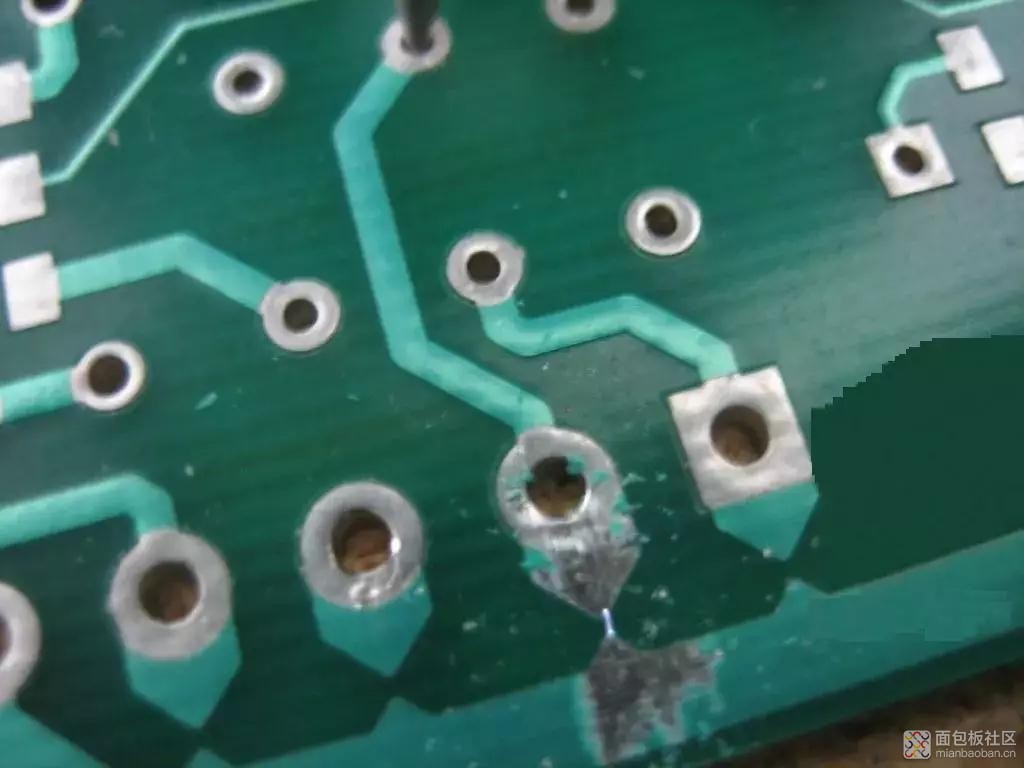

4火花间隙法

这种方法是在一份材料中看到的,具体做法是在铜皮构成的微带线层使用尖端相互对准的三角铜皮构成,三角铜皮一端连接在信号线,另一个三角铜皮连接地。当有静电时会产生尖端放电进而消耗电能。

5采用LC滤波器的方法进行保护电路

LC组成的滤波器可以有效的减小高频静电进入电路。电感的感抗特性能很好的抑制高频ESD进入电路,而电容有分流了ESD的高频能量到地。同时,该类型的滤波器还可以圆滑信号边缘而较小RF效应,性能方面在信号完整性方面又有了进一步的提高。

6多层板进行ESD防护

当资金允许的情况下,选择多层板也是一种有效防止ESD的一种手段。在多层板中,由于有了一个完整的地平面靠近走线,这样可以使ESD更加快捷的耦合到低阻抗平面上,进而保护关键信号的作用。

7电路板外围留保护带的方法保护法

这种方法通常是在电路板周围画出不加组焊层的走线。在条件允许的情况下将该走线连接至外壳,同时要注意该走线不能构成一个封闭的环,以免形成环形天线而引入更大的麻烦。

8采用有钳位二极管的CMOS器件或者TTL器件进行电路的保护

这种方法是利用了隔离的原理进行电路板的保护,由于这些器件有了钳位二极管的保护,在实际电路设计中减小了设计的复杂度。

9多采用去耦电容

这些去耦电容要有低的ESL和ESR数值,对于低频的ESD来说,去耦电容减小了环路的面积,由于其ESL的作用使电解质作用减弱,可以更好的滤除高频能量。

总之,ESD虽然可怕,甚至会带来严重后果,但是,只有保护好电路上电源和信号线,那么就能有效的防止ESD的电流流入PCB中。其中,我老大经常说的一句“一个板子的良好接地才是王道”,希望这句话也能给大家带来打破天窗的效果。

下面将提到更多保护细节:

■尽可能使用多层PCB,相对于双面PCB而言,地平面和电源平面,以及排列紧密的信号线-地线间距能够减小共模阻抗和感性耦合,使之达到双面PCB的 1/10到1/100。尽量地将每一个信号层都紧靠一个电源层或地线层。对于顶层和底层表面都有元器件、具有很短连接线以及许多填充地的高密度PCB,可以考虑使用内层线。

■对于双面PCB来说,要采用紧密交织的电源和地栅格。电源线紧靠地线,在垂直和水平线或填充区之间,要尽可能多地连接。一面的栅格尺寸小于等于60mm,如果可能,栅格尺寸应小于13mm。

■确保每一个电路尽可能紧凑。

■尽可能将所有连接器都放在一边。

■如果可能,将电源线从卡的中央引入,并远离容易直接遭受ESD影响的区域。

■在引向机箱外的连接器(容易直接被ESD击中)下方的所有PCB层上,要放置宽的机箱地或者多边形填充地,并每隔大约13mm的距离用过孔将它们连接在一起。

■在卡的边缘上放置安装孔,安装孔周围用无阻焊剂的顶层和底层焊盘连接到机箱地上。

■PCB装配时,不要在顶层或者底层的焊盘上涂覆任何焊料。使用具有内嵌垫圈的螺钉来实现PCB与金属机箱/屏蔽层或接地面上支架的紧密接触。

■在每一层的机箱地和电路地之间,要设置相同的“隔离区”;如果可能,保持间隔距离为0.64mm。

■在卡的顶层和底层靠近安装孔的位置,每隔100mm沿机箱地线将机箱地和电路地用1.27mm宽的线连接在一起。与这些连接点的相邻处,在机箱地和电路地之间放置用于安装的焊盘或安装孔。这些地线连接可以用刀片划开,以保持开路,或用磁珠/高频电容的跳接。

■如果电路板不会放入金属机箱或者屏蔽装置中,在电路板的顶层和底层机箱地线上不能涂阻焊剂,这样它们可以作为ESD电弧的放电极。

■要以下列方式在电路周围设置一个环形地:

(1)除边缘连接器以及机箱地以外,在整个外围四周放上环形地通路。

(2)确保所有层的环形地宽度大于2.5mm。

(3)每隔13mm用过孔将环形地连接起来。

(4)将环形地与多层电路的公共地连接到一起。

(5)对安装在金属机箱或者屏蔽装置里的双面板来说,应该将环形地与电路公共地连接起来。不屏蔽的双面电路则应该将环形地连接到机箱地,环形地上不能涂阻焊剂,以便该环形地可以充当ESD的放电棒,在环形地(所有层)上的某个位置处至少放置一个0.5mm宽的间隙,这样可以避免形成一个大的环路。信号布线离环形地的距离不能小于0.5mm。

■在能被ESD直接击中的区域,每一个信号线附近都要布一条地线。

■I/O电路要尽可能靠近对应的连接器。

■对易受ESD影响的电路,应该放在靠近电路中心的区域,这样其他电路可以为它们提供一定的屏蔽作用。

■通常在接收端放置串联的电阻和磁珠,而对那些易被ESD击中的电缆驱动器,也可以考虑在驱动端放置串联的电阻或磁珠。

■通常在接收端放置瞬态保护器。用短而粗的线(长度小于5倍宽度,最好小于3倍宽度)连接到机箱地。从连接器出来的信号线和地线要直接接到瞬态保护器,然后才能接电路的其他部分。

■在连接器处或者离接收电路25mm的范围内,要放置滤波电容。

(1)用短而粗的线连接到机箱地或者接收电路地(长度小于5倍宽度,最好小于3倍宽度)。

(2)信号线和地线先连接到电容再连接到接收电路。

■要确保信号线尽可能短。

■信号线的长度大于300mm时,一定要平行布一条地线。

■确保信号线和相应回路之间的环路面积尽可能小。对于长信号线每隔几厘米便要调换信号线和地线的位置来减小环路面积。

■从网络的中心位置驱动信号进入多个接收电路。

■确保电源和地之间的环路面积尽可能小,在靠近集成电路芯片每一个电源管脚的地方放置一个高频电容。

■在距离每一个连接器80mm范围以内放置一个高频旁路电容。

■在可能的情况下,要用地填充未使用的区域,每隔60mm距离将所有层的填充地连接起来。

■确保在任意大的地填充区(大约大于25mm×6mm)的两个相反端点位置处要与地连接。

■电源或地平面上开口长度超过8mm时,要用窄的线将开口的两侧连接起来。

■复位线、中断信号线或者边沿触发信号线不能布置在靠近PCB边沿的地方。

■将安装孔同电路公地连接在一起,或者将它们隔离开来。

(1)金属支架必须和金属屏蔽装置或者机箱一起使用时,要采用一个零欧姆电阻实现连接。

(2)确定安装孔大小来实现金属或者塑料支架的可靠安装,在安装孔顶层和底层上要采用大焊盘,底层焊盘上不能采用阻焊剂,并确保底层焊盘不采用波峰焊工艺进行焊接。

■不能将受保护的信号线和不受保护的信号线并行排列。

■要特别注意复位、中断和控制信号线的布线。

(1)要采用高频滤波。

(2)远离输入和输出电路。

(3)远离电路板边缘。

■PCB要插入机箱内,不要安装在开口位置或者内部接缝处。

■要注意磁珠下、焊盘之间和可能接触到磁珠的信号线的布线。有些磁珠导电性能相当好,可能会产生意想不到的导电路径。

■如果一个机箱或者主板要内装几个电路板,应该将对静电最敏感的电路板放在最中间

更多咨询大家可以登入捷配PCB官网查询:www.jiepei.com/G062

/5

/5

curton 2019-4-24 17:15

测量无处不在 2019-4-8 15:48