随着对车载高速总线的深入研究,以电信号为媒介的传输方式逐渐显露出劣势,当传输速率超过25Gbps时,基于电信号传输已经很难保证长距离传输下的信号质量与损耗。在这样的背景下,应用于工业领域的光通信技术因其高带宽、长距离、低电磁干扰的特点得到了密切的关注,IEEE在2023年发布了802.3cz[1]协议,旨在定义一套光纤以太网在车载领域的应用标准。

MultiGBASE-AU总览

以下是MultiGBASE-AU在OSI模型以及以太网层级中的位置:

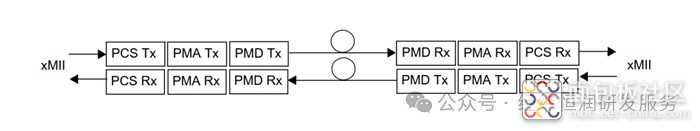

MultiGBASE-AU基于一对多模玻璃光纤进行通信,两根光纤分别对应了发送和接收,因此,MultiGBASE-AU的通信形式同样是全双工通信。同样地,由于两根光纤相对独立地连接着PHY自身的发射机和对方的接收机,MultiGBASE-AU并没有主从的概念,通信过程中,两个PHY的PMA RX都需要进行时钟恢复。

从上图中可以看到,从介质无关接口(xMII)传输下来的数据,通过PCS TX的编码及RS-FEC、PMA TX的电信号调制,PMD TX的电光转换后,转变为光信号传输至链路伙伴进行光电转换、解调、解码。在PMA TX的调制方式上,2.5G/5G/10G/25GBASE-AU采用的是NRZ编码,50GBASE-AU采用的是PAM4编码。

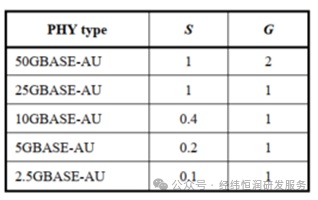

与MultiGBASE-T1类似的是,同样包含了多个速率的MultiGBASE-AU在PHY的相关参数设定上,也通过缩放参数S(Scaling Parameter)对参数进行缩放,不一样的是,由于50GBASE-AU的特殊性,802.3cz规定了另一个参数:分组参数G(Grouping Parameter)用于区分调制方式。

XG/25G、50GMII

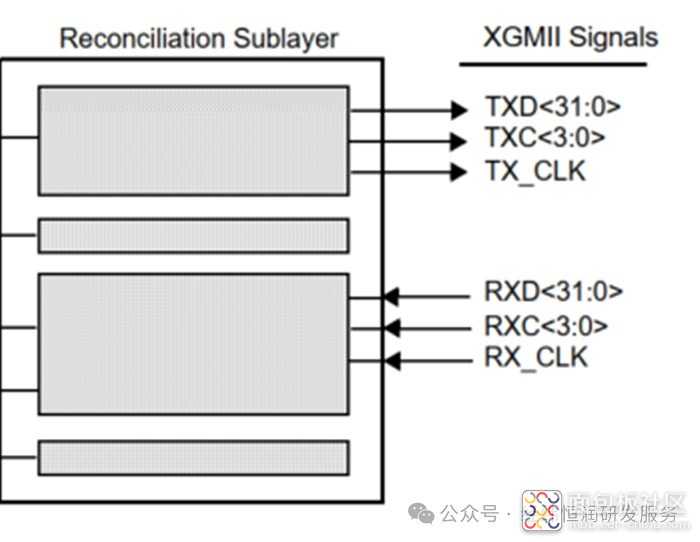

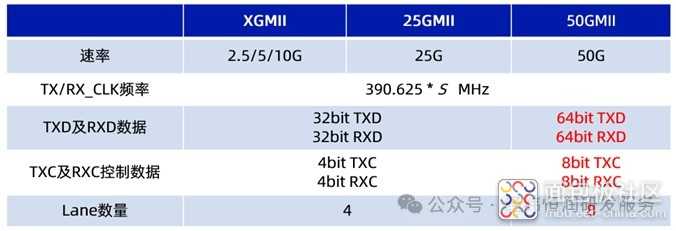

在介质无关接口的定义上,802.3cz中包含了XGMII、25GMII、50GMII三种,其中,对于XGMII的介绍,可以参考《MultiGBASE-T1协议解读系列(上):车载以太网多G物理层概述》。

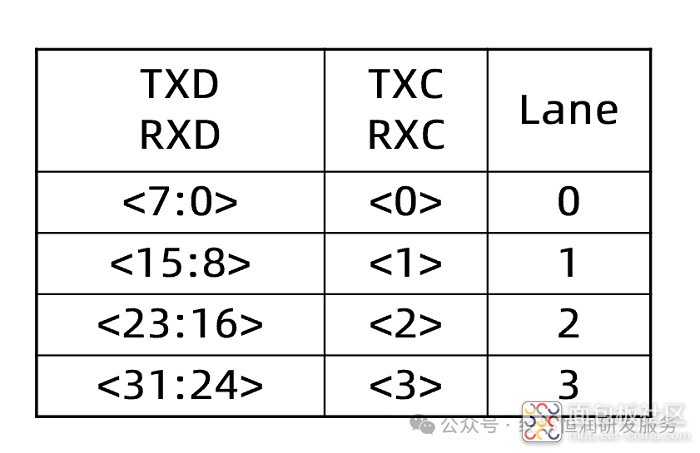

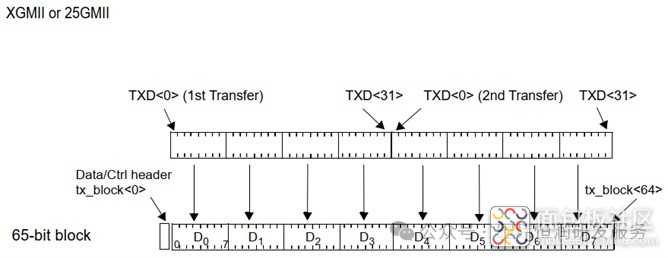

25GMII与XGMII在数据和控制字符的设定上完全一致,同样包括了32bit TXD,32bit RXD,4bit TXC以及4bit RXC。在机制上同样是将32bit数据字符划分为四个虚拟的Lane,每个Lane通过一个控制字符指示信号内容(data或ctrl)。在时钟频率上,25GMII的时钟频率为390.625 MHz。

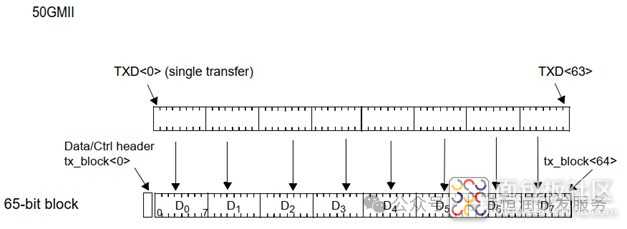

50GMII的时钟速率与25GMII相同,主要的改动点在于将数据字符、控制字符和Lane的数量进行了翻倍。下表是对三者相关参数的对比,时钟速率可以通过缩放参数S进行计算:

PCS子层

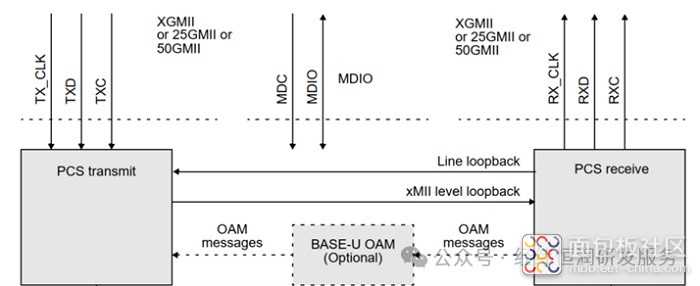

PCS子层位于协调子层(通过xMII)和PMA子层之间,MultiGBASE-AU的PCS子层包括了PCS Transmit和PCS Receive两个部分。802.3cz中定义的两个可选功能:节能以太网(EEE)与运行管理维护(OAM)也需要PCS子层的部分机制实现。

· PCS Transmit功能

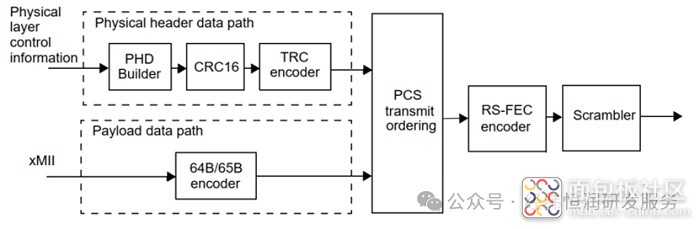

与MultiGBASE-T1不同的是,MultiGBASE-AU的PCS子层引入了一个新的概念:Physical header data物理层头部,简称PHD,包含了物理层传输模式,链路状态、OAM信息等内容。通过XMII传输并经过64/65B编码后的数据会与PHD进行组合,经过RS-FEC编码以及扰码器的扰码后,发送至PMA子层。

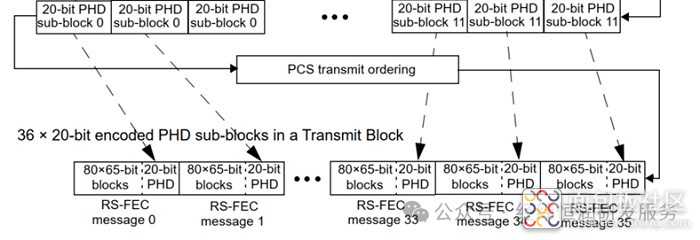

由于PHD与Payload的组合方式是将PHD拆开插入Payload,因此将一个完整的PHD与Payload data组合,经过后续编码形成的数据被称为一个Transmit Block。

接下来我们将分别从上图中的Physical header data path与Payload data path了解一下PCS发送数据的组成与编码方式。

物理层头部数据主要用于链路双方交换发送模式、接收数据可靠性,link状态,OAM信息等,共224bit,其构成如下表所示:

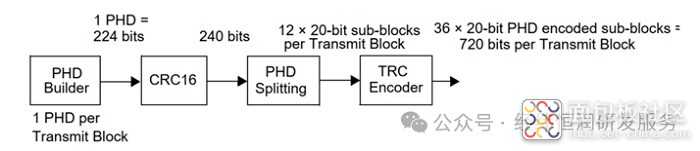

与Payload data组合之前,PHD data还需要经过CRC16、PHD Splitting以及TRC Encoder三个流程。加入CRC16校验码的240bit数据会被PHD Splitting分割成12个20bit的子模块。TRC Encoder则是将每个子模块复制为三份形成36个20bit子模块。因此,一个完整的PHD data包含了720bit数据。

在进行64/65B编码之前,来自XMII的Payload data还需要进行映射,对于分组参数G=1的速率,需要将两个发送周期的数据组合为一个64bit block,再进行编码。对于G=2的速率则是使用一个发送周期的数据直接进行编码。

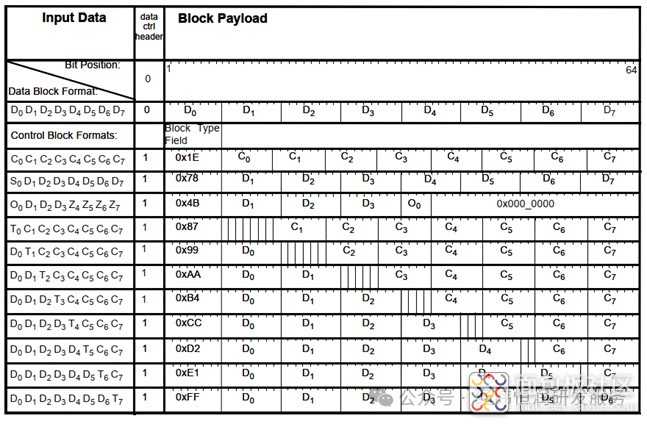

64/65B编码的规则与MultiGBASE-T1的PCS子层编码规则一致,可详见《MultiGBASE-T1协议解读系列(中):MultiGBASE-T1 PCS子层》。需要特殊注意的是,由于50GMII上一个发送周期的数据是64bit,不会出现Start字符在65bit中间的情况,因此50G速率下,64/65B编码的block格式与其他速率不同,如下图所示。

经过64/65B编码后,每80个65B数据组成一个模块,一个Transmit Block中包含了36个模块,共187200bit。这36个模块的末尾插入一个PHD的子模块后,这段长度为5220bit的数据被称为一个Codeword,接下来的RS-FEC前向纠错就是以Codeword为单位进行的。

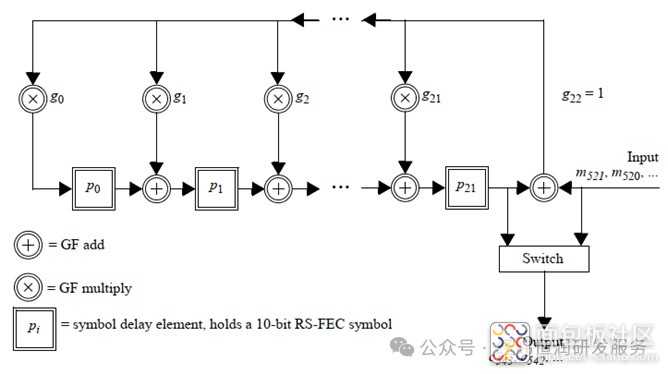

MultiGBASE-AU的RS-FEC采用(544,522,10),即10bit一组,将5220bit分为522组进行RS-FEC的计算,计算完成后引入22组前向纠错码,共输出5440bit数据。

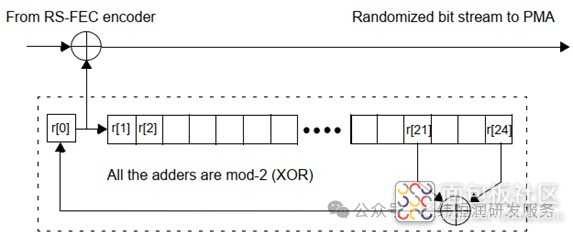

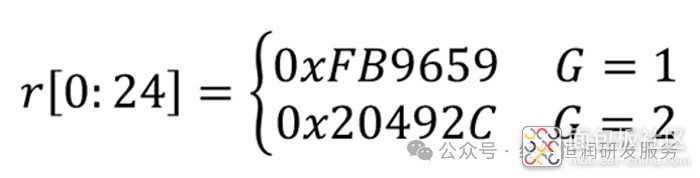

完成RS-FEC编码后的36Codeword数据会通过一个25位的移位寄存器进行扰码。

由于分组参数G=1和G=2采用了不同的调制方式,为了平衡电平分布,二者的扰码种子也不同。

· PCS Receive功能

PCS Receive在构成上与PCS Transmit基本相同,只是方向相反,从PMA Receive收到数据后,首先要进行解扰码,然后分割成36个Codeword,进行RS-FEC的校验纠错,确认数据无误会将PHD和Payload分开,Payload映射到XMII的通道上进行传输,PHD则进行TRC解码、PHD组合、CRC16校验得到完整的PHD。

结语

以上便是介绍的MultiGBASE-AU物理层中XMII及PCS子层的全部内容,在下一篇文章中,我们将介绍MultiGBASE-AU两个可选功能:EEE及OAM的相关内容。这部分内容是如何实现的,与MultiGBASE-T1的EEE和OAM功能会有什么差别呢?敬请关注下期:一文读懂光纤以太网IEEE 802.3cz-中。

经纬恒润作为OPEN联盟会员和AUTOSAR联盟的高级合作伙伴,长期为国内外各大OEM和供应商提供涵盖TCP/IP、SOME/IP、DoIP、AVB、TSN、DDS等技术领域的设计和测试咨询服务,积极研发和探索车载网络前沿技术的工程应用。通过多个项目的实践经验,已建立了高质量、本土化的设计与测试一体化解决方案,为整车网络架构提供可靠支持。

参考文献

[1] IEEE, 802.3cz-2023, " IEEE Standard for Ethernet, Amendment 7: Physical Layer Specifications and Management Parameters for Multi‐Gigabit Glass Optical Fiber Automotive Ethernet ", 2023.

了解更多

请致电 010-64840808转6117或发邮件至market_dept@hirain.com(联系时请说明来自面包房社区)

作者: 经纬恒润, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3882431.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/5

/5

文章评论(0条评论)

登录后参与讨论