半导体行业正在开发下一波原子层蚀刻(ALE)应用,希望能在一些新的新兴市场站稳脚跟。

ALE 是下一代蚀刻技术,可去除原子级材料,是晶圆厂里制造先进器件所需的几种工具之一。在 2016 年前后,因为特定应用,ALE 开始投入生产,但由于该技术较低的工艺速度,因此仍未得到广泛部署。现在,业界正在研究 ALE在内存和逻辑领域,以及 III-V 材料和异质金属方面的新应用。只要ALE 能够克服一些挑战,它有机会突破这些市场。

ALE 是当前市场上几种主要蚀刻技术之一。蚀刻本身要与沉积配合使用。在芯片生产中,芯片制造商使用沉积系统将材料沉积在晶圆上。然后,再使用蚀刻系统,通过化学工艺去除不需要的材料。主流蚀刻工具称为反应离子蚀刻(RIE),用于芯片生产已有几十年的历史。基本上,基于 RIE 的蚀刻系统会连续去除设备中的材料。

在高级节点上,RIE 蚀刻器和其他设备用于芯片制造,然而也存在一些挑战。随着每个节点的芯片尺寸变小,芯片制造商只做原子级的工艺处理。因此,在晶圆厂中,芯片制造商使用在原子级工艺设备,即原子层沉积(ALD)和 ALE。ALD是一种成熟的技术,用于沉积原子级的薄膜。

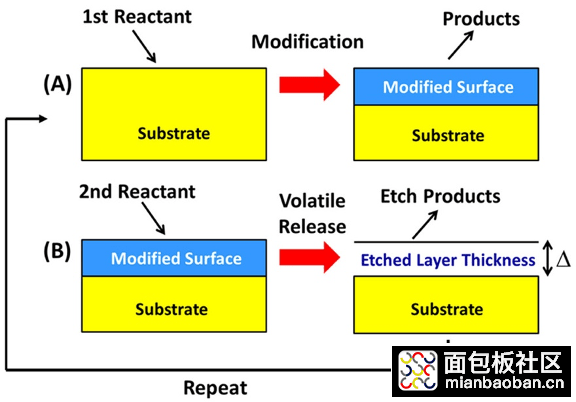

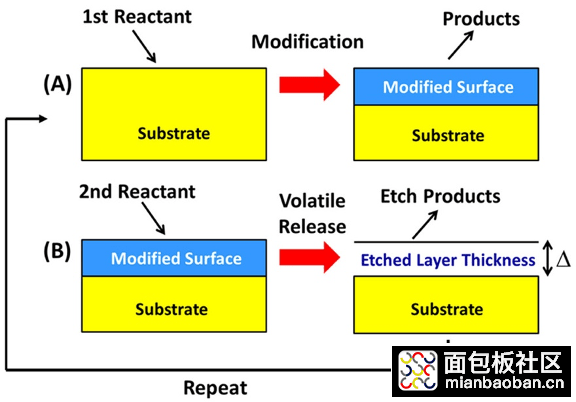

ALE 则更新更不成熟。通常,供应商提供独立的 ALE 设备,或将这些工艺集成到基于 RIE 的蚀刻设备中。通常采用两步工艺,通过ALE 有选择地去除原子级的目标材料,而不会损坏结构的其他部分。"有了 ALE,你隔离了不同的工序,"Lam Research的 CTO Rick Gottscho 解释道。通过将时间和空间上的东西分开,现在您已经将问题分解成更小的部分,每个部分都可以独立进行优化。

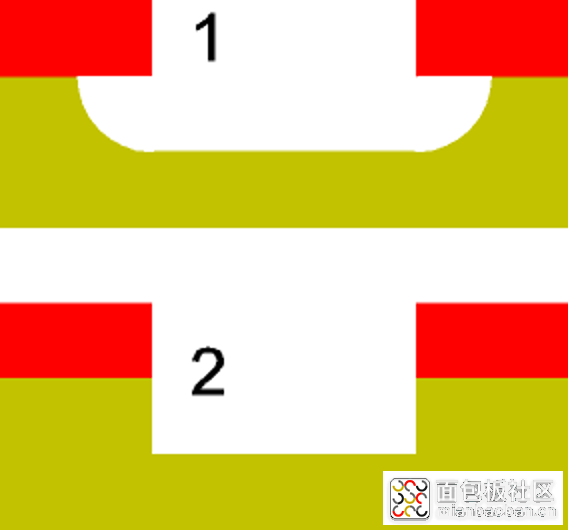

图1:基于连续表面改性及挥发性释放反应的 ALE 工艺原理图。资料来源:科罗拉多大学

与 RIE 蚀刻工具不同,ALE 并非适用于晶圆厂内任何器件制造。"ALE 在某些方面有适用价值,例如内存等。但是,当你需要它无所不适、无处不在时,它就很难被广泛使用,"VLSI研发总裁Risto Puhakka说。"与整体蚀刻市场相比,ALE 的市场规模仍然相当有限。开发新技术需要时间。

尽管ALE被认为是个宝贵工具,但它却不能解决fab里的每一个问题。因此,在研发领域,围绕着ALE展开了一系列活动。在最近举行的 ALD/ALE 2020 大会上,公司、研发机构和大学就 ALE 的下一步工作发表了各种论文。它们包括:

等离子体ALE执行定向蚀刻(各向异性),正在生产,并扩展到传统硅以外的应用,如氮化铀(GaN)和耐火金属。

热ALE,执行单向蚀刻(等向),仍处于起步阶段。一些公司的目标是下一代晶体管的热 ALE。

科罗拉多大学介绍了金属栅、电介质等的热 ALE 研究工作。

特拉华大学介绍了金属和合金的热 ALE 工作。其他人也在开发这项技术。

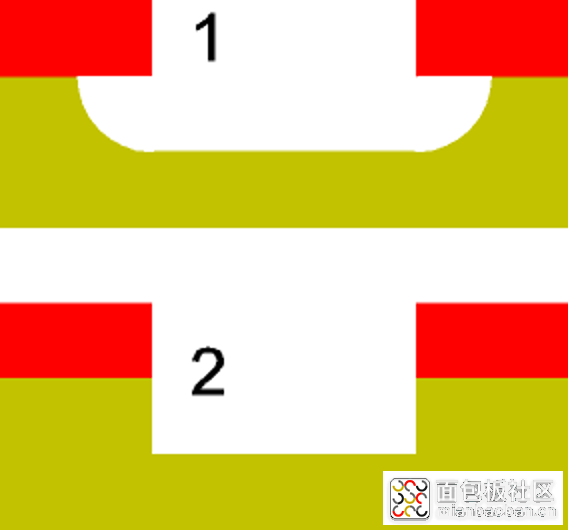

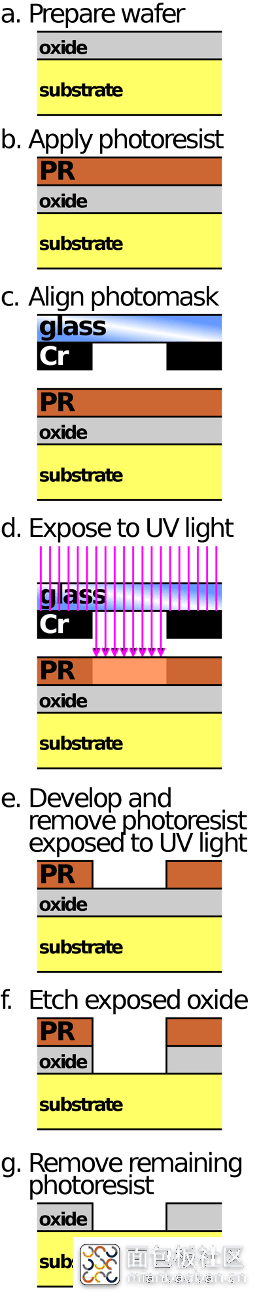

图2:等向或单向蚀刻(上)与各向异性或定向蚀刻(下图) 来源:维基百科

什么是蚀刻?

VLSI Research表示,尽管商业环境艰难,但2020年半导体设备市场预计将达到827亿美元,比2019年增长7.3%。VLSI研究公司首席执行 DanHucheson 表示:"由于中国的大力推动,刻蚀设备业务非常强劲。中国设备行业的增长正在抵消其他地方带来的疲软。

VLSI Research表示,预计2020年蚀刻市场将达到120亿美元左右,比2019年增长8%。到2021年,蚀刻市场将增长6%。

VLSI的研究表明,根据市场份额,"三大"蚀刻供应商是应用材料,Lam Research 和TEL。AMEC、日立高科技( Hitachi High-Tech)、KLA等也参与着激烈的市场竞争。

根据VLSI Research的研究,在整体蚀刻市场,ALE规模仍然很小,仅代表着"数亿美元"的业务。应用材料,Lam Research 和TEL是主要 ALE 玩家。日立、牛津(Oxford)等参与了竞争。

蚀刻并不是一项新技术。它可追溯到20世纪60年代末,当时,Signetics在等离子体蚀刻方面进行了早期工作。然后,在1970和1980年代,出现了几个商业蚀刻供应商。20世纪80年代,大学开始探索ALE。

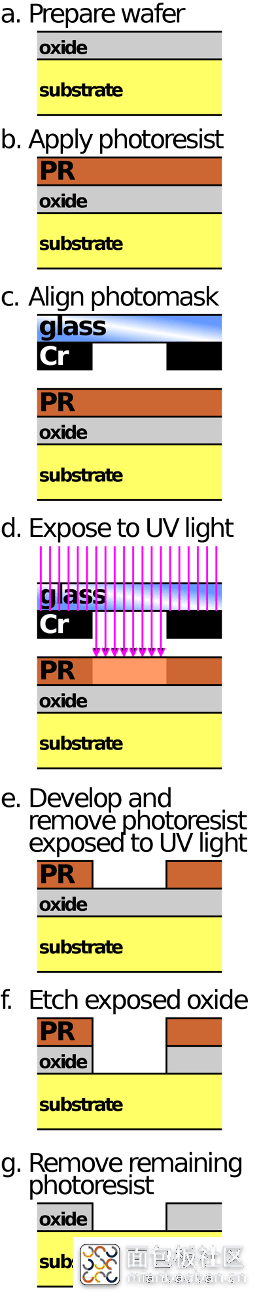

在技术方面,蚀刻市场分为两类-湿法蚀刻和干法蚀刻。湿法蚀刻使用液体化学品去除材料。干法或等离子蚀刻占据了两类市场里的大头,它们还包括了ALE 和 RIE。

在晶圆厂,主力蚀刻工具基于 RIE 技术。在 RIE 蚀刻系统中,晶圆位于具有等离子源的反应堆中。气体被引入系统,等离子体分解气体,产生离子和反应中性物种。然后,离子和物种轰炸晶圆的预定义部分,从而去除材料。

几年前,工艺很简单。RIE 蚀刻器只需在单个材料中蚀刻沟槽或其他结构即可。

图3:干蚀刻工艺的简化图解。资料来源:维基百科

而今逻辑和内存器件更为复杂,这给蚀刻和其他设备带来了一些挑战。以3D NAND为例。与平面 NAND(2D 结构)不同,3D NAND 类似于垂直摩天大楼,其中存储单元的水平层堆叠起来,然后使用微小的垂直通道进行连接。

3D NAND 根据器件中堆叠的层数进行衡量。随着添加更多图层,位密度将增加。如今,供应商正在运送 96 层 3D NAND 设备,并生产 128 层产品。

"由于3D NAND闪存,新一代非易失性固态存储在几乎所有可以想象到的电子设备中广泛应用,"Coventor(Lam Research的子公司)软件应用工程师Timothy Yang说。3D NAND 可以实现超过 2D NAND 结构的数据密度,即使使用下一代技术节点制造工艺。

但在 3D NAND 中,存在一些沉积和蚀刻挑战。首先,供应商将交替薄膜沉积在基材上。该工艺需要重复多次,直到达到设定器件所需的层数。然后,使用 RIE 蚀刻器,从设备堆栈顶部钻取到基板的微小通道。96 层设备的纵横比为 50:1。

每个小通道必须平行且均匀,这是一项具有挑战性的任务。KLA产品营销总监Efi Megged说:"你不仅必须控制CD和覆盖,还要解决与这些新的和非常高的设备结构的配置文件控制相关的挑战。

除了3D NAND,先进的晶体管、DRAM和新型存储器类型也具有具有不同材料的复杂结构。

为了应对这些挑战,芯片制造商需要先进的 RIE 蚀刻工具。这些工具必须处理多种工艺流程。芯片制造商在每个工艺中都调整蚀刻。

"蚀刻设备约有 300 个传感器。有的是力传感器,有的是化学品和流速。很多不同的参数在控制蚀刻设备。"TEL美国公司副总裁兼副总经理本·拉萨克(Ben Rathsack)在最近的一次演讲中说:"使用不同的化学品进行某些轮廓刻蚀,特别是对于高纵横比蚀刻。这正变得极其关键。

转向ALE

除了 RIE 蚀刻设备外,芯片制造商还使用 ALE 进行高级芯片生产。当今的先进芯片由三部分组成——晶体管、触点和互连。晶体管用作开关。

互连位于晶体管的顶部,由微小的铜线方案组成,将电信号从一个晶体管传输到另一个晶体管。然后,一个称为中间线的层使用微小的接触结构连接晶体管和互连件。

在每个节点上,晶体管结构变得越来越小和复杂。TEL高级技术人员罗伯特·克拉克(Robert Clark)在 ALD/ALE 2020 大会上的演讲中表示:"目前,我们向更小尺寸发展,正在接近以原子为单位的量级。“

这反过来又带来了一些沉积和蚀刻的挑战。"结构变得越来越高,越来越薄。一些工艺需要围绕曲线和底层操作,那些地方我们甚至看不到要沉积的层,"克拉克说。

不过还是有一些解决方案。"一种方法是引入我提到的自对准技术。需要自我对齐的结构,使我们能够实施工艺,例如,从一个金属层到另一个水平的通孔,"他说。"我们需要原子尺度技术,如原子层沉积(ALD)和原子层蚀刻(ALE),以控制高纵横比结构的厚度,达到良好的一致性。

ALD 用于将材料沉积在表面上,一次一个单层。这是一个缓慢但可靠的工艺。多年来,在逻辑和内存方面芯片制造商一直使用 ALD 。

ALE 也很缓慢,但与 ALD 正好相反。它使用两步自限制工艺,ALE 可去除材料。在某些情况下,ALD 和 ALE 可以在同一流程中协同工作。

经过多年的研发,ALE终于在2016年前后投产。最初,该技术用于芯片中的自对齐接触点。现已扩展到其他领域。

例如,考虑具有微小间隙的结构。ALE 用于形成这些间隙,这些间隙随后充满钴。该工艺涉及在表面上输送反应物,然后使用第二反应物去除材料并形成间隙。ALE 的诀窍是在于完成工艺却不损坏结构的其他部分。

在 Lam 的 ALE 示例中,晶圆位于 ALE 系统中的腔室中。第一步是将氯气注入腔室的硅表面。氯分子被吸收在表面,这反过来又改变表面。然后,离子被注入到腔室刻蚀表面,并去除修改后的层,据Lam介绍说。

"有了 ALE,可以拿掉被修改的层,可以放入一些能量来源,然后进行选择性处理,"Lam的 Gottscho 说。"可以通过离子实施,或者可以通过温度实施,或者可以用光子实施。您将在基础层和修改的基板之间切割键合。它们比基板本身的键弱,这就是为什么你要一次删除"一层"。这里的引号意思是,它通常是多个图层,因为修改曲面会有一些深度,不仅仅是一个图层。

ALE 有等离子体ALE和热ALE两种类型。正在生产的等离子ALE能够实现定向或各向异性蚀刻。"等离子 ALE 用高能离子或中性原子去除表面物质。由于高能离子和中性原子的定向性,等离子体ALE产生构成高纵横比特征所需的各向异性蚀刻,"科罗拉多大学(CU)化学教授Steven George说。

热 ALE 更具挑战性,它使用单向或等向蚀刻的热反应。今天,等离子ALE已经取得进展,而热ALE仍在发展阶段。Steven George表示,"我不认为热ALE投入生产了,但是,许多供应商都在研究热 ALE。”

这两种 ALE 类型都非常适合某些应用。例如,ALE 可用于移除结构中的材料,以形成间隙,其间隙为 10 到 15 个埃,或 5 个原子宽。1埃是 0.1nm 。

在另一个应用程序中,等离子 ALE 可用于处理触点。ALE 还用作抛光技术,用于修复EUV图形化工艺引起的线边粗糙度问题。

因其速度太慢,在许多应用中都不需要用ALE 。传统的 RIE 可以做这项工作。一种技术取代另一种,取决于应用、成本和性能。

尽管如此,该行业仍在开发等离子 ALE。ALE 的一个指标是 Lam 所说的"协同效应"。该术语描述 ALE 的生成量减去不需要的反应。目标是在 ALE 流程中实现 100% 的协同效应。

在硅基工艺中,等离子ALE是有用的。然而,有时硅基的 ALE 工艺容易出现不必要的反应。据专家称,协同效应有时在80%到90%之间。

事实证明,等离子 ALE 在 Lam 所说的"超级 ALE"材料中获得了更高的协同效应,这种材料通常耐热和耐磨。钻石、无定形碳和各种耐火金属被认为是"超级 ALE"材料。GaN也很有前途。

"这些材料有什么共同点?它们都有高表面结合能量,"Lam 高级技术总监 Keren Kanarik 在 ALD/ALE 会议上的一次演示中说。"去除硬度高且难以蚀刻的材料。这就是你想要的 ALE 。这些强度使得材料能够抵抗不良反应。“

这反过来又为可与 ALE 一起使用的新材料打开了大门。例如,ALE 可以帮助抛光"超级 ALE"材料的表面。在另一项应用中,Leti 和 Lam 最近提出了一篇有关在 GaN 中将等离子 ALE 用于栅极蚀刻应用的论文。选择栅极图案的策略是凹槽栅,即深凹槽(超过 100nm)进入堆栈,以生成正向关闭的晶体管。ALE 工艺非常有前途,因为它们能蚀刻GaN,却几乎不会引起衰退,但是速度非常慢。因此,由于蚀刻持续时间长,具有全 ALE 工艺的蚀刻还不适合工业化环境,"Leti的研究员 Simon Ruel 说。"开发的解决方案是启动具有经典、快速等离子工艺的栅极蚀刻,并完成几个 ALE 循环。这种组合提供了更快的蚀刻速率和减少衰退。”

更多的ALE

热ALE也是一个活跃的研究领域。与正在进展中的等离子 ALE 不同,热 ALE 才刚刚起步。CU的乔治说,"还有许多材料需要通过热 ALE 进行演示。了解热 ALE 各种途径的机制仍在开发中。”

业界刚刚开始了解这些机制。"金属氧化物的主要热 ALE 机制是基于氟化和配体交换反应,"George 在最近的一篇论文中说。"氟化是表面修饰反应。氟化对热化学有利,因为大多数金属氟化物比相应的金属氧化物更稳定。氟化的一个困难是,一些金属氟化物易挥发,需要不同的热 ALE 机制。“

尽管如此,研究人员正在探索热 ALE 的几种应用。它们包括:

全栅极晶体管。

用于下一代设备互连的钴、铜和钛。

钴、铁和镍,用于 STT-MRAM 等磁性设备。

使用 ALD 和 ALE 的组合,热 ALE 对于"沉积和反复蚀刻"策略也很重要。ALD 将用于沉积连续薄膜,而热 ALE 将用于蚀刻所需的厚度。"沉积和蚀刻"策略对于由于成核困难而不能直接使用 ALD 形成的超薄薄膜非常重要,"George 说。

如今,一些(但并非全部)应用使用传统的 RIE,这是经过验证的且经济高效的。热 ALE 将需要一些新的突破来破解这些市场。

但是,如果行业能够推进热 ALE,该技术具有一定的优势。热 ALE 不易损坏。随着器件3D化,需要同向性蚀刻。使用摩天大楼类比,RIE可以蚀刻垂直电梯轴阿,而不是水平走廊。

有鉴于此,该行业将同向性ALE定位为 3nm 和/或 2nm 的下一代纳米板 FET 晶体管。纳米片FET是一边用栅包裹着的鳍。

在简单的工艺流程中,纳米表FET从基板上形成超晶格结构开始。这种结构由基板上的硅-锗(SiGe)和硅交替层组成。

然后,在超晶格结构中形成垂直散热,然后形成内部。在此步骤中,使用等向蚀刻技术凹陷超晶格结构中的 SiGe 层的外部部分。这是一个极其困难的过程。

但是,IBM 和 TEL 最近描述了此应用的蚀刻技术。这涉及水平等向SiGe干蚀刻技术,纵横比为 150:1。

同时,在 ALD/ALE 2020 上,特拉华大学提交了一篇有关金属和合金(即钴、铁和 CoFeB)(钴-铁-铜)使用热 ALE 的论文。之所以对CoFeB感兴趣,是因为它用于形成磁隧道结(MTJ)堆栈的下一代内存技术STT-MRAM。

特拉华大学教授Andrew Teplyakov说:"这些材料的性质是,它们ALE中的化学步骤之一必须严格控制,以实现真正的ALE方法,我们通过将表面氯化和氯化的二酮类表面的反应相结合,已经表明了这一点。但是,为组合合金金属选择工艺条件,必须了解蚀刻机制。

最近,研究人员在这里发现了这些机制背后的基本原因。Teplyakov 说:"对于包括 MTJ 在内的应用,ALE 很有希望,因为它是去除材料的有效而精确的方法,而且工艺中不会增加(并实际降低)表面粗糙度。

在会议上,CU还提交了一份有关热ALE的论文,以用于氧化铝(Ta2O5)化合物和钛氮化物(TaN)。目标是使用 Ta2O5 和TaN的金属栅。Ta2O5 是一种有用的介电材料。

尽管如此,金属的热 ALE 仍具有挑战性。CU的乔治说:"选择性具有挑战,因为需要金属前驱物,在配体交换过程中能够生产出一种稳定且挥发性的材料。但是,对于其他周围材料,不需要类似的配体交换反应。了解哪些金属前驱物通过配体交换反应,可产生所需的稳定挥发性产品,需要对化学的广泛了解。”

结论

ALE 绝对是一项值得期待的技术,它可以帮助实现下一代逻辑和内存芯片,更不用说其他了。基于这些芯片和其他芯片的挑战,芯片制造商需要从中得到帮助。

博主译自:SEMIENGINEERING, https://semiengineering.com/atomic-layer-etch-expands-to-new-markets/

/5

/5

pidaneng 2020-8-27 23:46