在FPGA的系统中,如果数据传输不满足触发器的Tsu(建立时间)和Th(保持时间),或者复位过程中复位信号的释放不满足有效时钟沿的恢复时间(recovery time),就有可能产生亚稳态,此时触发器的输出端Q长时间处于震荡状态,且不等于输入端D,并且这种无用的输出可以沿信号通道上的各个触发器级联式传播下去。

下图为数字电路的高低电平和亚稳态区域:

亚稳态通常发生在跨时钟域信号传输以及异步信号采集上,其根本原因是:时序上不满足触发器的建立与保持时间。

1.跨时钟域信号传输,由于源寄存器时钟和目的寄存器的 时钟相移未知,所以源寄存器数据发出,可能在任何时间到达异步时钟域的目的寄存器,因此无法保证这些数据满足目的寄存器的建立时间Tsu和保持时间Th的要求。

2.异步信号采集上,异步信号可以在任何时间点到达目的寄存器,也无法保证满足目的寄存器的建立时间Tsu和保持时间Th的要求。

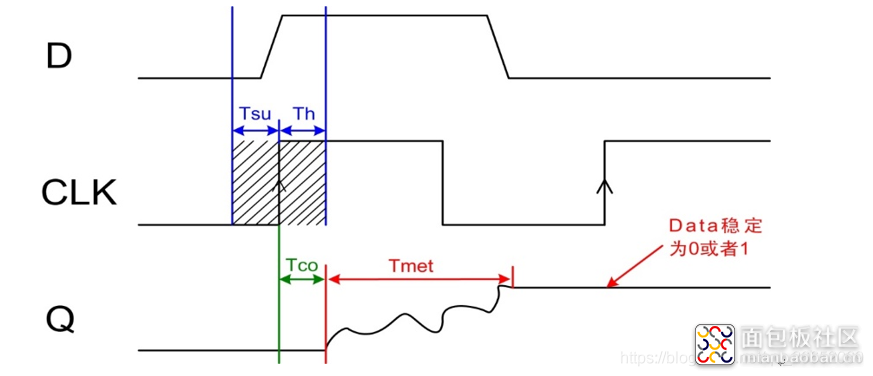

当数据在目的寄存器的Tsu-Th窗口发生变化时,即当数据的Tsu或Th不满足时,就有可能发生亚稳态的现象:

由图可知,当产生亚稳态后,Tco(时钟输出延迟)时间后会有个Tmet(决断时间)的振荡时间段,当振荡结束回到稳定状态时为“0”或“1”,这个是随机的。因此会对后续电路的判断造成影响。

常用对亚稳态消除的三种方式:

1.对异步信号进行同步处理;

2.采用FIFO对跨时钟域数据通信进行缓冲设计;

3.对复位电路采用异步复位、同步释放方式处理;

/1

/1

yzw92 2021-3-17 06:14

火引冰薪 2021-3-16 16:04