一、从电路板设计来说,这里只讨论TYPE-C母座的相关内容,就是焊接在电路板上的TYPE-C插座。电缆上的TYPE-C插头部分,朋友们自行查找TYPE-C标准,自行了解。这是我电路板上用的一种TYPE-C连接器,双排帖片式的,引出了TYPE-C标准的全部24个信号,另外加上4个通孔,增加连接器的牢固性。千万不要选择那种全帖片的连接器,这种连接器做成产品后,用一段时间后就开焊了,体验很差。

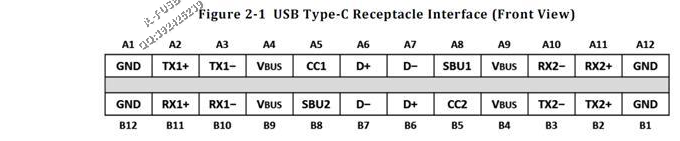

二、TYPE-C连接器的信号说明。

三、原理图设计,CADENCE格式的。

1、设计上,USB2的两组信号并联在一起;USB3的TX、RX两组信号分别并联在一起。三组差分信号再连接到USB3芯片CYUSB3014上。

2、4个数字地信号A1、A12、B1、B12并联在一起,直接和电路板的数字地连续。

3、4个金属外壳地SH1、SH2、SH3、SH4并联在一起,再通过电阻电容并联后接到数据地上。

4、4个电源A4、A9、B4、B9并联在一起,经过磁珠为电路板供电。

四、PCB设计。

在电路板中摆放TYPE-C插座J20及ESD芯片U10后,首先处理电源及两个铺地。如下图所示:

1、4个电源A4、A9、B4、B9并联在一起,图中黄色的4个引脚,分别打过孔到第5层,电源层;

2、4个数字地信号A1、A12、B1、B12,图中绿色部分,先铺铜,再打过孔到第二层,地层;

3、4个金属外壳地SH1、SH2、SH3、SH4,图中蓝色部分,铺铜就可以。;

五、处理三对差分信号。设置好差分规则后,按下图分别打差分对过孔,图中高亮显示的粉色,蓝色,棕色。过孔下到第三、四层内层布线后处理。同时ESD芯片也可以直接和SS信号相连。

六、在内层处理三对差分信号,如下图所示:

良子USB,20200206

专注USB3.0、FPGA、PCIE、定制UVC摄像头

QQ:392425239

作者: 良子usb, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3903348.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/5

/5

Evan0168 2020-3-26 17:33

curton 2020-2-26 19:31