Q: 晶体振荡电路是什么?

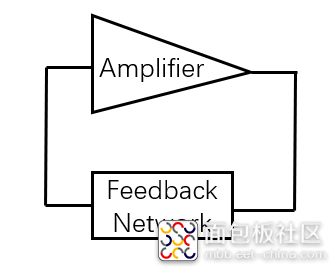

A: 振荡电路是能够产生大小和方向随着周期发生变化的振荡电流。这种振荡电流电路称为振荡电路。振荡电路是由放大器和反馈网络组成。放大电路可以补充能量损耗。正反馈网络可以使电路产生正弦波信号。

Q: 晶振电路设计中需要考虑哪些因素?

A: 在设计振荡器电路时,需要注意以下6点:谐振电路,负载电容,激励电平,频率和振荡模式,走线设计,负阻抗。

------------------------------------------------------------------------------------------------------------------------

1. 谐振电路 (串联/并联)

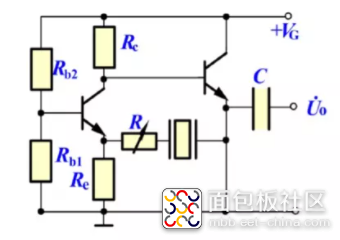

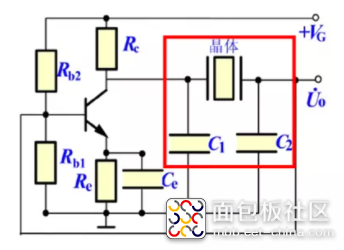

晶体本身无法产生振荡信号,需要借助外部振荡电路实现振荡。振荡电路分为串联和并联。

2. 负载电容

负载电容是选购KOAN晶体必选的参数之一。晶体的频率会根据串联的电容电抗而改变。在串联谐振型电路中,不需要负载电容。

3. 激励电平

激励电平是晶体在工作时消耗的电量,通常以毫瓦和微瓦来表示。激励电平过高会导致KOAN晶振不稳定,加快老化等问题出现。

4、 频率以及振荡模式

晶片越薄,振荡频率就越高。由于工艺的限制和晶片破裂的风险,晶片不能无限的薄。为了达到高频,20mhz基频的晶片,经过五次泛音就可达到100mhz。

5. 设计

减少平行走线,走线尽量短,减少杂散电容。

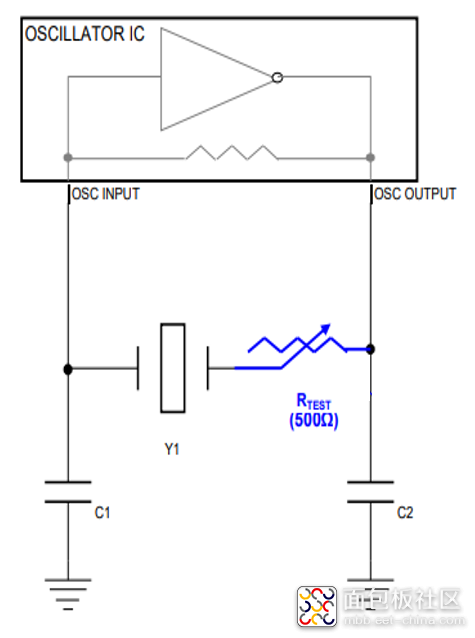

6. 负阻抗

最常用的测试裕量的方法是负阻测试。在晶振支路上串联一个电阻,这个阻值的大小一般为3到5倍的晶振内阻。当加入这个负载电阻后,如果整个KOAN晶振电路还是可以正常起振,我们就基本上可以判定这个晶振拓扑是稳定的。

/4

/4

文章评论(0条评论)

登录后参与讨论