GPIO是通用输入/输出端口的简称,是STM32可控制的引脚。GPIO的引脚与外部硬件设备连接,可实现与外部通讯、控制外部硬件或者采集外部硬件数据的功能。那STM32引脚是如何分类的?GPIO内部结构是怎样的,随海翎光电的小编一起看看吧!

一、GPIO是什么?

GPIO(英语:General-purpose input/output)

通用输入输出端口的简称。可以通过软件控制其输出和输入。stm32芯片的GPIO引脚与外部设备连接起来,GPIO既然一个引脚可以用于输入、输出或其他特殊功能,那么一定有寄存器用来选择这些功能。对于输入,一定可以通过读取某个寄存器来确定引脚电位的高低;对于输出,一定可以通过写入某个寄存器来让这个引脚输出高电位或者低电位;对于其他特殊功能,则有另外的寄存器来控制它们。

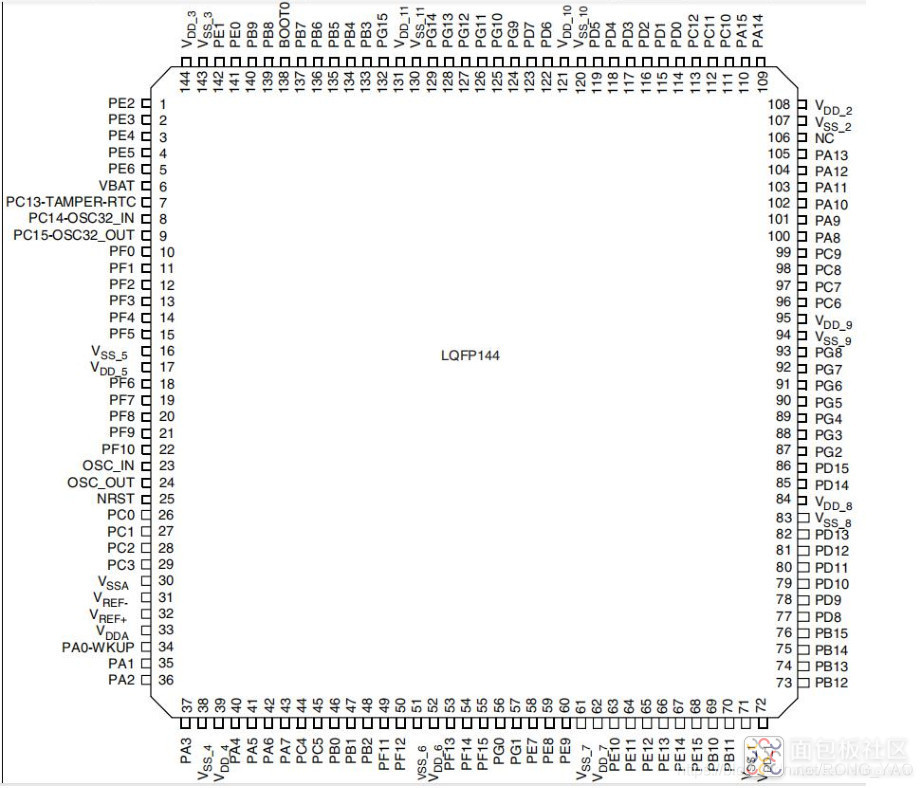

二、STM32引脚分类

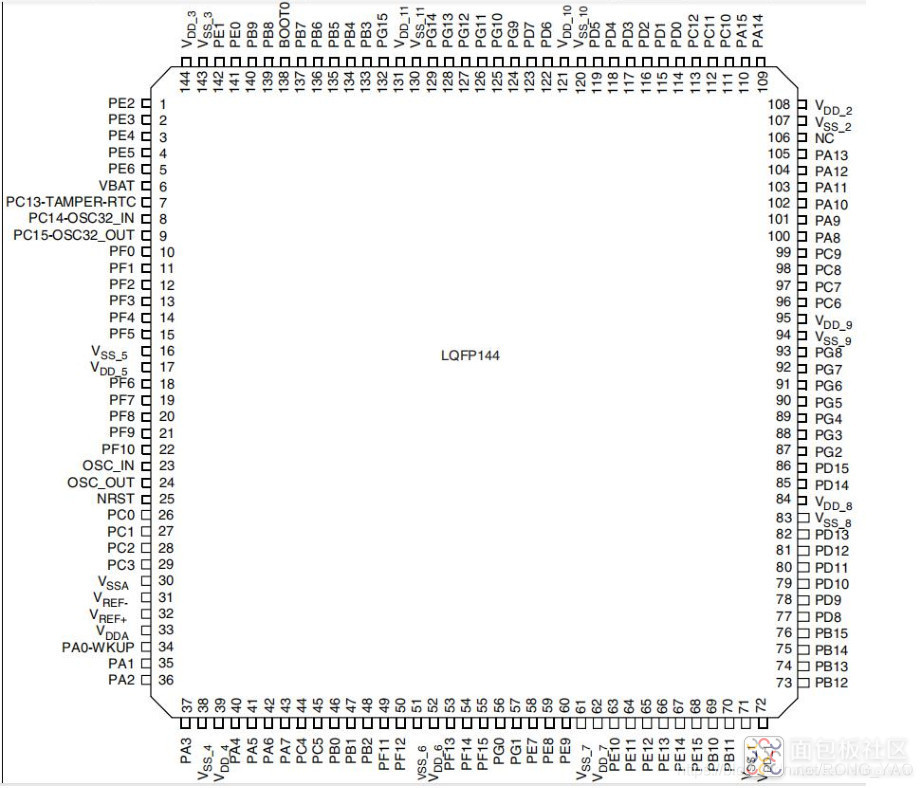

1.电源管脚:引脚图中的 VDD、VSS、VREF+、VREF-、VSSA、VDDA 等都属于电源引脚。

2.晶振管脚:引脚图中的 PC14、PC15 和 OSC_IN、OSC_OUT 都属于晶振引脚,不过它们还可以作为普通引脚使用。

3.复位管脚: 引脚图中的 NRST 属于复位引脚,不做其他功能使用。

4.下载引脚:引脚图中的 PA13、PA14、PA15、PB3 和 PB4 属于 JTAG 或SW 下载引脚。不过它们还可以作为普通引脚或者特殊功能使用,具体的功能可以查看芯片数据手册,里面都会有附加功能说明。当然,STM32 的串口功能引脚也是可以作为下载引脚使用。

5.T BOOT 引脚:引脚图中的 BOOT0 和 PB2(BOOT1)属于 BOOT 引脚,PB2 还可以作为普通管脚使用。在 STM32 启动中会有模式选择,其中就是依靠着 BOOT0和 BOOT1 的电平来决定。

6.GPIO管脚:引脚图中的 PA、PB、PC、PD 等均属于 GPIO 引脚。从引脚图可以看出,GPIO 占用了 STM32 芯片大部分的引脚。并且每一个端口都有 16 个引脚,比如 PA 端口,它有 PA0-PA15。其他的 PB、PC 等端口是一样的。

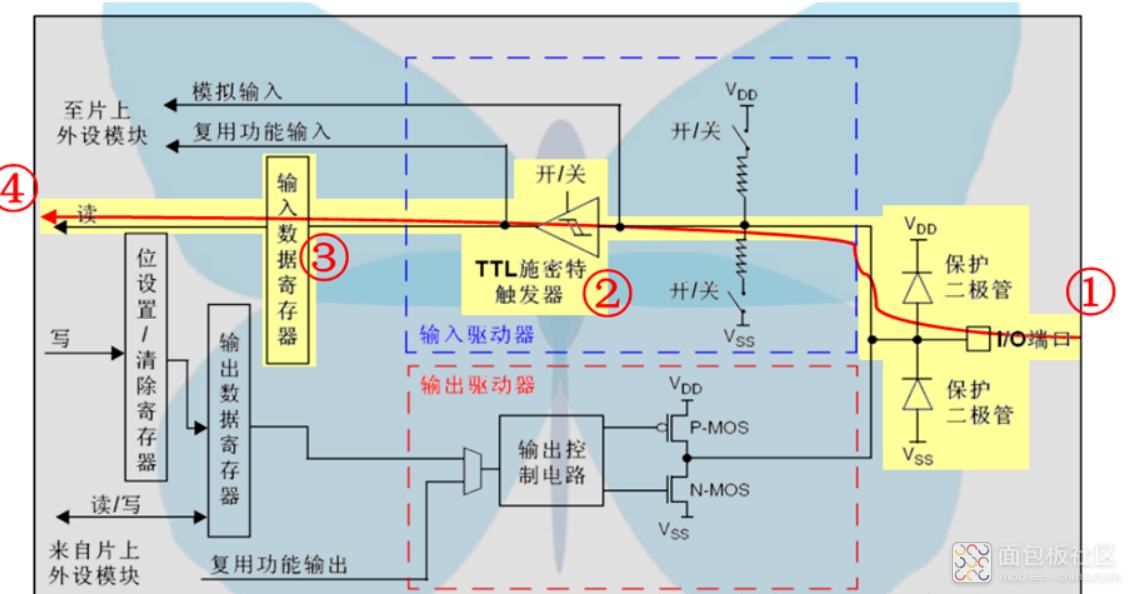

三、GPIO内部结构

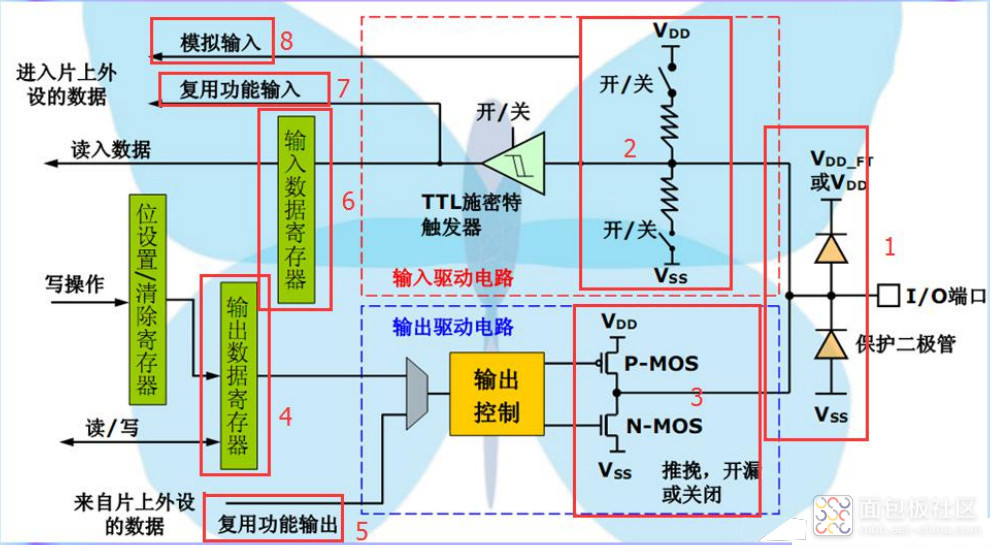

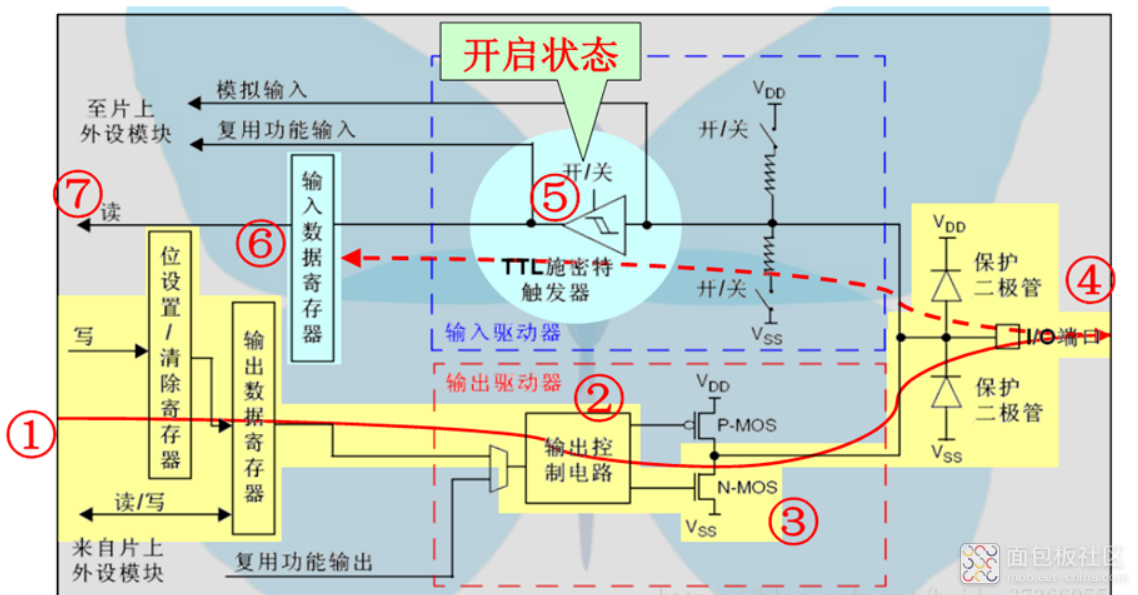

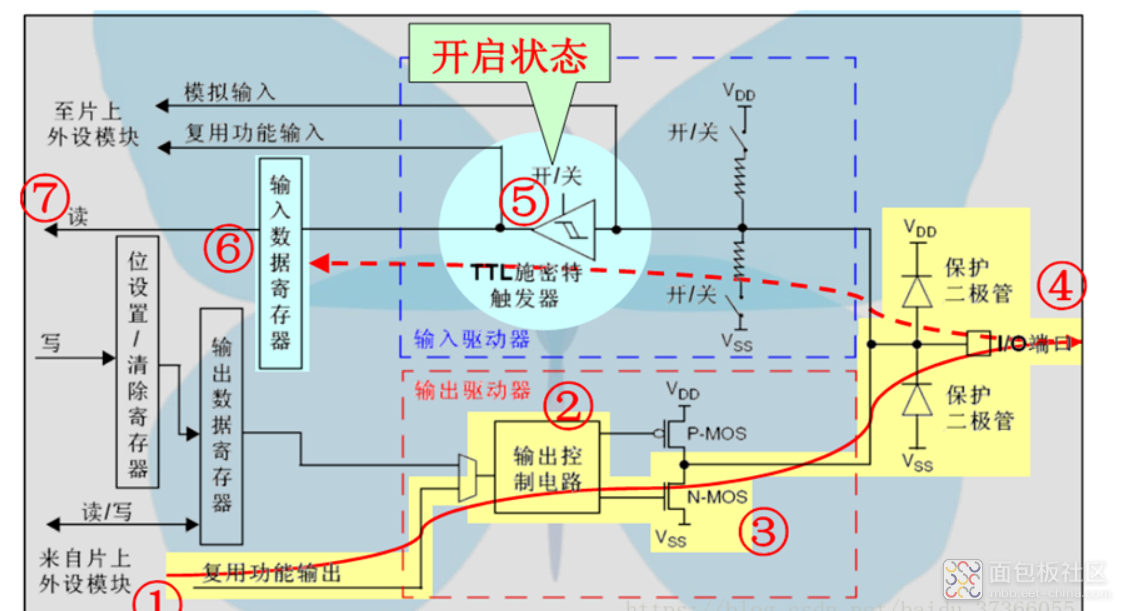

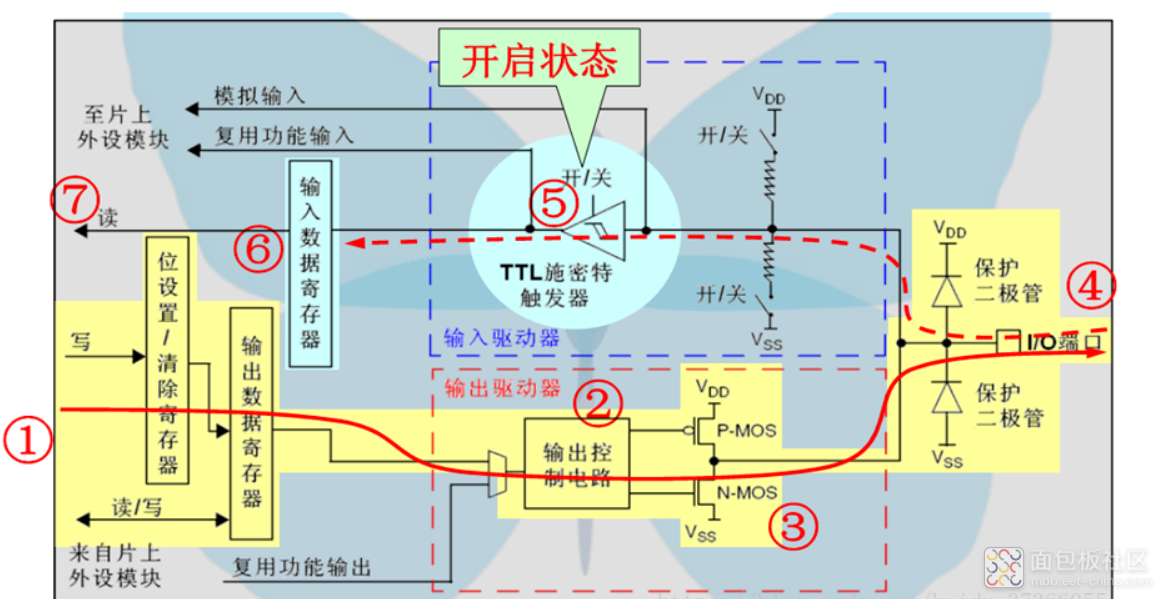

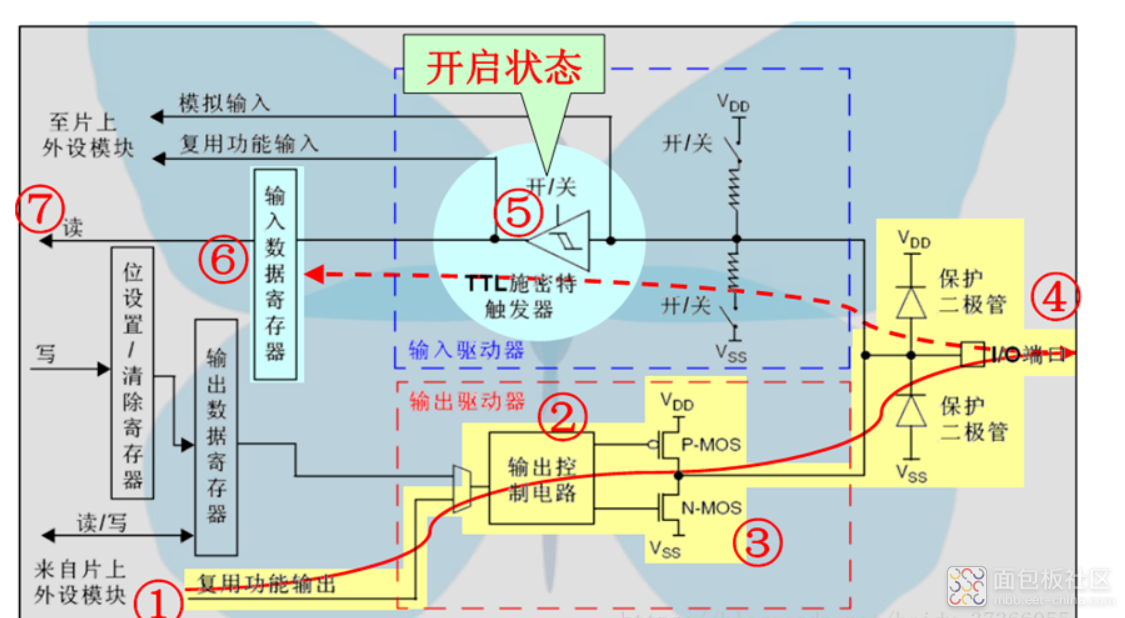

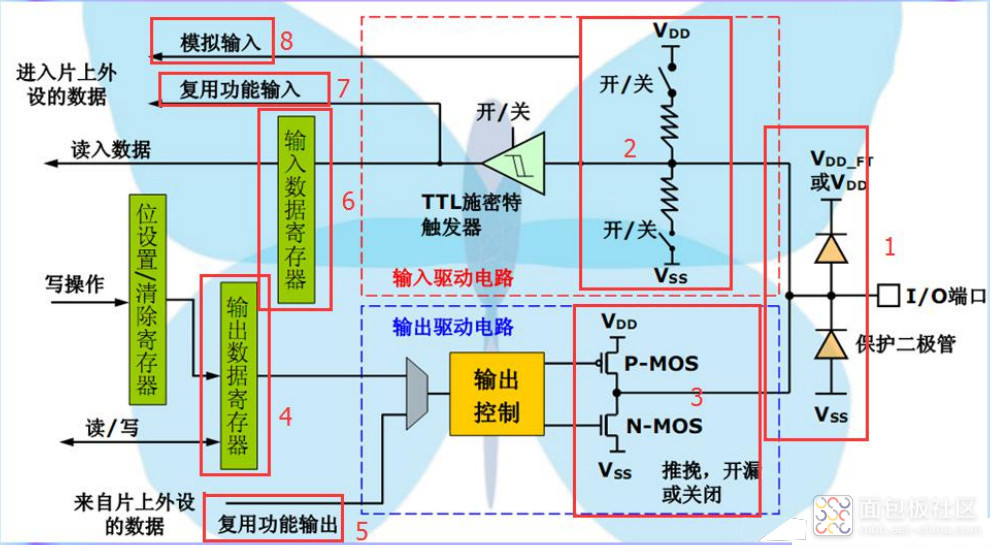

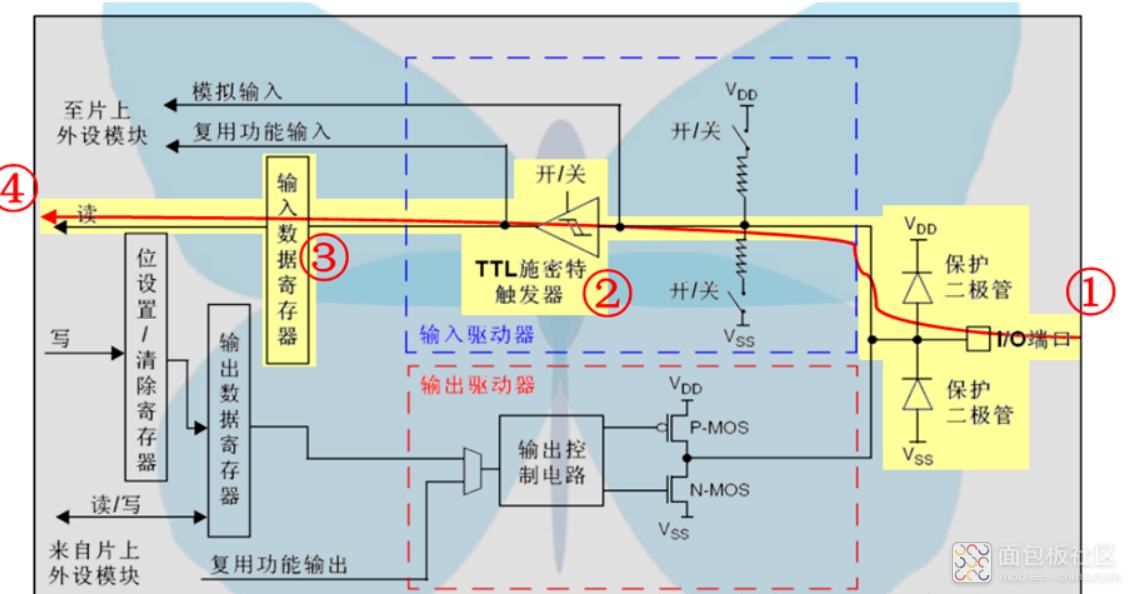

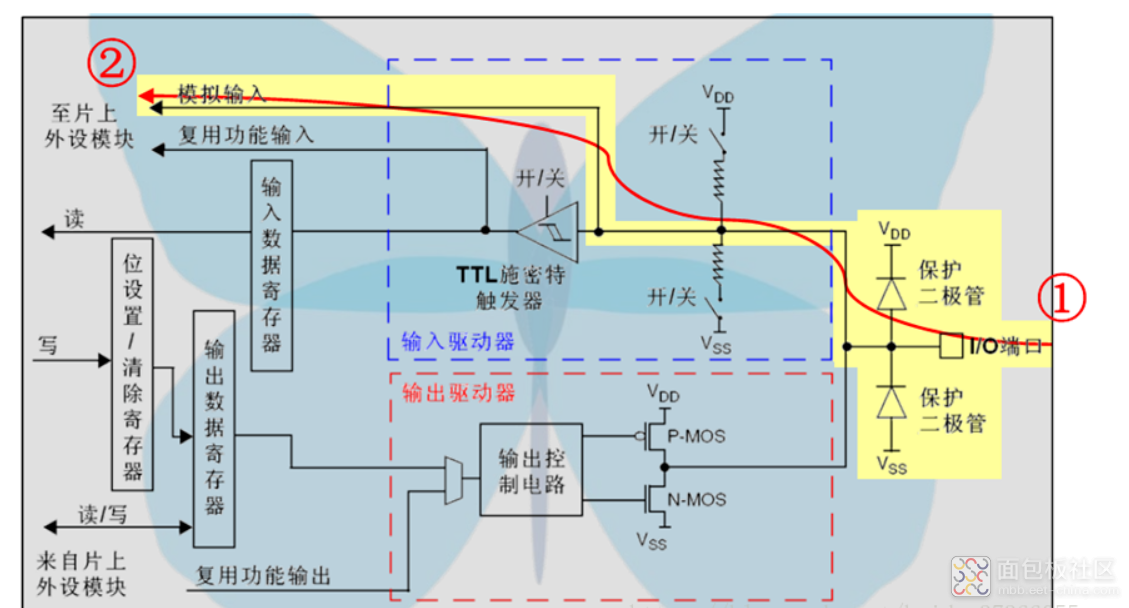

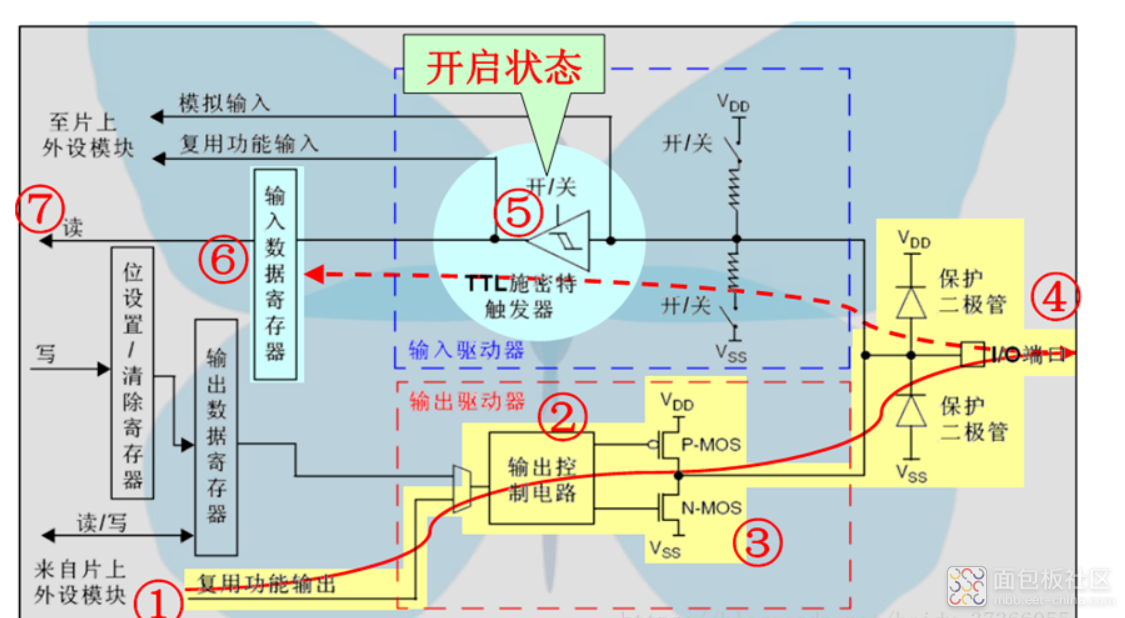

图中最右端 I/O 端口是STM32 芯片的引脚,其它部分都在 STM32 芯片内部。

(1)保护二极管- 引脚内部加上这两个保护二级管可以防止引脚外部过高或过低的电压输入。

- 当引脚电压高于 VDD_FT 或 VDD 时,上方的二极管导通吸收这个高电压。

- 当引脚电压低于 VSS 时,下方的二极管导通,防止不正常电压引入芯片导致芯片烧毁。

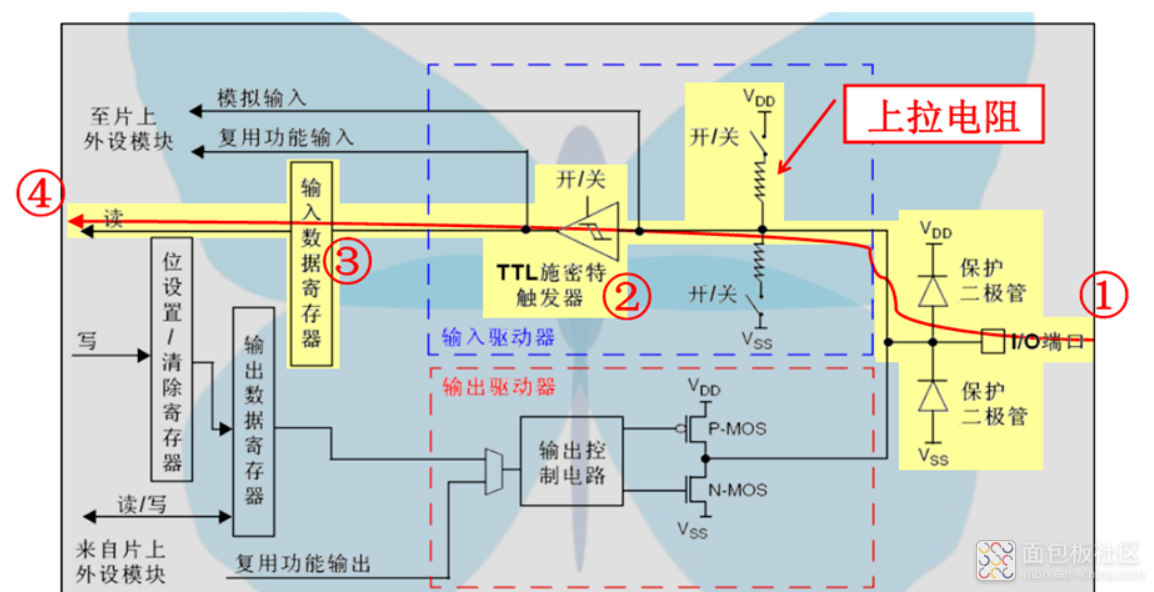

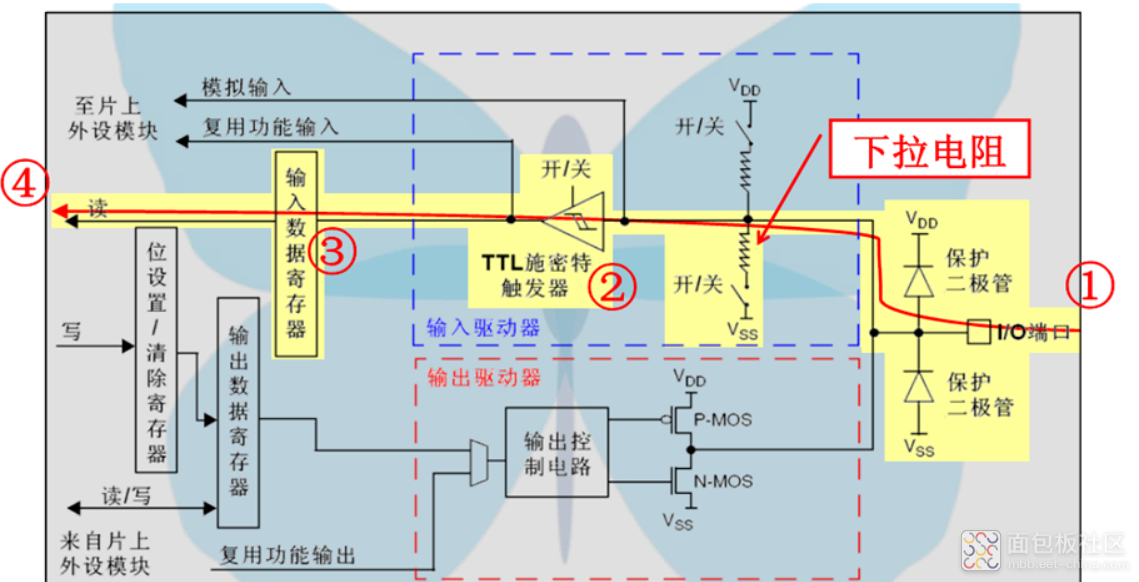

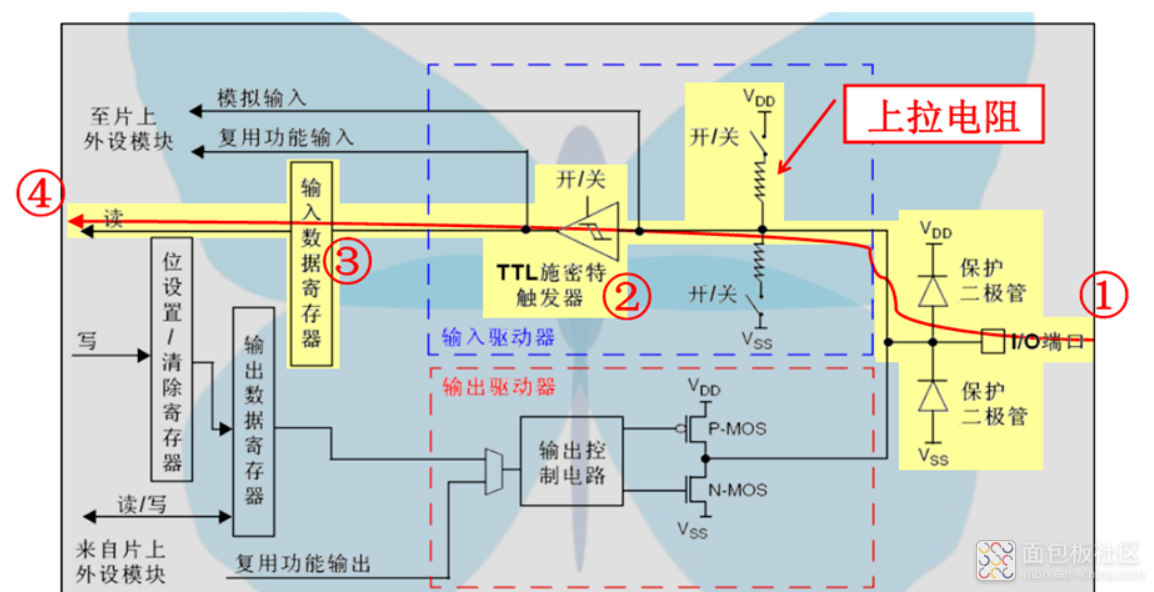

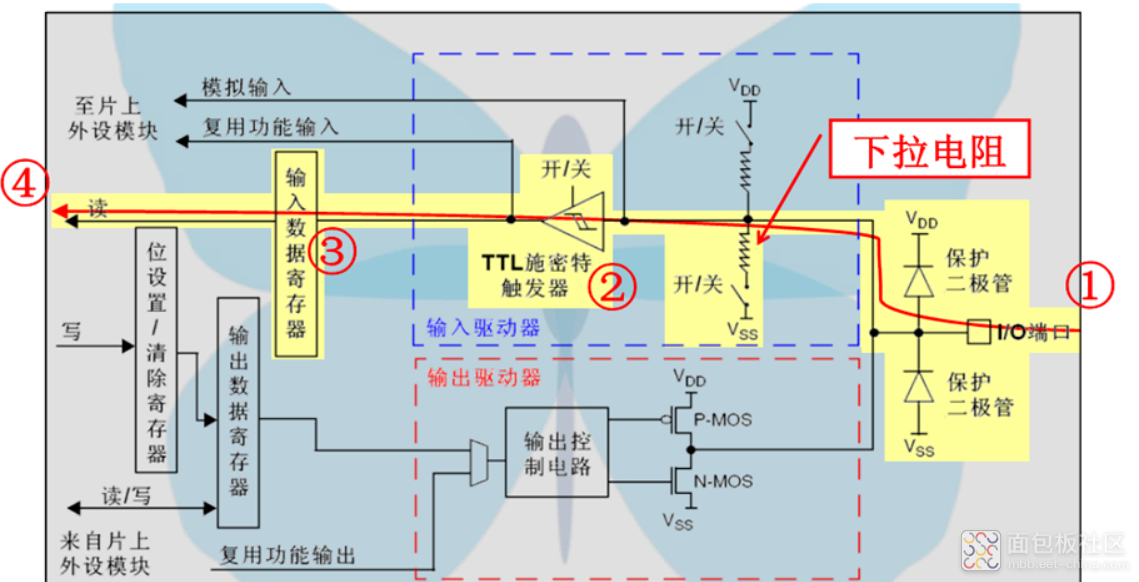

(2)上下拉电阻- 上拉和下拉电阻上都有一个开关,通过配置上下拉电阻开关,可以控制引脚的默认状态电平。

- 当开启上拉时引脚默认电压为高电平,

- 开启下拉时,引脚默认电压为低电平,这样就可以消除引脚不定状态的影响。

- 将上拉和下拉的开关都关断,这种状态我们称为浮空模式,一旦配置成这个模式,引脚的电压是不确定的,如果用万用表测量此模式下管脚电压时会发现只有 1 点几伏,而且还不时改变,所以一般情况下我们都会给引脚设置成上拉或者下拉模式,使它有一个默认状态。

- STM32 上下拉及浮空模式的配置是通过GPIOx_CRL 和 GPIOx_CRH 寄存器控制的。

- STM32 内部的上拉其实是一个弱上拉,也就是说通过此上拉电阻输出的电流很小,如果想要输出一个大电流,那么就需要外接上拉电阻了。

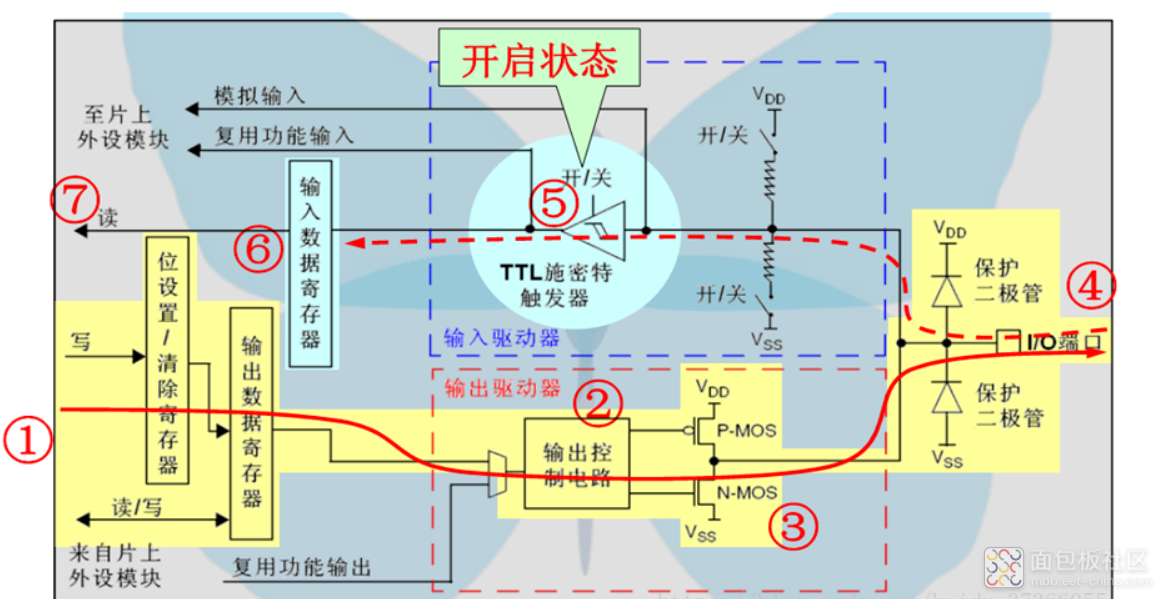

(3)、P-MOS 和 和 S N-MOS - GPIO 引脚经过两个保护二极管后就分成两路,

- 上面一路是“输入模式”,下面一路是“输出模式”。

- 输出模式,线路经过一个由 P-MOS 和 N-MOS管组成的单元电路,这让 GPIO 引脚具有了推挽和开漏两种输出模式。

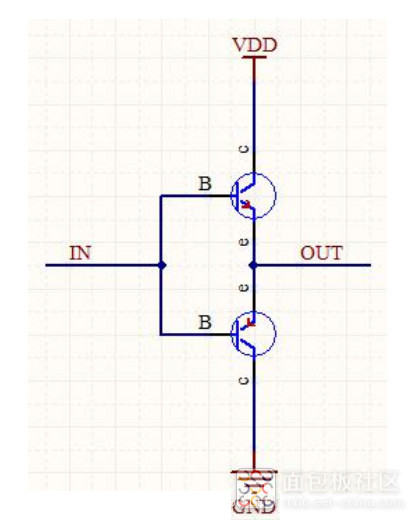

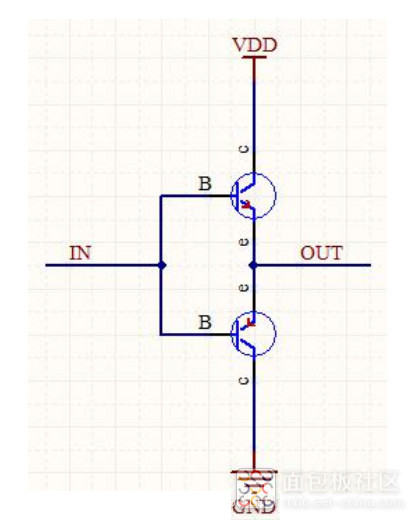

- 推挽输出模式,是根据 P-MOS 和 N-MOS 管的工作方式命名的。

- 在该结构单元输入一个高电平时,P-MOS 管导通,N-MOS 管截止,对外输出高电平(3.3V)。

- 在该单元输入一个低电平时,P-MOS 管截止,N-MOS 管导通,对外输出低电平(0V)。

- 如果当切换输入高低电平时,两个 MOS 管将轮流导通,一个负责灌电流(电流输出到负载),一个负责拉电流(负载电流流向芯片),使其负载能力和开关速度都比普通的方式有很大的提高。下图为推挽输出模式的等效电路。

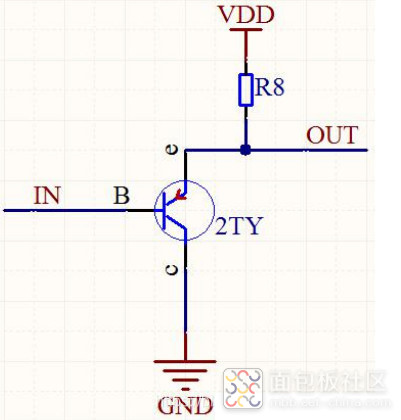

- 在开漏输出模式时,不论输入是高电平还是低电平,P-MOS 管总处于关闭状态。

- 当给这个单元电路输入低电平时,N-MOS 管导通,输出即为低电平。

- 当输入高电平时,N-MOS 管截止,这个时候引脚状态既不是高电平,又不是低电平,我们称之为高阻态。

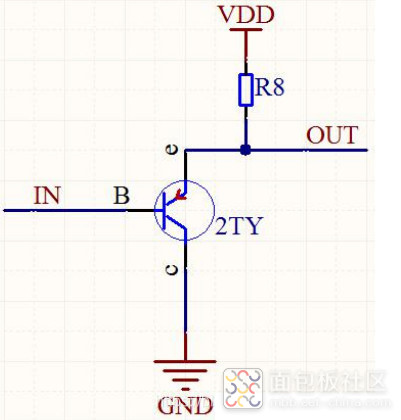

- 如果想让引脚输出高电平,那么引脚必须外接一个上拉电阻,由上拉电阻提供高电平。开漏输出模式等效电路图如下图所示。

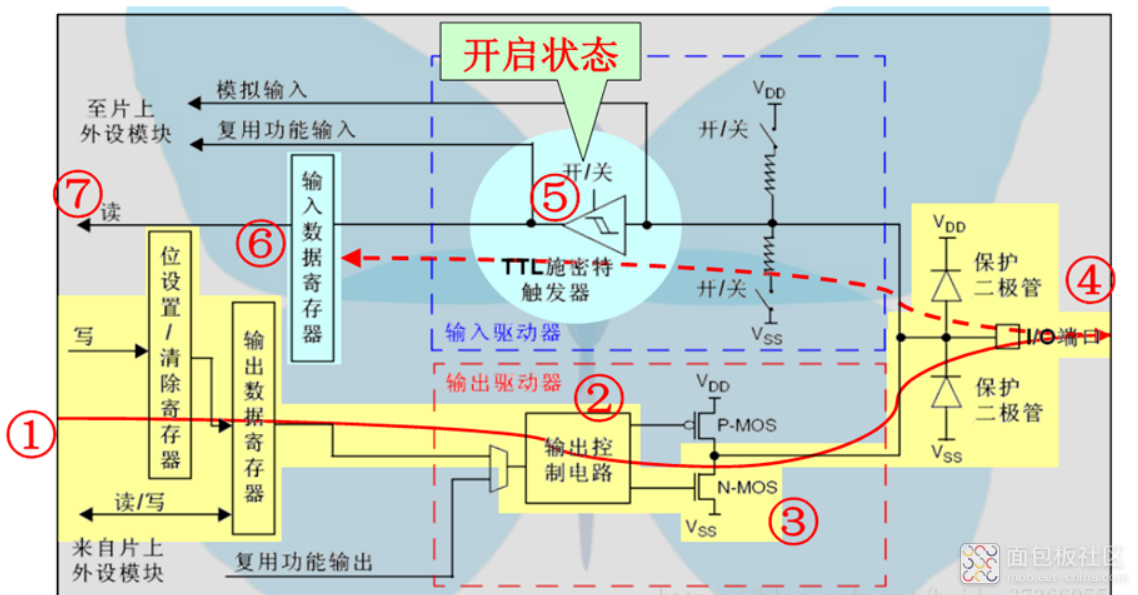

(4)、输出数据寄存器双 MOS 管结构电路的输入信号,是由 GPIO“

输出数据寄存器GPIOx_ODR”提供的,因此我们通过修改输出数据寄存器的值就可以修改 GPIO 引脚的输出电平。而“置位/复位寄存器 GPIOx_BSRR”可以通过修改输出数据寄存器的值从而影响电路的输出。

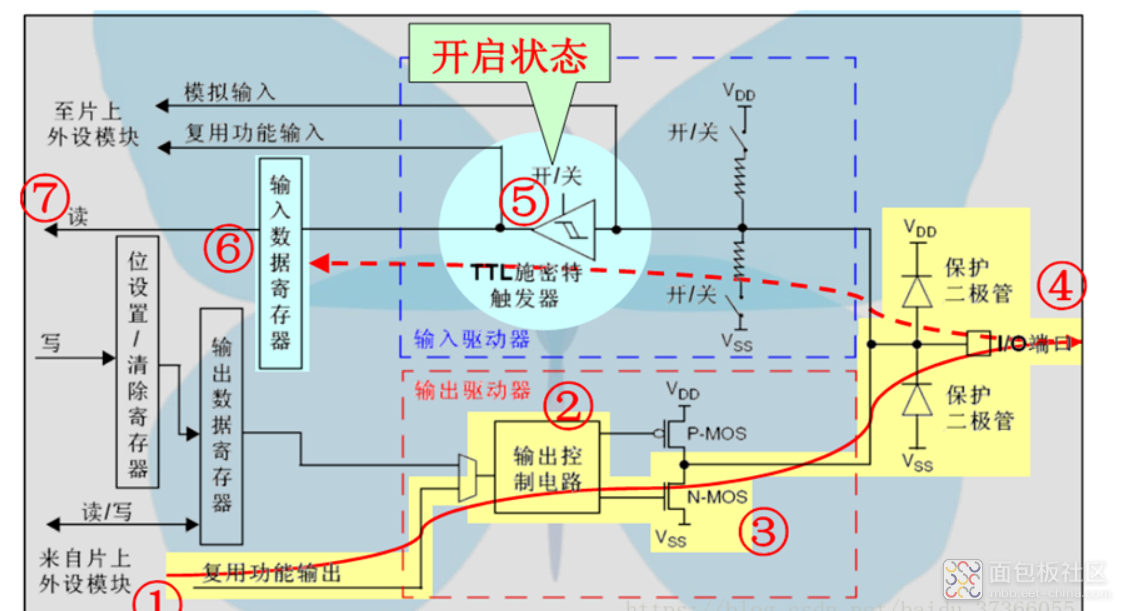

(5)、复用功能输出由于

STM32 的 GPIO 引脚具有第二功能,因此当使用复用功能的时候,也就是通过其他外设复用功能输出信号与 GPIO 数据寄存器一起连接到双 MOS 管电路的输入,其中梯形结构是用来选择使用复用功能还是普通 IO 口功能。例如我们使用 USART 串口通讯时,需要用到某个 GPIO 引脚作为通讯发送引脚,这个时候就可以把该 GPIO 引脚配置成 USART 串口复用功能,由串口外设控制该引脚,发送数据。

(6)、输入数据寄存器输入数据寄存器是由 IO 口经过上下拉电阻、施密特触发器引入。当信号经过触发器,模拟信号将变为数字信号 0 或 1,然后存储在输入数据寄存器中,通过读取输入数据寄存器 GPIOx_IDR 就可以知道 IO 口的电平状态。

(7)、复用功能输入此模式与复用功能输出类似。在复用功能输入模式时,GPIO 引脚的信号传输到 STM32 其他片上外设,由该外设读取引脚的状态。同样,如我们使用 USART 串口通讯时,需要用到某个 GPIO 引脚作为通讯接收引脚,这个时候就可以把该 GPIO 引脚配置成 USART 串口复用功能,使 USART 可以通过该通讯引脚的接收远端数据。

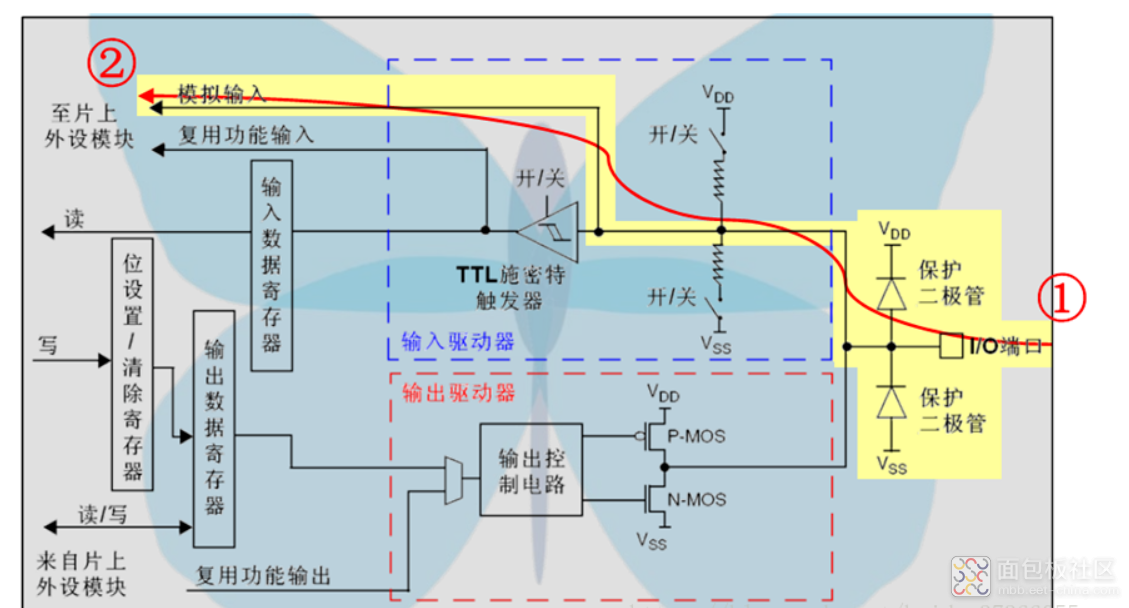

(8)、模拟输入输出当 GPIO 引脚用于

ADC 采集电压的输入通道时,用作“模拟输入”功能,此时信号是不经过施密特触发器的,

因为经过施密特触发器后信号只有 0、1 两种状态,ADC 外设要采集到原始的模拟信号,信号源输入必须在

施密特触发器之前。类似地,当 GPIO 引脚用于 DAC 作为模拟电压输出通道时,此时作为“模拟输出”功能, DAC 的模拟信号输出就不经过双 MOS 管结构了,模拟信号直接通过管脚输出。

四、GPIO具有8种模式,四种输入模式,四种输出模式。

输入模式:

输入浮空 GPIO_Mode_IN_FLOATING输入上拉 GPIO_Mode_IPU输入下拉 GPIO_Mode_IPD模拟输入 GPIO_Mode_AIN

输出模式:

开漏输出(上拉或者下拉)GPIO_Mode_Out_OD

开漏复用功能(上拉或者下拉)GPIO_Mode_AF_OD

推挽式输出(上拉或者下拉)GPIO_Mode_Out_PP

推挽式复用功能(上拉或者下拉)GPIO_Mode_AF_PP

四种最大输出速度:

2MHZ

25MHZ

50MHZ

1000MHZ

五、GPIO8种模式含义

输入浮空:浮空就是逻辑器件与引脚即不接高电平,也不接低电平。由于逻辑器件的内部结构,当它输入引脚悬空时,相当于该引脚接了高电平。一般实际运用时,引脚不建议悬空,易受干扰。通俗讲就是浮空就是浮在空中,就相当于此端口在默认情况下什么都不接,呈高阻态,这种设置在数据传输时用的比较多。浮空最大的特点就是电压的不确定性,它可能是0V,页可能是VCC,还可能是介于两者之间的某个值(最有可能) 浮空一般用来做ADC输入用,这样可以减少上下拉电阻对结果的影响。

输入上拉模式:上拉就是把点位拉高,比如拉到Vcc。上拉就是将不确定的信号通过一个电阻嵌位在高电平。电阻同时起到限流的作用。弱强只是上拉电阻的阻值不同,没有什么严格区分。

输入下拉:就是把电压拉低,拉到GND。与上拉原理相似。

模拟输入:模拟输入是指传统方式的输入,数字输入是输入PCM数字信号,即0,1的二进制数字信号,通过数模转换,转换成模拟信号,经前级放大进入功率放大器,功率放大器还是模拟的。

开漏输出:输出端相当于三极管的集电极,要得到高电平状态需要上拉电阻才行,适合于做电流型的驱动,其吸收电流的能力相对强(一般20mA以内)。

开漏形式的电路有以下几个特点:1. 利用外部电路的驱动能力,减少IC内部的驱动。当IC内部MOSFET导通时,驱动电流是从外部的VCC流经R pull-up ,MOSFET到GND。IC内部仅需很下的栅极驱动电流。2. 一般来说,开漏是用来连接不同电平的器件,匹配电平用的,因为开漏引脚不连接外部的上拉电阻时,只能输出低电平,如果需要同时具备输出高电平的功能,则需要接上拉电阻,很好的一个优点是通过改变上拉电源的电压,便可以改变传输电平。比如加上上拉电阻就可以提供TTL/CMOS电平输出等。(上拉电阻的阻 决定了逻辑电平转换的沿的速度 。阻 越大,速度越低功耗越小,所以负载电阻的选择要兼顾功耗和速度。)3. OPEN-DRAIN提供了灵活的输出方式,但是也有其弱点,就是带来上升沿的延时。因为上升沿是通过外接上拉无源电阻对负载充电,所以当电阻选择小时延时就小,但功耗大;反之延时大功耗小。所以如果对延时有要求,则建议用下降沿输出。4. 可以将多个开漏输出的Pin,连接到一条线上。通过一只上拉电阻,在不增加任何器件的情况下,形成“与逻辑”关系。这也是I2C,SMBus等总线判断总线占用状态的原理。 在一个结点(线)上, 连接一个上拉电阻到电源 VCC 或 VDD 和 n 个 NPN 或 NMOS 晶体管的集电极 C 或漏极 D, 这些晶体管的发射极 E 或源极 S 都接到地线上, 只要有一个晶体管饱和, 这个结点(线)就被拉到地线电平上. 因为这些晶体管的基极注入电流(NPN)或栅极加上高电平(NMOS),晶体管就会饱和, 所以这些基极或栅极对这个结点(线)的关系是或非 NOR 逻辑. 如果这个结点后面加一个反相器, 就是或 OR 逻辑.

其实可以简单的理解为:在所有引脚连在一起时,外接一上拉电阻,如果有一个引脚输出为逻辑0,相当于接地,与之并联的回路“相当于被一根导线短路”,所以外电路逻辑电平便为0,只有都为高电平时,与的结果才为逻辑1。

开漏复用功能:可以理解为GPIO口被用作第二功能时的配置情况(即并非作为通用IO口使用)。端口必须配置成复用功能输出模式(推挽或开漏)

推挽式输出:可以输出高,低电平,连接数字器件;推挽结构一般是指两个三级管分别受到互补信号的控制,总是在一个三极管导通的时候另一个截止。高低电平由IC的电源低定。

推挽电路是两个参数相同的三极管或MOSFET,以推挽方式存在于电路中,各负责正负半周的波形方法任务,电路工作时,两只对称的功率开关管每次只有一个导通,所以导通损耗小,效率高。输出即可以向负载灌电流。推拉式输出级即提高电路的负载能力,又提高开关速度。

推挽式复用功能:可以理解为GPIO口被用作第二功能时的配置情况(并非作为通用IO口使用)

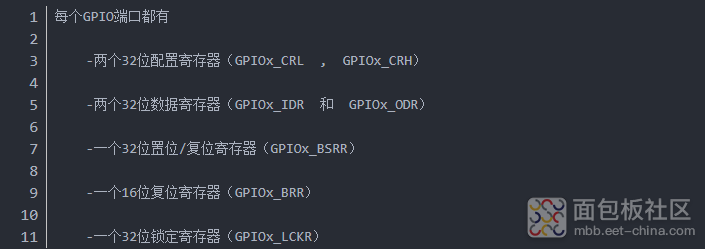

GPIO的主要寄存器

每个I/O端口位可以自由编程,然而I/O端口寄存器必须按32位字被访问(不允许半字或字节访问),**一些寄存器的使用功能可以通过立创商场查找相应单片机芯片的数据手册来查阅,然后进行相应的端口配置,以达到IO口初始化的效果。**也可以通过以下链接来查看GPIO相关寄存器配置详情。

GPIO相关寄存器

六、在stm32中选用io模式

(1) 浮空输入_IN_FLOATING ——浮空输入,可以做KEY识别,RX1

(2)带上拉输入_IPU——IO内部上拉电阻输入

(3)带下拉输入_IPD—— IO内部下拉电阻输入

(4)模拟输入_AIN ——应用ADC模拟输入,或者低功耗下省电

(5)开漏输出_OUT_OD ——IO输出0接GND,IO输出1,悬空,需要外接上拉电阻,才能实现输出高电平。当输出为1时,IO口的状态由上拉电阻拉高电平,但由于是开漏输出模式,这样IO口也就可以由外部电路改变为低电平或不变 。可以读IO输入电平变化,实现C51的IO双向功能

(6)推挽输出_OUT_PP ——IO输出0-接GND, IO输出1 -接VCC,读输入值是未知的

(7)复用功能的推挽输出_AF_PP ——片内外设功能(I2C的SCL,SDA)

(8)复用功能的开漏输出_AF_OD ——片内外设功能(TX1,MOSI,MISO.SCK.SS)

总结:之前对于配置寄存器都是通过例程来进行配置的,当自己实际来进行配置的时候还是有点困难,经过多次练习后,自己掌握了一些寄存器的应用场景之后,配置端口的速度也有所提升,也对之前不懂的地方有了新的理解,总的来说,成功没有捷径,还是要多练习,多看stm32中的一些底层函数,这样才有更好的提升。好了,海翎光电的小编今日分享就到这里。

/2

/2

文章评论(0条评论)

登录后参与讨论