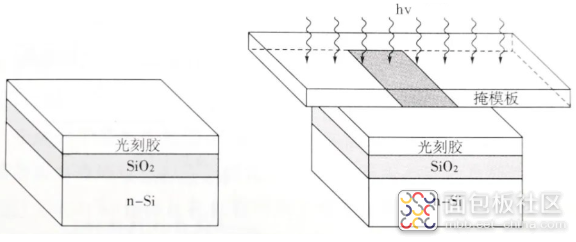

光刻就是将掩膜上的几何图形转移到涂在半导体晶圆表面的光敏薄层材料(光刻胶)上的工艺过程。为了产生电路图形,还需要再一次把光刻胶上的图形转移到光刻胶下面的组成集成电路器件的各层上去(刻蚀)。

1.光学光刻-掩膜、光刻胶

1.1 洁净室

由于空气中的尘埃粒子会落到半导体晶圆和光刻掩模上,致使器件中产生缺陷,导致集成电路失效,因此洁净室是必需的。制造集成电路的大多数工艺区域要求100级(空气中每立方米内直径大于等于0.5μm的尘埃粒子总数不超过约3500)洁净室,在光刻区域,洁净室要求10级或更高。

1.2 光刻胶

光刻这个步骤中,首先是涂光刻胶:

涂光刻胶的过程:

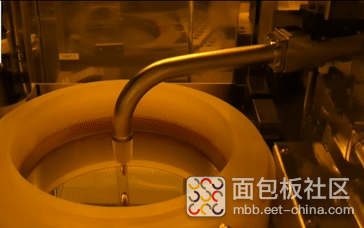

将光刻胶涂在晶圆上,并让晶圆高速旋转,使光刻胶均匀分布

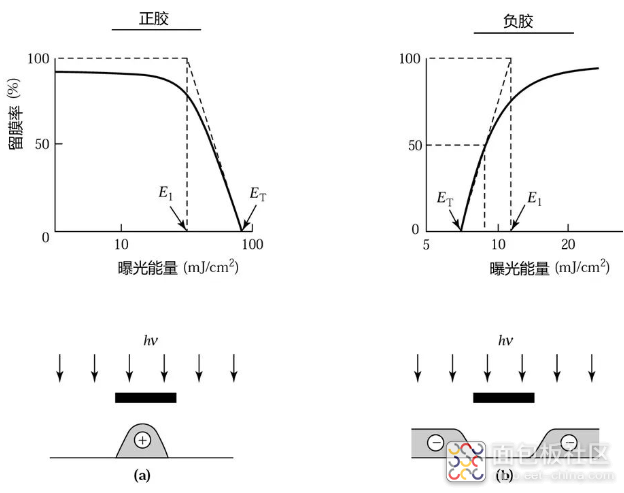

光刻胶是一种对辐射敏感的化合物,分为正胶和负胶。正胶的曝光部分在显影时更易溶于溶剂而被去掉,所得的图图像与掩模上的相同。负胶的曝光部分在显影时更不易被溶解,因此所得图形与掩模上的相反。

图(a)给出了典型的曝光反应曲线与正胶图像的截面图。光刻胶即使没有曝光,在显影液中也有一定的可溶性。随着曝光能量的增加,可溶性逐渐增加,达到阈值能量Er后,光刻胶完全可溶。图(b)负胶同理。

由于存在衍射,光刻胶图像边缘一般不在掩膜图像边缘的垂直投影位置上,而是在吸收的光能总量等于阈值能量Er的位置上。

1.3 掩膜

集成电路制造所用的掩膜通常是缩小倍数的掩膜。制作掩膜是用电子束曝光系统将图形直接转移到对电子束敏感的掩膜上。掩模由镀铬玻璃板组成。电路图形首先被转移到对电子敏感的掩模上,再被转移到下面的镀铬层上,最终得到需要的掩模。

一块掩膜上的图形代表了集成电路设计中的一层。综合的布局布线图按照集成电路制造对应的工序分成若干块掩模层,例如隔离区是一层,栅极区是另一层等。一般一个完整的集成电路工艺流程需要15~20层不同的掩膜。

2.光学光刻-曝光(设备、原理)

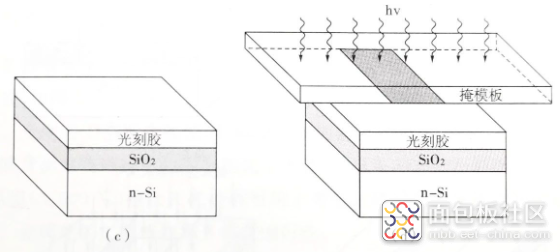

2.1 遮蔽式曝光(接触式曝光、接近式曝光):

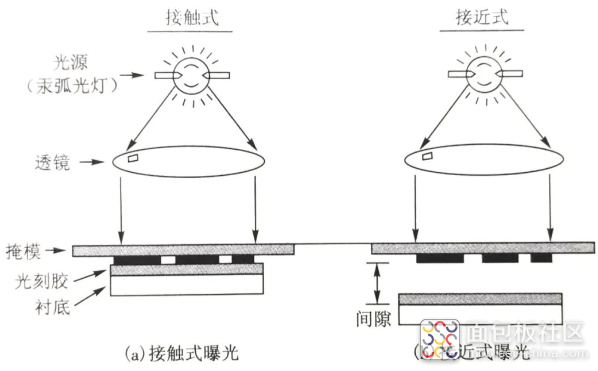

有两种基本的光学曝光方法:遮蔽式(shadow)曝光与投影式(projection)曝光。遮蔽式曝光可分为两种:掩模和晶圆直接接触,称为接触式曝光;掩模和晶圆非常靠近但不接触,称为接近式曝光。

图(a)为接触式曝光。涂了光刻胶的晶圆与掩模直接接触,分辨率可达1μm。但是,当掩模与晶圆接触时,晶圆上的尘埃粒子或硅渣会嵌入掩模,对掩模造成永久性损伤,使随后使用它曝光的每个晶圆上都留下缺陷。

要把掩模的受损程度减至最小,可采用接近式曝光,如图(b)所示:曝光时在掩模与晶圆之间有一个小的间隙(10~50μm)。这个小间隙使掩模图形边缘处形成光学衍射,即在光通过不透明掩模图形边缘时,形成一些干涉条纹,有一些光进入阴影区,使分辨率降到2~5μm范围.

在遮蔽式曝光中,可以达到的最小线宽CD(critical dimension,也称临界尺寸)约为

因此,减小λ(曝光所用的光波波长)与g(掩模与晶圆之间的距离,包括光刻胶的厚度)都是有利的。 当λ=0.4 μm,g=50 μm时,临界尺寸CD为4.5 um。若λ降到0.25μm(波长为0.2~0.3μm的光属于紫外光谱区),g减小到15μm,则CD降为2μm。然而,在距离g给定后,直径大于g的尘埃粒子仍能造成掩模的损伤。

免责声明:文章来源汶颢www.whchip.com 以传播知识、有益学习和研究为宗旨。 转载仅供参考学习及传递有用信息,版权归原作者所有,如侵犯权益,请联系删除。

/2

/2

文章评论(0条评论)

登录后参与讨论