在阅读了《高速PCB设计经验规则应用实践》后,对于PCB设计的布局经验有了更为深入和系统的理解。该书不仅详细阐述了高速PCB设计中的经验法则,还通过实际案例和理论分析,让读者能够更好地掌握这些法则并将其应用于实际工作中。布局是走线的基础,预先的规划再到叠层的选择,电源和地的分配,信号网络的走线等等,对布局方面也是非常的关注。

布局规划的重要性:

在PCB设计中,布局规划是至关重要的一步。它直接影响到后续布线的难易程度、信号完整性以及电磁兼容性等方面。因此,在进行元件布局之前,我们必须对PCB的平面空间做出一个分区布置规划。这一步骤要求我们不仅要了解PCB的尺寸和形状,还要根据电路的功能需求和信号流向,合理划分各个功能区域,如模拟电路区、数字电路区、射频电路区等。通过预先规划,我们可以避免在布线阶段出现过多的交叉和重叠,从而提高布线的效率和质量。

叠层布局的经验:

在高速PCB设计中,叠层布局是影响信号完整性和电磁兼容性的关键因素之一。合理的叠层布局可以有效地减小信号间的串扰和损耗,提高信号的传输质量。在选择叠层结构时,我们需要考虑多种因素,如信号的传输速率、介质材料的介电常数、阻抗控制等。此外,为了减小电磁辐射和干扰,我们通常会在电源平面和地平面之间设置一定的间距,并采用适当的屏蔽措施。

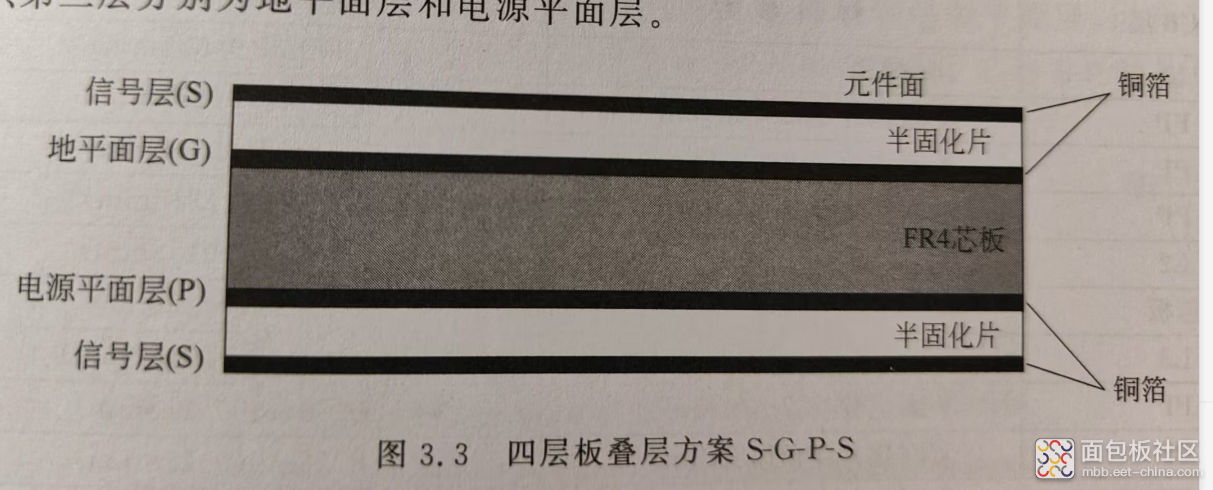

例如四层板的SGPS方案:

这种布线方式实现了信号层与地平面、信号层和电源层的紧密耦合。

电源与地的布局:

电源与地的布局也是高速PCB设计中的重要环节。在布局时,我们需要确保电源和地的分布均匀,避免出现电源或地线的过度集中或稀疏。同时,为了减小电源噪声和地线反弹等问题,我们还可以采用去耦电容、滤波电感等元件来抑制电源波动和干扰。此外,在布局过程中,我们还需要注意电源和地线的线宽和间距,以确保它们能够满足电流和电压的需求,并减小信号的损耗和干扰。

串扰损耗的应对策略:

串扰损耗是高速PCB设计中常见的问题之一。它主要是由于信号线之间的电磁耦合作用而产生的。为了减小串扰损耗,我们可以采用多种方法,如增加信号线之间的间距、使用屏蔽线或差分线等。此外,在布线过程中,我们还需要注意信号的传输方向和路径,避免信号线的交叉和重叠。通过合理的布局和布线,我们可以有效地减小串扰损耗,提高信号的传输质量和稳定性。

通过阅读《高速PCB设计经验规则应用实践》,更加深刻认识到布局经验在高速PCB设计中的重要性。合理的布局规划、叠层布局、电源与地的布局以及串扰损耗的应对策略等经验法则都是我们在实际工作中需要不断学习和掌握的关键技能。这些经验法则不仅能够帮助我们提高PCB设计的效率和质量,还能够为我们解决设计过程中的难题提供有力的支持。

当然布局只是本书中关于PCB的高速设计的一个大方面,还根据实际经验对常遇到的特殊电路进行了分析,例如DCDC电路,BGA电路,ADC电路等等,针对特定的电路进行了独特的见解分析,还有我们在实际工作中不太关注的材料特性,这些都为高速PCB产生着重大的影响。

/3

/3

文章评论(0条评论)

登录后参与讨论