设计环境语言

2.1.1 Max+plusII如图2.1所示,MAX+PLUS II是Altera公司的全集成化可编程逻辑设计环境。MAX+plus II 界面友好,使用便捷,被誉为业界最易用易学的EDA软件。MAX+plus II支持原理图、VHDL和Verilog语言文本文件,以及波形与EDIF等格式的文件作为设计输入,并支持这些文件的任意混合设计。MAX+plusII具有门级仿真器,可以进行功能仿真和时序仿真,能够产生精确的仿真结果。在适配之后,MAX+plusII生成供时序仿真用的EDIF、VHDL和Verilog三种不同格式的网表文件。

MAX+plusII支持主流的第三方EDA工具,如Synopsys、Cadence、Synplicity、Mentor、Viewlogic、Exemplar和Model Technology等。MAX+plusII支持除APEX20K系列之外的所有Altera FPGA/CPLD大规模逻辑器件。

MAX+plusII的HDL文本编辑器是很有弹性的工具,提供多种硬件描述语言的文字编辑与合成的环境。其中包括有:

1.Altera Hardware Description Language (AHDL)

2.Very High Integrated Circuit Hardware Description Language (VHDL)

3.Verilog Hardware Description Language (Verilig HDL)

以AHDL语法编写的文件格式为*.tdf,以VHDL语法编写的文件格式则为*.vhd,而以Verilog HDL语法编写的文件格式则为*.v。可以设计程序创建一个符号文件供图形编辑器使用。

图2.1

2.1.2 VHDL

VHDL 的英文全名是VHSIC Hardware Description Language(VHSIC硬件描述语言)。VHSIC是Very High Speed Integrated Circuit的缩写,是20世纪80年代在美国国防部的资助下始创的,并最终导致了VHDL语言的出现。1987年底,VHDL被 IEEE 和美国国防部确认为标准硬件描述语言。VHDL主要用于描述数字系统的结构,行为,功能和接口。除了含有许多具有硬件特征的语句外,VHDL的语言形式和描述风格与句法是十分类似于一般的计算机高级语言。VHDL的程序结构特点是将一项工程设计,或称设计实体(可以是一个元件,一个电路模块或一个系统)分成外部(或称可视部分,及端口)和内部(或称不可视部分),既涉及实体的内部功能和算法完成部分。在对一个设计实体定义了外部界面后,一旦其内部开发完成后,其他的设计就可以直接调用这个实体。这种将设计实体分成内外部分的概念是VHDL系统设计的基本点。

描述 在这个语言首次开发出来时,其目标仅是一个使电路文本化的一种标准,为了使人们采用文本方式描述的设计能够被其他人没有二意性地所理解。因为用自然语言描述电路会产生二意性。 这个模型是让人来阅读的。 模拟的模型 作为模型语言,用于采用模拟软件进行模拟。这个模型是让仿真软件来阅读的。 综合的模型 在自动设计系统中,作为设计输入。这个模型是让综合软件来阅读的。

VHDL 语言能够成为标准化的硬件描述语言并获得广泛应用,它自身必然具有很多其他硬件描述语言所不具备的优点。归纳起来,VHDL语言主要具有以下优点:

(1)VHDL 语言功能强大,设计方式多样

(2)VHDL 语言具有强大的硬件描述能力

(3)VHDL 语言具有很强的移植能力

(4)VHDL 语言的设计描述与器件无关

(5)VHDL 语言程序易于共享和复用

2.2 设计要求

1、设计一个电子定时器,控制洗衣机作如下运转:定时启动?正转?暂停?反转?暂停?定时未到回到“正转?暂停?……”,定时到则停止;

2、用两个数码管显示洗涤的预置时间(分钟数),按倒计时方式对洗涤过程作计时显示,直到时间到停机;洗涤过程由“开始”信号开始;

3、三只LED灯表示“正转”、“反转”、“暂停”三个状态。

2.3 设计流程

3 设计程序

3.1减数计时模块由于洗衣机有工作时间,必须要一模块来控制它的工作时间范围,当洗衣机开

始工作后,减法计数器即会实现减数功能,直到时间减到零,洗衣机便停止工作。

(1)程序

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity count is

- port(clk,tla,start,enter:in std_logic;

- ini:in std_logic_vector(7 downto 0);

- show:out std_logic_vector(7 downto 0);

- finish:out std_logic);

- end count;

- architecture one of count is

- signal fini:std_logic;

- signal show1:std_logic_vector(7 downto 0);

- begin

- process(tla,clk,start)

- variable num:std_logic_vector(7 downto 0);

- begin

- if enter='1' then num:=ini;

- elsif(tla'event and tla='1')then

- if start='1'and num/=0 then

- num:=num-1;

- end if;

- end if;

- if enter='0'and num=0 then

- fini<='1';num:="00000000";

- else fini<='0';

- show1<=num;

- end if;

- end process;

- process(clk)

- begin

- if clk'event and clk='1'then finish<=fini;

- show<=show1;

- end if;

- end process;

- end;

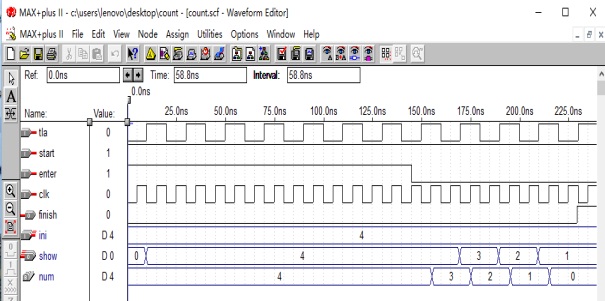

(2)仿真波形

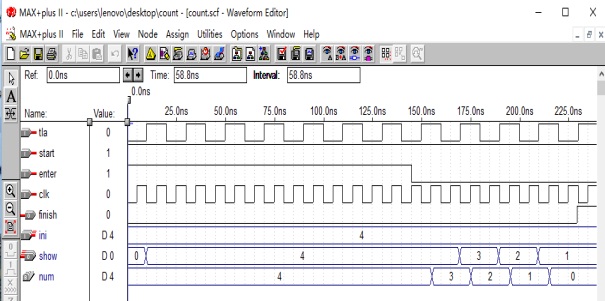

减数计时模块仿真如图3.1所示,start为电源开关,enter反应时间设置情况,当洗衣机开始工作,时由脉冲信号tla进行控制完成倒计时,并通过show进行显示。

图3.1

图3.1

3.2 预置时间模块设计与仿真

此模块由一个累加器和一个命令控制器组成,用来实现预置时间的功能,洗涤时间数以分钟为单位,用户可以根据自己的需求来设置洗涤时间的长短。

通过累加预置具体洗衣时间。

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity adder is

- port(in1:in std_logic;

- q:out std_logic_vector(2 downto 0));

- end adder;

- architecture one of adder is

- signal add:std_logic_vector(2 downto 0);

- begin

- q<=add;

- process(in1)

- begin

- if in1'event and in1='1' then

- add<=add+1;

- end if;

- end process;

- end;

累加器模块仿真波形如图3.2.1所示,通过累加的方式完成时间设置。

图3.2.1

将输入的三位二进制时间信号编码成十进制数输出到减法计数器电路。

- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- ENTITY ORDER IS

- PORT(CLK:IN STD_LOGIC;

- ORDER:IN STD_LOGIC_VECTOR(2 DOWNTO 0);

- TIME:OUT INTEGER RANGE 128 DOWNTO 0);

- END ORDER;

- ARCHITECTURE ONE OF ORDER IS

- BEGIN

- PROCESS(CLK)

- BEGIN

- CASE ORDER IS

- WHEN "000" =>TIME<=1;

- WHEN "001" =>TIME<=2;

- WHEN "010" =>TIME<=3;

- WHEN "011" =>TIME<=4;

- WHEN "100" =>TIME<=5;

- WHEN "101" =>TIME<=6;

- WHEN "110" =>TIME<=7;

- WHEN "111" =>TIME<=8;

- WHEN OTHERS =>TIME<=0;

- END CASE;

- END PROCESS;

- END;

命令控制器模块仿真波形如图3.2.2所示,将输入的二进制信号转化为十进制信号。

图3.2.2

图3.2.2

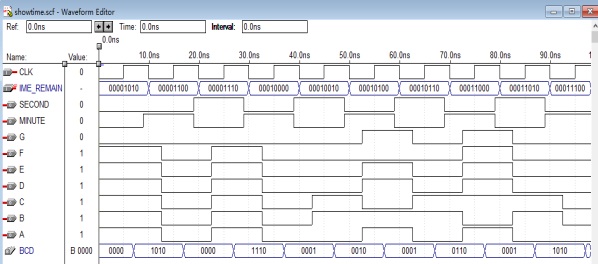

3.3数码管显示模块:

根据设计要求,必须将洗衣机的工作状态及工作时间在数码管和指示灯上显示出来,此模块是用来控制洗衣机的工作状态及工作的频率,并把工作状态及工作时间显示出来。a,b,c,d,e,f,g分别对应数码管的七段,minute和second分别位选两个数码管,显示十位和个位。- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- ENTITY SHOWTIME IS

- PORT (TIME_REMAIN:IN STD_LOGIC_VECTOR (7 DOWNTO 0);

- CLK:IN STD_LOGIC;

- MINUTE,SECOND:OUT STD_LOGIC;

- A,B,C,D,E,F,G:OUT STD_LOGIC);

- END SHOWTIME;

- ARCHITECTURE ONE OF SHOWTIME IS

- SIGNAL TEMP:STD_LOGIC_VECTOR(6 DOWNTO 0);

- SIGNAL BCD:STD_LOGIC_VECTOR(3 DOWNTO 0);

- SIGNAL CHOOSE:STD_LOGIC;

- BEGIN

- PROCESS (CLK)

- BEGIN

- IF(CLK'EVENT AND CLK='1')THEN

- CHOOSE<=NOT CHOOSE;

- IF(CHOOSE='1')THEN

- MINUTE<='0';SECOND<='1';

- BCD<=TIME_REMAIN(7 DOWNTO 4);

- ELSE

- MINUTE<='1';SECOND<='0';

- BCD<=TIME_REMAIN(3 DOWNTO 0);

- END IF;

- END IF;

- END PROCESS;

- PROCESS(BCD)

- BEGIN

- CASE BCD IS

- WHEN "0000" =>TEMP<="1111110";--0

- WHEN "0001" =>TEMP<="0110000";--1

- WHEN "0010" =>TEMP<="1101101";--2

- WHEN "0011" =>TEMP<="1111001";--3

- WHEN "0100" =>TEMP<="0110011";--4

- WHEN "0101" =>TEMP<="1011011";--5

- WHEN "0110" =>TEMP<="1011111";--6

- WHEN "0111" =>TEMP<="0001111";--7

- WHEN "1000" =>TEMP<="1111111";--8

- WHEN "1001" =>TEMP<="1111011";--9

- WHEN others =>TEMP<="0000000";

- END CASE;

- A<=TEMP(6);B<=TEMP(5);C<=TEMP(4);D<=TEMP(3);E<=TEMP(2);F<=TEMP(1);G<=TEMP(0);

- END PROCESS;

- END;

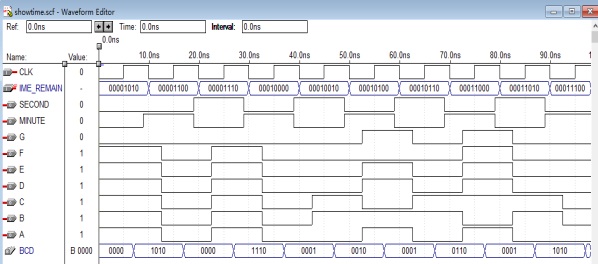

数码显示模块如图3.3所示,通过数码管MINUTE和SECOND显示十位和个位的数。

图3.3

3.4状态机模块:

接收电机运行状态信号,译码后实时控制电机的正传、反转和暂停。

- library ieee;

- use ieee.std_logic_1164.all;

- entity move is

- port(out_1,out_2:in std_logic;

- REV,RUN,PAUSE:buffer std_logic);

- end move;

- architecture move of move is

- signal choose:std_logic_vector(1 downto 0);

- begin

- choose(1)<=out_1;

- choose(0)<=out_2;

- process(choose)

- begin

- case choose is

- when "00"=>REV<='0';RUN<='0';PAUSE<='1';

- when "10"=>REV<='0';RUN<='1';PAUSE<='0';

- when "01"=>REV<='1';RUN<='0';PAUSE<='0';

- when others=>REV<='0';RUN<='0';PAUSE<='0';

- end case;

- REV<=out_2;RUN<=out_1;PAUSE<=not(out_1 or out_2);

- end process;

- end move;

状态机模块如图3.4所示,接受电机状态信号,完成电机正转RUN、反转REV和暂停PAUSE的控制

图3.4

采用的是模块化层次化的设计方法,通过这样分模块化的思考方式,设计显得相对容易了很多,思路也相对简单了很多。洗衣机控制器主要有三个状态,要实现几种状态的多次循环改变,预置时间,还有计时和数码管动态显示的功能。因此电路可主要分为以下几个模块:预置时间和减法计数器模块、数码管动态显示模块、状态控制模块。通过每个模块的设计,最后运用VHDL语言的进程语句进行模块间的组合,从而完成程序的设计。

通过这次设计,我对VHDL语言有了基本的掌握,对其设计方法也有了一些技巧性的了解,为将来的硬件设计打下了一定的基础。对于FPGA编程、定时器和计数器的设计都熟悉起来了,加深了对时序组合电路印象。同时学会了自顶向下的数字系统设计思路,在设计一个系统时,首先要对一个系统的功能做充分的了解,然后模块划分也应该进行合理的安排,模块与模块之间又应该如何连接,同时应该适当考虑电路实验问题。

通过洗衣机设计,还可以使我们对于FPGA的工作原理,有了较之前更清楚明白的理解。FPGA可以应用到许多方面,通过搭载不同的内核,可以应用到不同系统中,完成多种任务设计。由此可见,对于相关专业的学习与工作来说,学好FPGA,学会运用它丰富的功能,是十分有必要的。在学习一门技术之前我们往往从它的编程语言开始,如同学习单片机一样,我们从c语言开始入门,当掌握了c语言之后,开发单片机应用程序也就不是什么难事了。学习fpga也是如此,fpga的编程语言有两种:vhdl和verilog,这两种语言都适合用于fpga的编程。

总的来讲,在对FPGA的设计中,让我对于可编程逻辑器件的相关理论有了更深刻的理解与掌握,且锻炼了自己熟悉新软件能力,并且对VHDL语言有了一定的了解,对程序的设计有了直观的体验,从而得到许多收获。

图3.1

图3.1

图3.2.2

图3.2.2

/2

/2

文章评论(0条评论)

登录后参与讨论