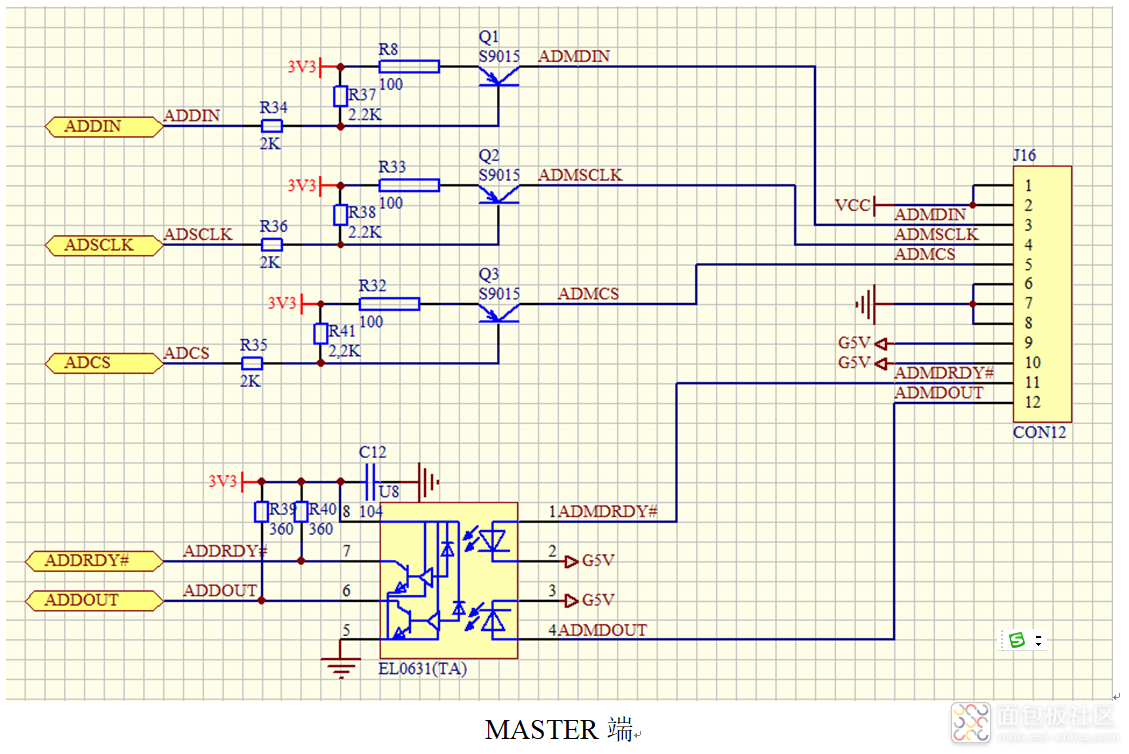

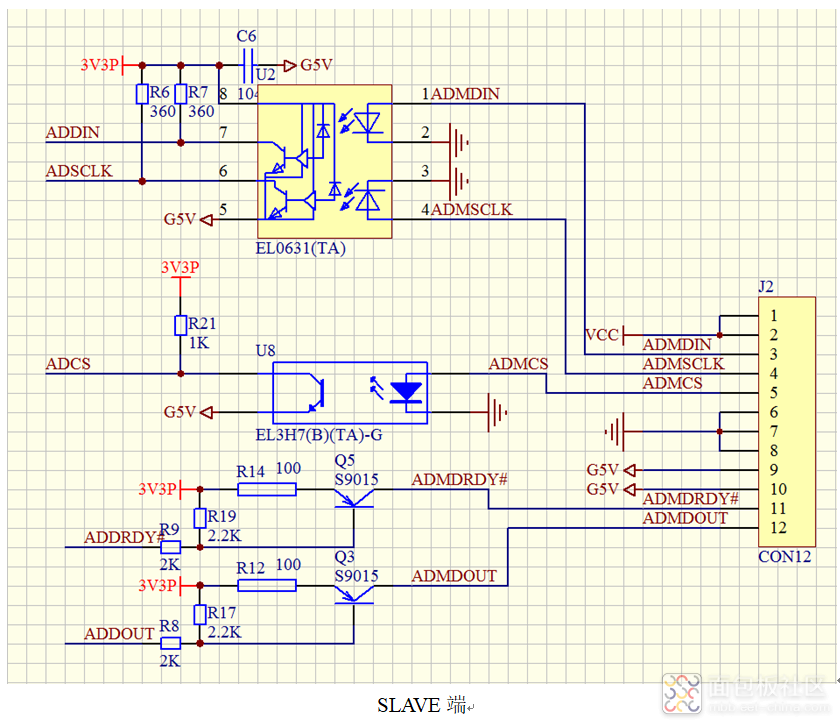

制作一个SPI光隔离电路,用于读取24位ΣΔADC,隔离的目的是防止数字部分的噪声影响ADC采集。SPI设计速度希望达到2M以上。图中MASTER端产生 CS SCLK MOSI信号驱动SLAVE(ADC)端光耦中的发光二极管。并接收MISO及DRDY信号。

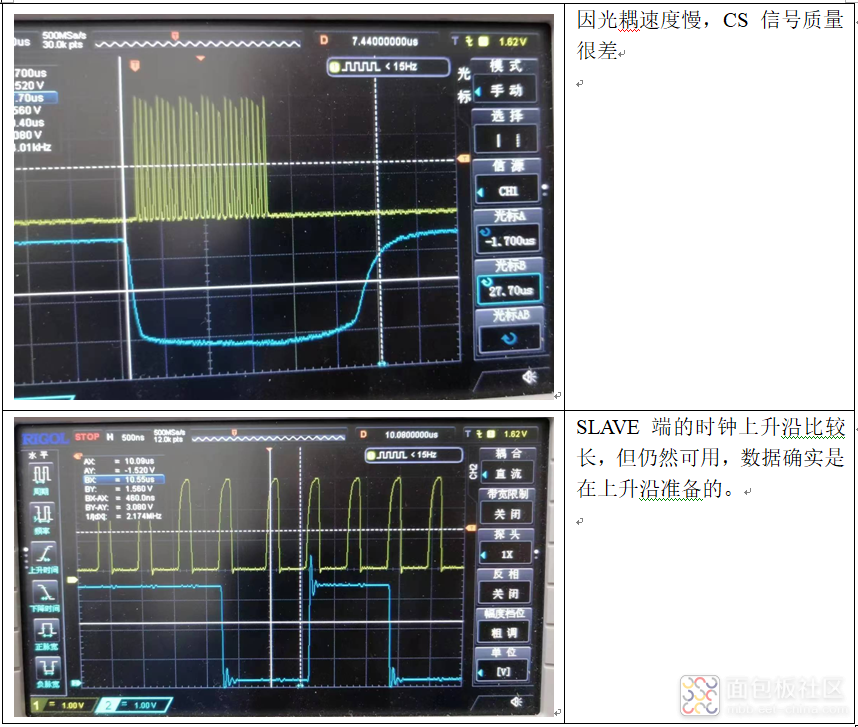

设计时认为SPISS这个信号很慢,可以用一个慢一点(便宜)的光耦。实际测试时发现,这个选择很不明智。SS下降沿时有可能无法与时钟同步,SS上升沿时则严重加长了等待时间。限制了SPI的速度,也降低了时序可靠性。实际使用时,应该使用与用于时钟线一致的光耦。

实际使用时发现,使用MCU硬件SPI驱动这个电路,读数不稳定。有时会出现ADC无响应这样的问题。降低SPI时钟速率也无效果。

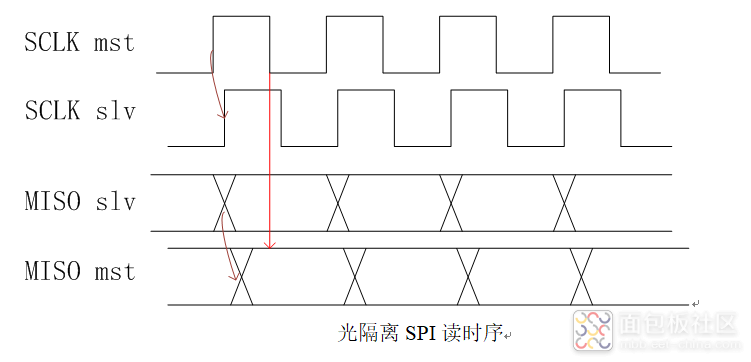

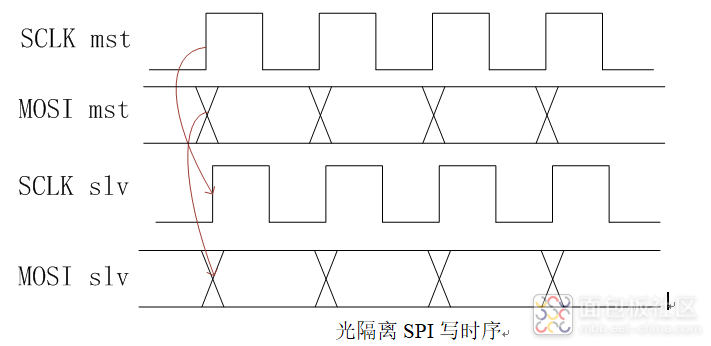

分析一下电路,在MASTER端,产生SCLK信号,隔离输出会延迟 100ns,SLAVE端在隔离SCLK信号上升沿输出数据,使用速度能达到10M的高速光耦,数据经隔离后延迟100ns,在MASTER端恢复,MASTER端在时钟下降沿采样MISO 得到数据。从图中可以看出,如果两次隔离总延迟超过半个SCLK时钟周期,则无法读取到正确数据。也就是说,这个SPI光隔离的速度限制在4倍总延时,在这个例子中是400ns,为2.5Mhz。考虑到需要有一些建立、保持时间。这个速度还会更低一些。

隔离写入时,并不存在问题,因为时钟和数据时同步延迟的。

分析认为,光耦的非均匀传输延迟导致输出SCLK和SDATA之间的相位关系混乱,从而导致ADC控制异常。改成用GPIO 模拟 SPI后,针对光耦延迟问题作优化。能稳定控制了。

由上面的分析及实际的测试可以看出,光隔离用于SPI会有速度限制。需要隔离的信号比较多,且信号之间还有严格的时序关系。所以设计的难度,主要是调试时序的难度比较大。上述的隔离电路用于UART不会有问题。因为传输是异步的。最多不能及时收到数据。但并不会出错。实测光隔离UART达到2Mb波特率。

作者: southcreek, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-408807.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/2

/2

luckyzy2000 2023-4-18 13:31

southcreek 2023-4-14 14:17

型号: CA-IS3722HS

品牌: Chipanalog(川土微)

封装: SOIC-8

• 信号传输速率: DC to 150Mbps

• 宽电源电压范围:2.5V to 5.5V

• 宽温度范围: -40°C to 125°C

• 无需启动初始化

• 默认输出高电平和低电平选项

• 优异的电磁抗扰度

• 高 CMTI: ±100kV/µs (典型值)

• 低功耗,(典型值):

▪ 电流为 1.5mA/通道(5V 电源供电 1Mbps 时)

▪ 电流为 6.6mA/通道(5V 电源供电 100Mbps

时)

• 精确时序 (典型值)

▪ 8ns 传播延迟

▪ 1ns 脉冲宽度失真

▪ 2ns 传播延迟偏差

▪ 5ns 最小脉冲宽度

• 高达 5KVRMS的隔离电压