最近在学习Synplify Pro综合,以前学校做项目时就只用QuartusII综合草草了事,工作了发现有太多的东西需要学习,包括不同的专业领域、不同的开发工具。所以趁现在工作还算轻松时自己恶补一下这些开发软件,先从Synplify Pro下手,现在干的活主要针对Altera器件的,就分享一下它与QuartusII的联合工作方法。在QuartusII 10.1手册中,详细说明了对Synplify的支持,并介绍了设计流程,

用QuartusII软件调用Synplify进行设计的通用方法,基本可分为一下几步:

1) 编写HDL代码

2) 在Synplify Pro中建立工程,加入编写完成得HDL代码

3) 在Synplify Pro中选择器件,加入时序约束和编译指令,使软件在综合时能优化设计

4) Synplify Pro对设计进行综合

5) 在QuartusII中建立工程,加入Synplify Pro综合得到的几个文件:*.vqm(Verilog Quartus Mapping File), *.scf(Synopsys Constraints Format File)和*.tcl(Tcl Constraints File)

6) 在QuartusII中place & route,得到最终设计结果

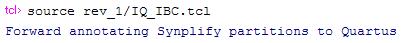

我按流程对自己的设计走了一遍,到第(5)部时发现了问题,加入时序约束文件时,因为QuartusII的时序约束文件是*.sdc(Synopsys Design Constraints File),不知道跟*.scf有啥区别,因为打开文件比较后发现两者的语法相同,先不管,编译后却发现*.scf并没有起效果,在TimeQuest Timeing Analyzer没约束;另外对加入*.tcl文件感到费解。为了究其原因,又仔细阅读了手册,发现了问题所在,原先我在QuartusII建工程时又重新选择了器件,其实这些都不用手动做,Synplify Pro其实已经将这些操作归成了一个tcl文件,只要调用这个tcl文件,所有操作一步搞定,其中就包括时序约束,会自动调用*.scf进行时序约束,因此真正加入QuartusII中的文件只有*.vqm一个,调用tcl文件可打开QuartusII中的View->Utility Windows->Tcl Console,在窗口中敲入source <synplify project_name>.tcl,如图1所示,然后直接编译就OK了。

图1

图1

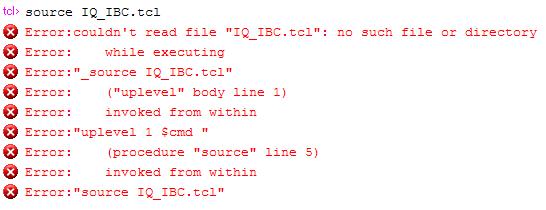

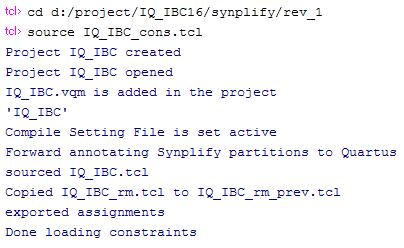

仔细看了手册,发现其实根本不用手动在QuartusII中建立工程,首先打开QuartusII软件,不用打开工程或者建立新工程,只需要调用<synplify project_name>_cons.tcl这个文件,一切都搞定,从建立QuartusII工程、加入*.vqm文件、设置器件、时序约束,编译的按钮都无需按,直接开始编译,真是方便。调用<synplify project_name>_cons.tcl这个文件时,需要先进入这个文件所在目录,不然就会提示找不到文件,如图2所示。进入方法如图3所示,这些是TCL语法,我也是初学啊!

图2

图3

先介绍到这儿,可以发现在文档中有关于TCL和时序约束方面没有细讲,因为自己对这些方面也是初学,在后续的日志中边学习边分享!

/1

/1

用户1516610 2015-8-8 16:57

用户377235 2014-8-13 16:17