不知道是在学校学的东西多还是走出来了学的多,据说楷哥就是嫌工作阻碍了自己的进步才回去读研的,而大多数人还是参加了工作才发现自己以前什么都不会的吧。总之知识离了实践便百无一用,作为多数派中的一员,还是赶紧充充电的好。慎之、慎之。

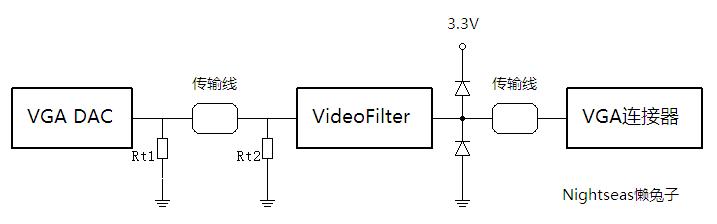

VGA的输出接口电路就是VGA DAC到VGA连接器(通常为DB15)之间的电路,包括RGB信号、行场同步和DDC串行信号。不同的芯片,其生产商会在手册中提供相应的设计参考。下面就是一个典型的RGB信号接口电路:

其中Rt1和Rt2分别是DAC输出端和滤波电路输入端的端接电阻,通常为150ohm,当然了这和PCB传输线上的阻抗有关,芯片手册会给出推荐的Layout长度和线间距等要求。ESD(Electro-Static discharge)二极管是静电释放二极管,这个比较好理解,如果静电放电尖峰是正压,连接电源的二极管导通,尖峰就会被电源网络吸收;相反,连接GND的二级管导通,负压尖峰会被GND网络吸收。ESD二极管的电源和地之间应加一个104去耦电容,滤除3.3V电源带来的干扰。

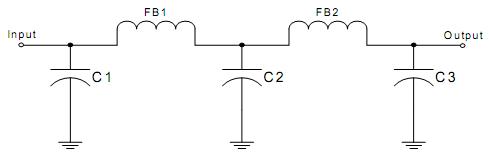

前面的都好说,重点是这个Video Filter。下图是一个截止频率为200MHz的低通滤波器,在965芯片组中,Intel会告诉你C1~C3分别选用10pF、22pF、10pF的0603陶瓷电容,FB1和FB2是47ohm@100MHz的磁珠。

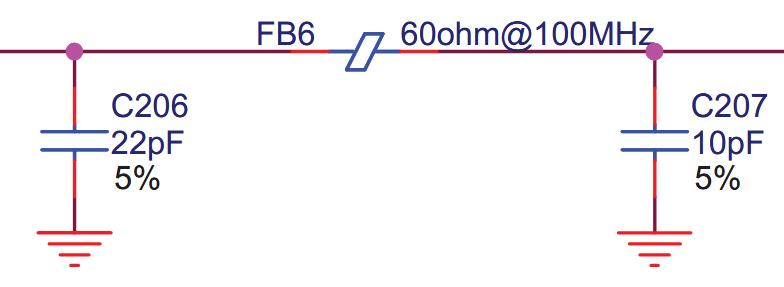

而在包含945芯片组的主板中,厂家有时会采用一个稍简单些的电路,如图。22pF可以使用CIS电容。

然而令我不解的是这样一个电路的具体作用是什么?Intel说这是用于解决EMI问题的,然后告诉你如果不这样做会如何如何,通过不了EMC测试,具体的问题当然不会深谈。于是我只能回去翻书(学艺不精啊),还真找到了解释。原来这个滤波电路主要是为了解决采用了连接器后电流环路互感引起的串扰。在一个简单模型里,这种串扰正比于环路间的互感L和dI/dt,而在连接器的驱动端并联电容可以减缓信号的上升从而降低串扰,相当于衰减高频分量(又是上升时间,看来高速电路问题最主要的因素就是信号上升时间呀)。需要注意的是,这个电容应该安装在连接器驱动端而不是接收端,如果在接收端放置电容只会使冲击电流增加并使情况恶化,同时,在电容前串联阻抗,如磁珠和电阻,可以提高电容的效果。因为电容是有滤波作用范围的,此滤波器要尽可能接近连接器放置。端接电阻也应当靠近芯片摆放。

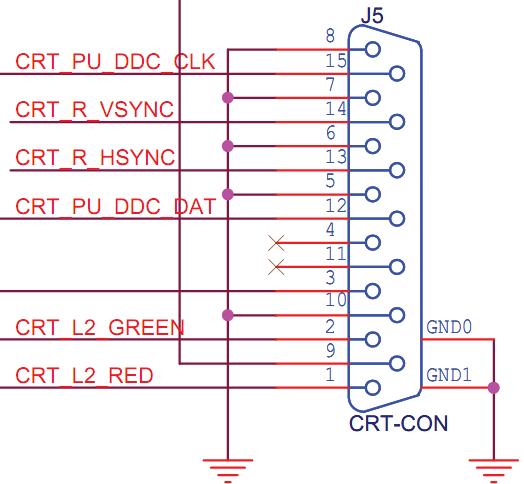

另外DB15连接器中大量的GND也是通过接地改变电流返回的路径从而降低串扰:

由此可知,对于不同的芯片和连接器,这部分电路的要求也不尽相同,例如NV6800显卡的公版电路中,DAC的RGB输出只加一个150ohm源端端接电阻,就可以直接连接MXM连接器了。

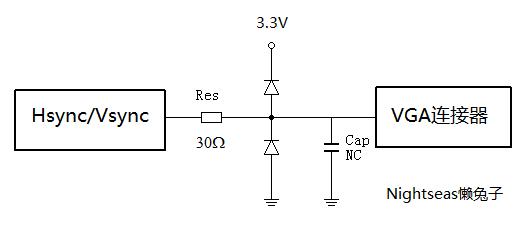

行场同步信号的处理要简单一些,匹配电阻常在30ohm左右,输出端会预留一个电容的位置,依然是用作上面提到的EMI问题。

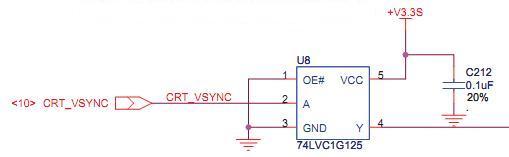

行场同步信号也可以使用两个三态缓冲门74LVC1G125来增强驱动能力并进行信号隔离,匹配电阻需要加载在74LVC1G125的输出一侧,而二极管就可以省略了。

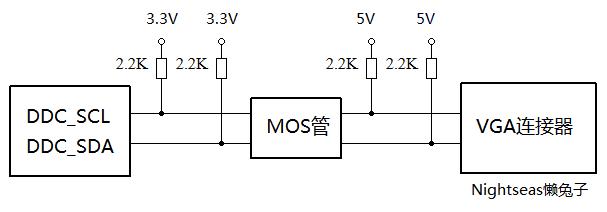

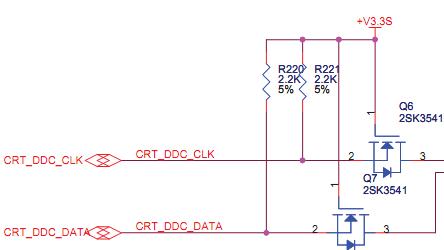

DDC信号是显示数据控制信号,其实就是一个I2C,包含SCL和SDA两条线,这里需要做信号隔离和电平转换,具体的形式有很多种,下面是一种典型方式:

如果系统的VGA输出不使用(比如采用PCIe的显示芯片),只需将RGB信号接电阻接地(965中推荐阻值为75ohm),其它信号直接接地就可以了。

用户1528429 2014-2-17 17:30

用户377235 2013-4-20 06:59

用户377235 2012-2-11 10:40

用户377235 2012-2-11 09:59

为什么行场同步信号匹配电阻要在30欧左右?到底是怎么算的?这问题一直困扰着我

用户1569902 2011-10-20 22:45