在开篇前先推荐两篇文档,一篇是altera的官方文档 Appling Multicycle Execptions in the TimeQuest Timing Analyzer ,另一篇是riple兄很早之前推荐过的Multicycles Exception Between Two Synchronous Clock,这两篇都是关于多周期约束很好的上手文档,虽然可以快速上手解决当务之急,但事后不免还会有些疑惑。TimeQuest中的多周期约束语法的设置选项有:基于setup(建立时间)的个数,基于hold(保持时间)的个数,start模式和end模式,如下所示。

set_multicycle_path -setup -start from [get_clocks {clk_s}] to [get_clocks {clk_r}] 2

set_multicycle_path -hold -end from [get_clocks {clk_s}] to [get_clocks {clk_r}] 2

但在使用过程中,为什么有时只设置基于建立时间的多周期个数就可以了?而为什么有时建立时间和保持时间的多周期个数都要设置?保持时间设置和建立时间设置存在什么依赖关系?为什么会有start和end两种模式,分别在什么情况下使用?我们是TimeQuest的用户,用户使用产品时只会去关心自己的需求,而用户成千上万,需求也千奇百怪,产品设计者为了满足所有用户,必须提高产品的通用性,最简单的方法就是增加选项模式,当一个需求简单的用户使用这个通用产品时,面对多重的选择和模式,往往会无从下手,因为根本就不知道这些选项设置的作用,自然就会产生上述的那些为什么。要解答这些为什么,我们可以试着换位思考,从TimeQuest设计者的角度出发,如何设计多周期约束的语法规则?

明确设计目的

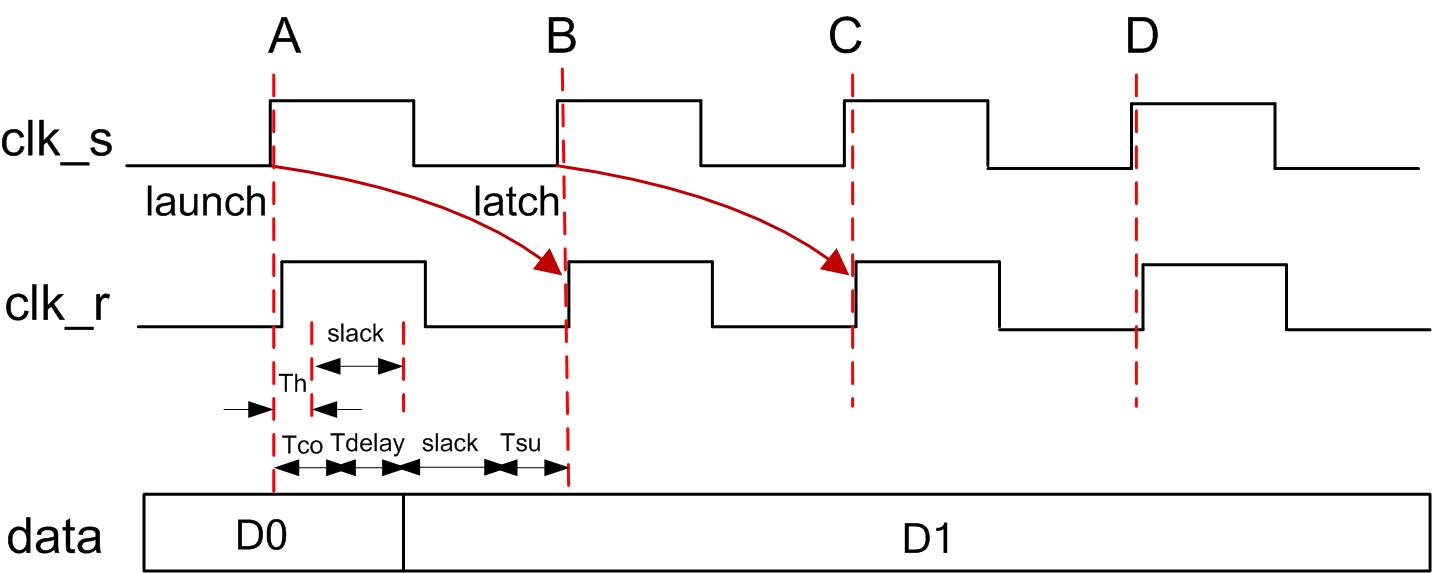

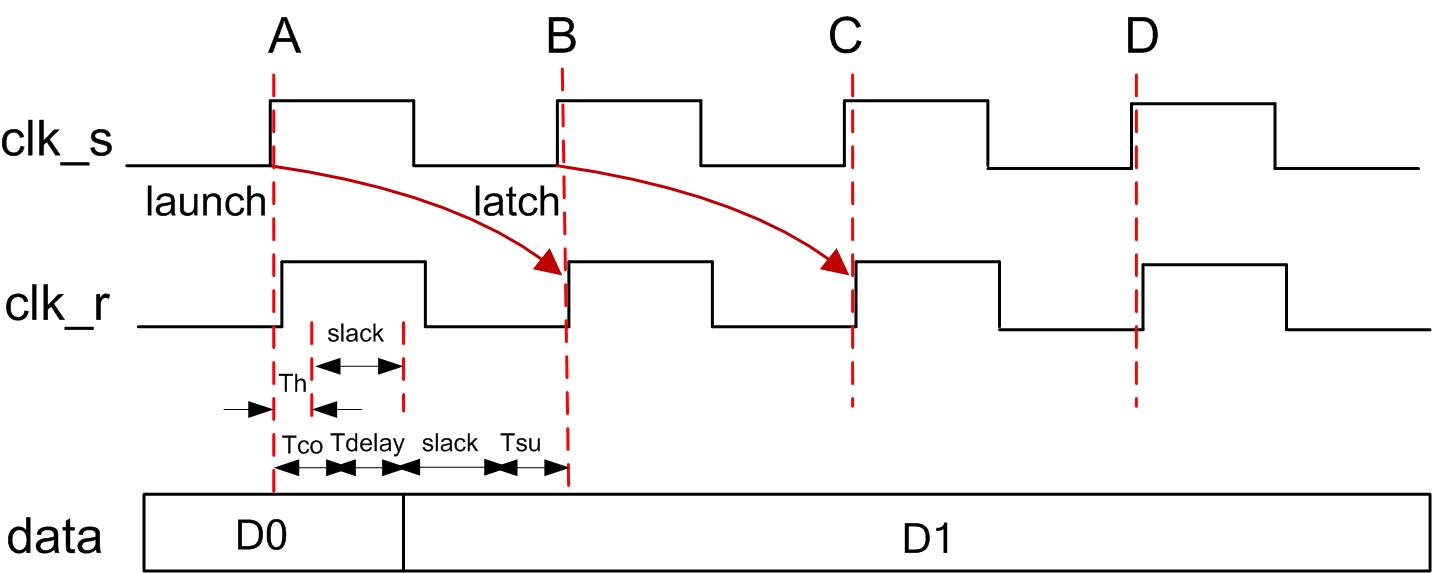

先来看看一个最常见的发送接收波形如图一所示,A时刻发送的数据B时刻锁存,launch(发送)边沿和latch(锁存)边沿间隔为一个时钟周期。

图一

这种情况下,建立时间和保持时间裕量为

setup slack = (current latch edge - current launch edge ) + Tskew - (Tdelay + Tco + Tsu)

= T + Tskew - (Tdelay + Tco + Tsu)

hold slack = Tdelay + Tco - (Th + previous latch edge - current launch edge)

= Tdelay + Tco - Th

其中Tskew是时钟偏斜,Tdelay为传输延迟,Tco为源寄存器的输出延迟,Tsu和Th为寄存器需要的建立保持时间。

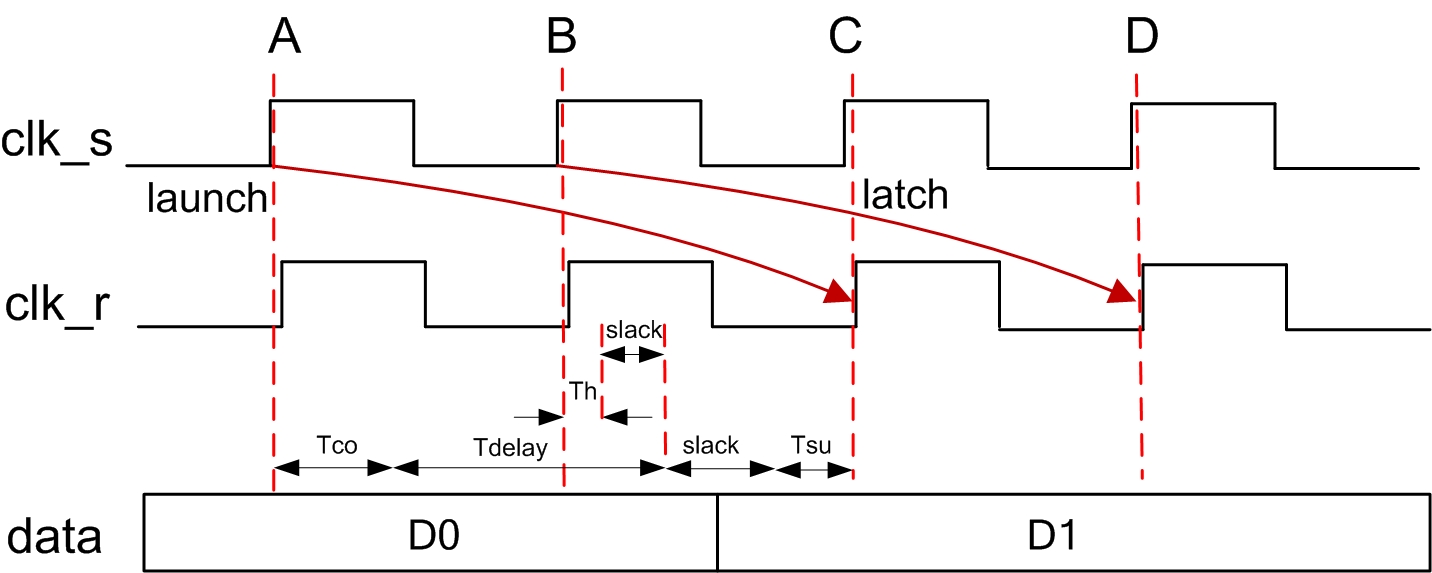

如果接收波形整体延迟一个时钟周期,如图二所示,latch边沿改变了,A时刻发送的数据C时刻锁存,B时刻发送的数据D时刻锁存。

图二

此时,我们期望的建立时间和保持时间裕量为

setup slack = (current latch edge - current launch edge ) + Tskew - (Tdelay + Tco + Tsu)

= 2*T + Tskew - (Tdelay + Tco + Tsu)

hold slack = Tdelay + Tco - (Th + previout latch edge - current launch edge)

= Tdelay+Tco - (T+Th)

和前一种情况比较,建立时间裕量宽裕了一个周期,保持时间裕量缩紧了一个周期,但TimeQuest并不知道latch边沿变了,如果不进行多周期约束,仍按照前一种情况的裕量去约束,结果就会使得建立时间多了没必要的裕量,而保持时间的裕量可能不足。所谓的多周期是相对单周期而言的,launch和latch默认间隔为单周期,当launch和latch间隔为多个周期时,就需要用到多周期约束了,一个完整的时序分析路径是由Tskew、Tco、Tdelay、Tsu、Th以及launch时刻和latch时刻等共同决定的,后两项会随着用户不同的需求而改变,TimeQuest无法自动获得,所以多周期约束语法规则设计的目的就是准确的告诉TimeQuest波形何时launch何时latch,进行适当的建立保持约束。

明确TimeQuest的需求

我们已经知道了TimeQuest无法自己获取launch时刻和latch时刻,必须由用户提供,那么TimeQuest具体需要哪些信息才能完全了解发送接收波形呢?

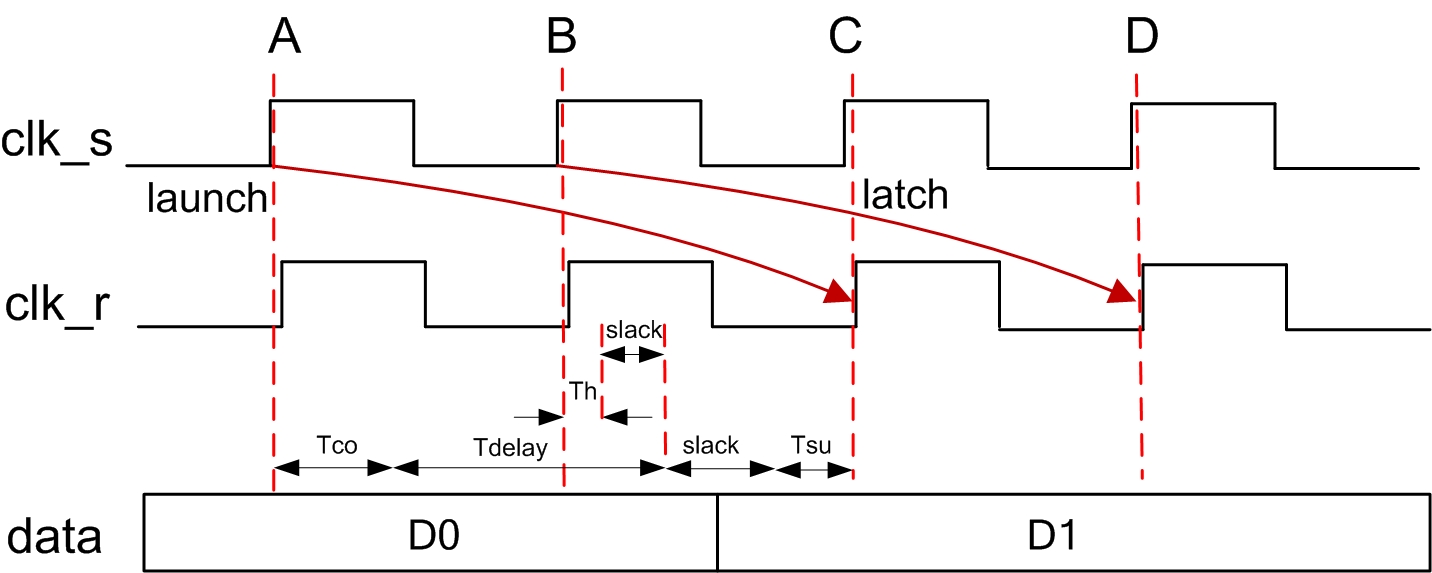

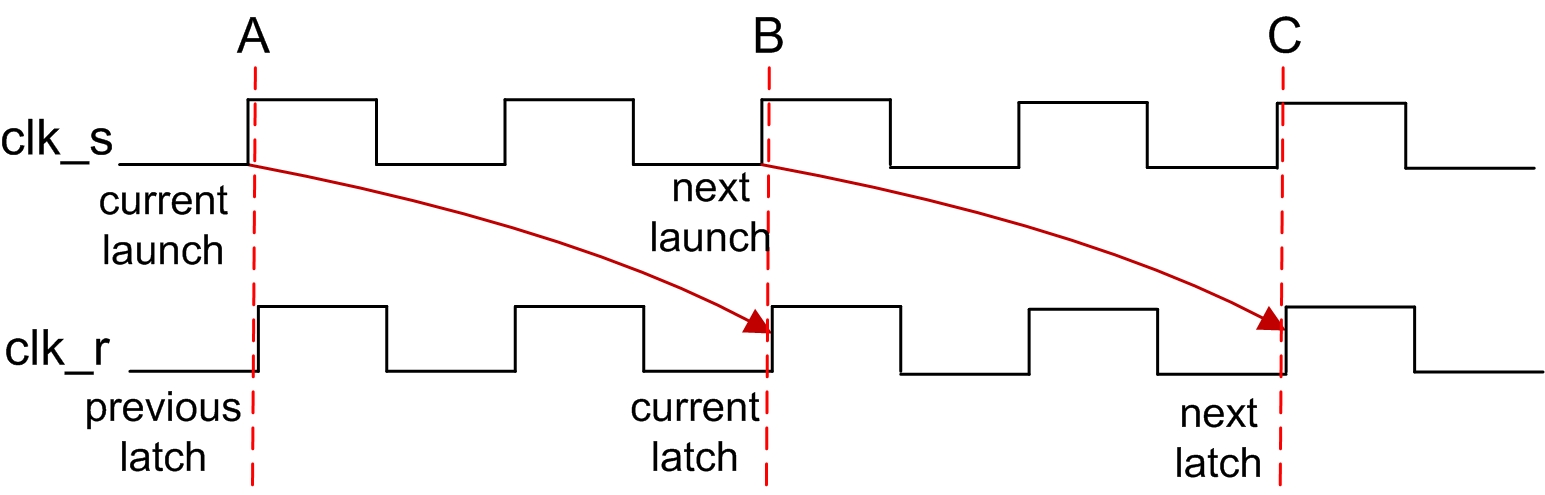

举一个典型的多周期波形,如图三所示,A时刻发送的数据B时刻锁存,B时刻发送的数据C时刻锁存,A为current launch,B即为current latch又是next launch,C是next latch。

图三

图三的发送接收关系,我们可以表示为下面几个式子:

current latch - current launch = 2个时钟周期

current latch - next launch = 0个时钟周期

previous latch - current launch = 0个时钟周期

由于波形的周期性,后两个表达式是完全等效的,图二的发送接收关系同样可以表示为:

current latch - current launch = 2个时钟周期

current latch - next launch = 1个时钟周期

previous latch - current launch = 1个时钟周期

将这几个表达式推广到更多不同的例子,会发现只要知道了current launch、current latch、next launch和previous latch就能确定任何形式的发送接收波形,因此TimeQuest只需获得这四个量,也就清楚波形的真实情况了。

明确用户的需求

假设用户的波形如图二所示,相比常见的图一单周期波形,建立时间宽裕了一个周期,而保持时间紧缩了一个周期,作为用户,其实并不关心current launch、current latch、next launch和previous latch这些量,只会关注如何把变化了的建立保持关系告知TimeQuest,让其在该放松的地方放宽约束,该紧缩的地方加强约束。

-------------------------------------------------------------------------------------------------------------

/5

/5

用户419742 2012-5-8 20:54

ashly0903_595850101 2012-5-8 15:54