一 直以来,一般人下载FPGA 的配置芯片,都是用ASP下载模式,USB Blaster接口要插来插去,真的是麻烦,其实,下载FPGA 的配置芯片,还有另外的方法,那就是仍然通过JTAG下载,二换一种配置模式,下载jic文件或者是jam 文件,对然这样做,对实际开发来说,对一般实验意义不怎么大,但是若是批量开发,不仅可以减少板子的费用(因为不用ASP下载接口了,面积减少),而且省 去了不少器件,应该有效益。

具体做法,在下面我会详细说明,让开发变得更简单。

告别ASP(主动串行编程)下载模式... 1

——JTAG---EPCS1. 1

序... 1

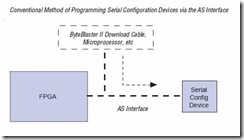

一、ASP、JTAG两种模式下子EPCS的比较... 2

流程图... 2

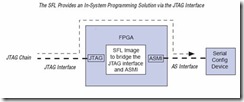

Serial Flash Loader 2

二、 配置下载的全过程... 3

1、新建工程... 3

2、编写Water_Led.v. 3

3、加入Serial Flash Loader的IP. 4

4、添加程序... 4

5、把sof文件转换为jic文件... 4

6、把jic文件转换为jam文件或者svf文件... 7

7、编程串行配置器件,下载程序... 7

9、效果... 7

三、 结论感受... 7

The Serial Flash Loader, SFL, provides the ability to program an active serial configuration device through the FPGA’s JTAG pins. The SFL creates a bridge between the FPGA JTAG pins and the FPGA ASMI interface. The SFL, which consumes ~188 logic elements, must be included in the design as this instantiates the bridge. The SFL bridge is instantiated using the Quartus II MegaWizard Plug-In Manager.

module JTAG_EPCS1(

input clk, //50MHZ on the board

output reg [7:0] Water_Led

);

reg [21:0] cnt;

reg clk_led;//10HZ

always@(posedge clk)

begin

if(cnt<22'd2500000)

cnt<=cnt+1'b1;

else

begin

cnt<=0;

clk_led<=~clk_led;

end

end

always@(posedge clk_led)

begin

case(Water_Led)

8'b00000000 : Water_Led<=8'b00000001;

8'b00000001 : Water_Led<=8'b00000011;

8'b00000011 : Water_Led<=8'b00000111;

8'b00000111 : Water_Led<=8'b00001111;

8'b00001111 : Water_Led<=8'b00011111;

8'b00011111 : Water_Led<=8'b00111111;

8'b00111111 : Water_Led<=8'b01111111;

8'b01111111 : Water_Led<=8'b11111111;

8'b11111111 : Water_Led<=8'b11111110;

8'b11111110 : Water_Led<=8'b11111100;

8'b11111100 : Water_Led<=8'b11111000;

8'b11111000 : Water_Led<=8'b11110000;

8'b11110000 : Water_Led<=8'b11100000;

8'b11100000 : Water_Led<=8'b11000000;

8'b11000000 : Water_Led<=8'b10000000;

8'b10000000 : Water_Led<=8'b00000000;

endcase

end

endmodule

Serial_Flash_Loader u_S(

.noein(1'b0)

);

endmodule

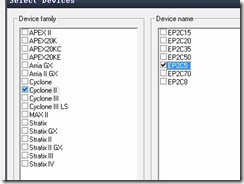

(1)

(2)

选择JTAG Indirect Configuration File、EPCS1,以及保存的jic文件名

选择Memory Map File

(3)

选择目标板器件

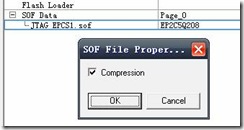

(4) ![]()

在SOF DATA添加工程中sof文件,用来转换为mif文件

(5)

选择压缩sof文件的模式,以减少空间

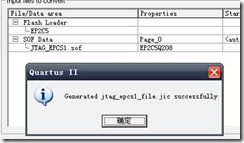

转换成功

Alternatively,这部可以不选,直接第7部下载程序,我都不知道这有什么意义,有兴趣的人,可以参照文档Configuring EPCS Devices via JTAG v1.0

重启之后,流水灯就开始流动,说明程序已经通过JTAG下载到EPCS芯片中,实现了想要的功能。

刚接触到这个东西的 时候,我用的Q II 版本是9.1 的,当时测试了好多,看了好多的pdf ,可是就是下载不进去,当时还以为是板子电路的原因,或者是自己配制方法不对,工夫不到家,于是那时候也因为别的事情,再也没有碰过了。

后 来,记得去年年底,有个网友告诉我Q II 9.1有bug,固化程序上有问题,所以无论是通过ASP下载模式,还是通过JTAG下载模式配置下载到EPCS都不能成功,后来又Fans直接向 Altera求助,最后,很快,出来了Q II 9.1 SP1,大概是个补丁吧,要覆盖安装的,不是很小也不是很大,现在,果然可以了,纠结了那么久的时间原来不是我的错,是软件的错啊。

现在好了,呵呵,告诉大家我的心得,也希望不要像我这样走歪路,还在用Q II 9.1 的朋友,还是赶紧去ftp://ftp.altera.com/outgoing/release/ 下载Q II 9.1 SP1吧,省的走歪路,呵呵。

/4

/4

文章评论(0条评论)

登录后参与讨论