本节以MPC8548处理器为例说明HOST主桥在PowerPC处理器中的实现机制,并简要介绍x86处理器系统使用的HOST主桥。

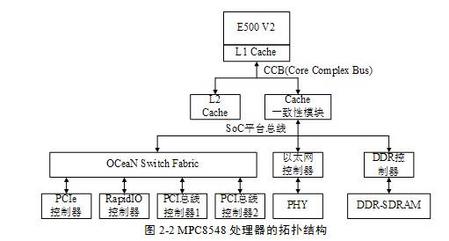

MPC8548处理器是Freescale基于E500 V2内核的一个PowerPC处理器,该处理器中集成了DDR控制器、多个eTSEC(Enhanced Three-Speed Ethernet Controller)、PCI/PCI-X和PCIe总线控制器等一系列接口。MPC8548处理器的拓扑结构如图2‑2所示。

如上图所示,MPC8548处理器的L1 Cache在E500 V2内核中,而L2 Cache与FSB[1]直接相连,不属于E500内核。值得注意的是有些高端PowerPC处理器的L2 Cache也在CPU中,而L3 Cache与CCB总线直接相连。

在MPC8548处理器中,所有外部设备,如以太网控制器、DDR控制器和OCeaN连接的总线控制器都与SoC平台总线[2]直接连接。而SoC平台总线通过Cache共享一致性模块与FSB连接。

在MPC8548处理器中,具有一个32位的PCI总线控制器、一个64位的PCI/PCI-X总线控制器,还有多个PCIe总线控制器。MPC8548处理器使用OCeaN连接这些PCI、PCI-X和PCIe总线控制器。在MPC8548处理器系统中,PCI设备进行DMA操作时,首先通过OCeaN,之后经过SoC平台总线到达DDR控制器。

OCeaN是MPC8548处理器中连接快速外设使用的交叉互连总线,OCeaN不仅可以连接PCI、PCI-X和PCIe总线控制器,而且可以连接RapidIO[3]总线控制器。使用OCeaN进行互连的总线控制器可以直接通信,而不需要通过SoC平台总线。

如来自HOST主桥1的数据报文可以通过OCeaN直接发向HOST主桥2,而不需要将数据通过SoC平台总线,再进行转发,从而减轻了SoC平台总线的负担。OCeaN部件的拓扑结构如图2‑3所示。

在MPC8548处理器中,有两个HOST主桥,分别是HOST主桥1和HOST主桥2,其中HOST主桥1可以支持PCI-X总线,而HOST主桥2只能支持PCI总线。此外该处理器还含有多个PCIe总线控制器。

本节仅介绍HOST主桥,即MPC8548处理器中的PCI总线控制器,而不介绍该处理器的PCIe总线控制器。因为从软件层面上看,MPC8548处理器的PCIe总线控制器与PCI/PCI-X总线控制器功能类似。

MPC8548处理器即可以作为PCI总线的HOST处理器,也可以作为PCI总线的从设备,本节仅讲述MPC8548处理器如何作为PCI总线的HOST处理器管理PCI总线树,而并不关心MPC8548处理器作为从设备的情况。

在MPC8548处理器的HOST主桥中,定义了一系列与系统软件相关的寄存器。本节将通过介绍这些寄存器,说明这个HOST主桥的功能。为节约篇幅,本节仅介绍与HOST主桥1相关的寄存器,HOST主桥2使用的寄存器与HOST主桥1使用的寄存器类似。

PCI总线规定访问配置空间的总线事务,即配置读写总线事务,使用ID号进行寻址。PCI设备的ID号由总线号(Bus Number)、设备号(Device Number)和功能号(Function Number)组成。

其中总线号在HOST主桥遍历PCI总线树时确定。PCI总线可以使用PCI桥扩展PCI总线,并形成一颗PCI总线树。在一颗PCI总线树上,有几个PCI桥(包括HOST主桥),就有几条PCI总线。在一颗PCI总线树中,总线号由系统软件决定,通常与HOST主桥直接相连的PCI总线编号为0,系统软件使用DFS(Depth-First Search)算法扫描PCI总线树上的所有PCI总线,并依次进行编号。

一条PCI总线的设备号由PCI设备的IDSEL信号与PCI总线地址线的连接关系确定,而功能号与PCI设备的具体设计相关。在一个PCI设备中最多有8个功能设备,而且每一个功能设备都有各自的PCI配置空间,而在绝大多数PCI设备中只有一个功能设备。HOST主桥使用寄存器号,访问PCI设备配置空间的某个寄存器。

在MPC8548处理器的HOST主桥中,与PCI设备配置空间相关的寄存器由CFG_ADDR、CFG_DATA和INT_ACK寄存器组成。系统软件使用CFG_ADDR和CFG_DATA寄存器访问PCI设备的配置空间,而使用INT_ACK寄存器访问挂接在PCI总线上的中断控制器的中断向量,这3个寄存器的地址偏移和属性如表2‑1所示。

表2‑1 PCI总线配置寄存器

|

Offset |

寄存器 |

属性 |

复位值 |

|

0x0_8000 |

CFG_ADDR |

可读写 |

0x0000-0000 |

|

0x0_8004 |

CFG_DATA |

可读写 |

0x0000-0000 |

|

0x0_8008 |

INT_ACK |

只读 |

0x0000-0000 |

在MPC8548处理器中,所有内部寄存器都使用存储器映射方式进行寻址,并存放在以BASE_ADDR[4]变量为起始地址的“1MB连续的物理地址空间”中。PowerPC处理器可以通过BASE_ADDR+Offset的方式访问表2‑1中的寄存器。

MPC8548处理器使用CFG_ADDR寄存器和CFG_DATA寄存器访问PCI设备的配置空间,其中用CFG_ADDR寄存器保存PCI设备的ID号和寄存器号,该寄存器的各个字段的详细说明如下所示。

MPC8548处理器访问PCI设备的配置空间时,首先需要在CFG_ADDR寄存器中设置这个PCI设备对应的总线号、设备号、功能号和寄存器号,然后使能Enable位。之后当MPC8548处理器对CFG_DATA寄存器进行读写访问时, HOST主桥将这个存储器读写访问转换为PCI配置读写请求,并发送到PCI总线上。如果Enable位没有使能,处理器对CFG_DATA的访问不过是一个普通的I/O访问,HOST主桥并不能将其转换为PCI配置读写请求。

HOST主桥根据CFG_ADDR寄存器中的ID号,生成PCI配置读写总线事务,并将这个读写总线事务,通过ID译码方式发送到指定的PCI设备。PCI设备将接收来自配置写总线事务的数据,或者为配置读总线事务提供数据。

值得注意的是,在PowerPC处理器中,在CFG_DATA寄存器中保存的数据采用大端方式进行编址,而PCI设备的配置寄存器采用小端编址,因此HOST主桥需要进行端模式转换。我们以源代码2‑1为例说明PowerPC处理器如何访问PCI配置空间。

源代码2‑1 PowerPC处理器访问PCI配置空间

|

stw r0, 0(r1) ld r3, 0(r2) |

我们首先假设寄存器r1的初始值为BASE_ADDR+0x0_8000(即CFG_ADDR寄存器的地址) ,寄存器r0的初始值为0x8000-0008,寄存器r2的初始值为BASE_ADDR+0x0_8004 (即CFG_DATA寄存器的地址),而指定PCI设备(总线号、设备号、功能号都为0)的配置寄存器的0x0B~0x08中的值为0x9988-7766。

这段源代码的执行步骤如下。

(1) 将r0寄存器赋值到r1寄存器所指向的地址空间中,即初始化CFG_ADDR寄存器为0x8000-0008。

(2) 从r2寄存器所指向的地址空间中读取数据到r3寄存器中,即从CFG_DATA寄存器中读取数据到r3寄存器。

在MPC8548处理器中,源代码2‑1执行完毕后,寄存器r3保存的值为0x6677-8899,而不是0x9988-6677。系统程序员在使用这个返回值时,一定要注意大小端模式的转换。值得注意的是,源代码2‑1可以使用lwbrx指令进行优化,该指令可以在读取数据的同时,进行大小端模式的转换。

处理器读取INT_ACK寄存器时,HOST主桥将这个读操作转换为PCI总线中断响应事务。PCI总线中断响应事务的作用是通过PCI总线读取中断控制器的中断向量号,这样做的前提是中断控制器需要连接在PCI总线上。

PowerPC处理器使用的MPIC中断控制器不是挂接在PCI总线上,而是挂接在SoC平台总线上的,因此PCI总线提供的中断应答事务在这个处理器系统中并没有太大用途。但是并不排除某些PowerPC处理器系统使用了挂接在PCI总线上的中断控制器,比如PCI南桥芯片,此时PowerPC处理器系统需要使用中断应答事务读取PCI南桥中的中断控制器,以获取中断向量号。

MPC8548处理器使用ATMU (Address Translation and Mapping Unit)寄存器组进行存储器域到PCI总线域,以及PCI总线域到存储器域的地址映射。ATMU寄存器组由两大组寄存器组成,分别为Outbound和Inbound寄存器组。其中Outbound寄存器组将存储器域的地址转换为PCI总线域的地址,而Inbound寄存器组将PCI总线域的地址转换为存储器域的地址。

在MPC8548处理器中,只有当CPU读写访问的地址范围在Outbound寄存器组管理的地址空间之内时,HOST主桥才能接收CPU的读写访问,并将CPU在存储器域上的读写访问转换为PCI总线域上的读写访问,然后才能对PCI设备进行读写操作。

如图2‑2所示,CPU对存储器域的地址访问,首先使用CCB总线事务,如果所访问的地址在Cache中命中时,则从Cache中直接获得数据,否则将从存储器域中获取数据。而在绝大多数情况下,外部设备使用的地址空间是不可Cache[5]的,所以在绝大多数情况之下,发向PCI设备的CCB总线事务并不会与Cache进行数据交换。

如果CCB总线事务使用的地址在HOST主桥的Outbound寄存器窗口中命中时,HOST主桥将接收这个CCB总线事务,并将其转换为PCI总线事务之后,再发送到PCI总线上。MPC8548处理器的每一个HOST主桥都提供了5个Outbound寄存器窗口来实现存储器域地址到PCI总线域地址的映射,其映射过程如图2‑4所示。

表2‑2 PCI/X ATMU Outbound寄存器组

|

地址偏移 |

寄存器名 |

属性 |

复位值 |

|

0x0_8C00/20/40/60/80 |

POTARn |

可读写 |

0x0000-0000 |

|

0x0_8C04/24/44/64/84 |

POTEARn |

可读写 |

0x0000-0000 |

|

0x0_8C28/48/68/88 |

POWBARn |

可读写 |

0x0000-0000 |

|

0x0_8C30/50/70/90 |

POWARn |

可读写 |

0x0000-0000 |

在POTARn和POTEARn寄存器中保存当前Outbound窗口在PCI总线域中的64位地址空间的基地址。这两个寄存器的主要字段如下。

而POWBARn寄存器保存当前Outbound窗口在存储器域中的36位地址空间的基地址[7] ,其主要字段如下。

[1]MPC8548也将FSB称为CCB(Core Complex Bus)。

[2]PowerPC处理器并没有公开其SoC平台总线的设计规范。ARM提出的AMBA总线是一条典型的SoC平台总线。

[3]RapidIO总线由Mercury Computer System和Motorola Semiconductor(目前的Freescale)共同提出,用于解决背板互连的一条外部总线。

[4]在MPC8548处理器中,BASE_ADDR存放在CCSRBAR寄存器中。

[5]PCI设备使用的ROM空间可以是“可Cache”的地址空间。

[6]POTARn寄存器没有保存PCI总线的11~0位,因为Outbound窗口大小至少为4KB。

[7]MPC8548处理器的物理地址为36位。注意在PowerPC处理器中,第0位是地址的最高位。

/5

/5

文章评论(0条评论)

登录后参与讨论