刚开始接触DSP_Builder工具时可能会对clock模块有些疑惑。Clock模块如下图所示。

![]() ,我来说一下我的疑惑,看大家是否有同感,把clock放在你要设计算法的model中,此外还有一个和clock差不多的东西,那就是

,我来说一下我的疑惑,看大家是否有同感,把clock放在你要设计算法的model中,此外还有一个和clock差不多的东西,那就是![]() ,字面意思倒是好理解,“引出时钟”,这个翻译有些不专业,但意思差不多,那就是由原时钟引出的时钟,那这两个东西连管教都没有,到底怎么用呢?

,字面意思倒是好理解,“引出时钟”,这个翻译有些不专业,但意思差不多,那就是由原时钟引出的时钟,那这两个东西连管教都没有,到底怎么用呢?

首先要说明一点,这两个时钟对于我们综合后的代码来说只是提供了两个接口,而真正引出时钟的含义只是在我们仿真时才是有意义的。怎么理解呢?simulink在仿真我们代码时需要一个统一的时间标准,这个时间标准就是我们的Clock模块,一个程序中标准只有一个,如果我们想设计多时钟程序怎么办,那就只能在原时钟基础上生成;而当我们生成可综合的代码时,这个引出时钟和原时钟就没有任何关系了,我们必须在外部通过逻辑代码或者PLL提供时钟信号,要保证和仿真时的频率关系和相位关系一致。

那这两个时钟连输出端口都没有,我们怎样使用呢?下面笔者给大家讲述一下Altera为什么要这么设计。FPGA设计时主张同步时序设计方法,先看一下同步时序的定义。

看到这个定义大家应该明白了吧,用一个clock模块是对应同一时钟,而是用clock_derived模块是对应多个时钟的情况。那还没有说端口的问题呢?其实这种设计是在帮我们省事,为什么那么说呢?当我们仔细观察各模块的参数就知道了,只有数据源模块才让我们填写参考时钟(如输入口(input)、计数器(counter)等),中间模块根本没有给我们设计参考时钟的机会,这种设计就使我们必须使用同步时序设计方法,且一条数据通道上仅使用一个时钟。

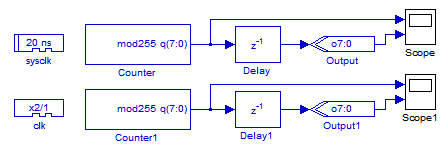

为了印证上述结论,笔者做了一个实验。

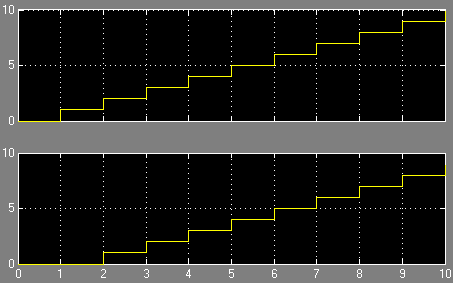

如上图所示,sysclk周期为20ns,clk是sysclk的二分频,counter的参考时钟是sysclk,counter1的参考时钟clk。下面是仿真结果。

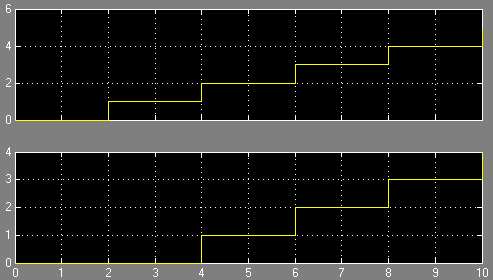

由这两个图可知,笔者的结论是正确的,delay模块的延时是延时的各部分时钟周期。

下面说说笔者为什么要进行这个实验,笔者之前设计了一个小波分解算法。当数据流按照奇偶性分离后,奇数据流和偶数据流的频率都为原频率的1/2,并且需要执行一步计算,那就是当前奇数流数据和前一个奇数流数据求和。在没得到上述结论之前,笔者采用的办法是,把前一个奇数流数据延时2个时钟在和当前数据求和,这中方法可以得到正确的结果,但多用了一组逻辑单元,造成逻辑单元的浪费相当严重。

/1

/1

文章评论(0条评论)

登录后参与讨论