一个好的算法并不只是讲求功能的实现,功能的实现只是前提,而消耗更少的资源(更省钱)提供相同的功能才是王道。本文就给大家说一下笔者整理的一些省钱的方法。

1、 器件的选型。对于Altera公司的FPGA,Cyclone II系列FPGA内部RAM资源只有M4K,Cyclone III是M9K,更高端的芯片可能有M512K,或者几种规格的RAM块都有。那是不是越大越好呢?答案是否定的,相反,RAM类型越高端,其资源使用率就会越低,试想,你使用M512K的RAM块,而你的程序根本用不大那么大资源,剩余的空间将全部浪费。所以在器件选型时,要综合考虑多方面因素。

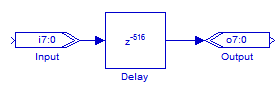

2、 下面我们来看一个具体的例子,通过这个例子我们就能看出来我前两篇博文讲诉的内容有什么作用。先来看两个算法:

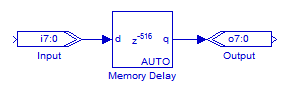

(1)

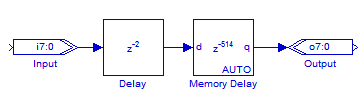

(2)

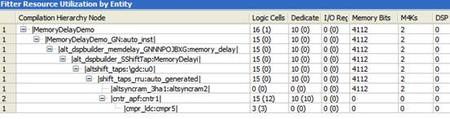

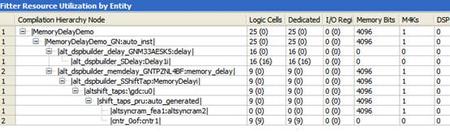

这两个算法在功能上实现的功能相同,都是把一个8位数据延时516个时钟单位,那我们就来对比一下资源消耗情况。对于算法(1),516*8=4128 bits > 4096 bits(4K bits),因此需要消耗两个M4Ks;再来看算法(2),前面两个时钟延时由delay模块完成,消耗16个LE,再延时514个时钟,正好消耗1个M4K。下面两幅图是上述算法综合后资源消耗情况。

那有人会问,我能不能设计成下图的算法,然后通过优化选项让综合器自己决定,通过笔者试验,这种功能Altera还没做到。

对比算法(1)和算法(2),我想我们之前的努力已经有所回报,我们少用了一个M4K,多用了几个LE就实现了所需的功能,何乐而不为呢!

/4

/4

文章评论(0条评论)

登录后参与讨论