上一篇博文我们认识到了Delay模块和Memory Delay模块的区别,但是,貌似我们还有个问题没有明确,认识到它们的区别到底有什么作用呢?笔者先来将一个自己在DSP_Builder算法设计过程中遇到的问题。笔者设计一个小波分解的算法,该算法需要把数据按次序奇偶性分离,还需要对行数据和变换后的数据进行延时,因此需要大量使用delay模块或者memory delay模块,当算法设计完成进行编译时,一个奇怪的事情发生了,memory bits资源只占用了60%左右,但提示memory资源不够。笔者为了揭开上述错误的谜团,才进行了上述博文的实验。

本次我们就来看一下到底为什么会出现上述现象。

我们先来讲述一个FPGA的基础知识。我们知道,对于Cyclone II系列的FPGA,其逻辑单元(LE)是构成FPGA的基本单元之一,一个LE由一个4输入的LUT、一个寄存器及进位和互连逻辑组成。但我们设计一个由少于4个输入端和1个数据输出端组成的电路时,一个LE足矣,但当我们由5个输入端和1个输出端组成电路时,就必须有两个LE构建,但有1个LE没有得到充分利用,其他电路能否再利用这个没有得到充分利用的资源呢,答案是不能。这个也就解释了为什么FPGA逻辑资源不可能达到100%的缘故。

受此影响,我们想,既然剩余的逻辑资源不能被再利用,那未用完的M4K资源能否得到再利用呢,为了说明这一点,我们做个试验,就一目了然了。笔者这个实验所用的芯片是Cyclone II的EP2C8Q208C8,该芯片有8256个LE,以及36个M4Ks资源。我们这个实验是把该芯片上36个M4Ks全部耗尽,但每个都有剩余空间,看还能否再利用。

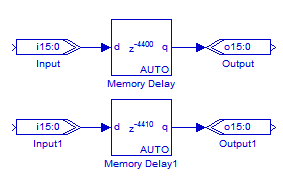

笔者设计了一个算法,如图所示。

这个算法很明显, 36个M4Ks全部消耗完毕,但至少有两个M4Ks资源没有得到充分利用,我们编译完查看资源消耗情况也很清楚。

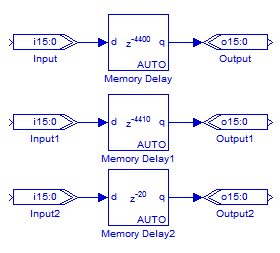

接下来,我们就在上图算法基础上再加一部分,如下图。

看到了吧,笔者意图相当明显,如果能够编译通过,那可以证明,未完全使用的M4Ks可以得到再利用;如果编译失败,要就只能说明,M4Ks如同LE一样,未完全使用的只能被丢弃。

实践证明,编译失败。由此可以说明,一个M4Ks被用过以后,即使有剩余空间,也不能被再利用了。这个结论揭示了笔者在算法设计中遇到的问题,memory资源占用率仅为60%,但确提示没有足够的memory资源。

由这两篇博文也揭示出一个道理:在算法设计过程中,功能的实现是前提,但算法的优化也是必不可少的。

/4

/4

文章评论(0条评论)

登录后参与讨论